浅谈半导体测试过程

制造/封装

描述

测试环节贯穿半导体生产制造,是芯片质量的把关者

半导体工艺制程越来越复杂,检测设备愈发重要。随摩尔定律的进一步发展,半导体芯片 晶体管密度越来越高,相关产品复杂度及集成度呈现指数级增长。新应用需求驱动了制程微缩 和三维结构的升级,使得工艺步骤大幅提升,成熟制程(以 45nm 为例)工艺步骤数大约需要 430 道,到了先进制程(以 5nm 为例)将会提升至 1250 道,工艺步骤将近提升了 3 倍;结构 上来看包括 GAAFET、MRAM 等新一代的半导体工艺都是越来越复杂,在数千道制程中,每一道 制程的检测对芯片的良率起到至关重要的作用。

半导体检测根据使用的环节以及检测项目的不同,可分为前道检测和后道检测。其中,前道量 测包括量测类和缺陷检测类,主要用于晶圆加工环节,目的是检查每一步制造工艺后晶圆产品 的加工参数是否达到设计的要求或者存在影响良率的缺陷,属于物理性检测;后道测试根据功 能的不同包括分选机、测试机、探针台,主要是用在晶圆加工之后、封装测试环节内,目的是 检查芯片的性能是否符合要求,属于电性能检测。晶圆制造环节检测主要进行光学检测,封测环节主要进行电性能检测。半导体测试环节是避 免“十倍成本”的关键。

所谓“十倍成本”是指芯片故障若未在测试环节中发现,那么在 后续电路板级别中发现故障导致的成本将在十倍以上。其中,封测环节主要可以分为:晶 圆测试和成品测试。晶圆测试主要是针对加工完的晶圆,进行电性测试,识别出能够正常工作 的芯片,需要使用的设备主要为测试机和探针台。

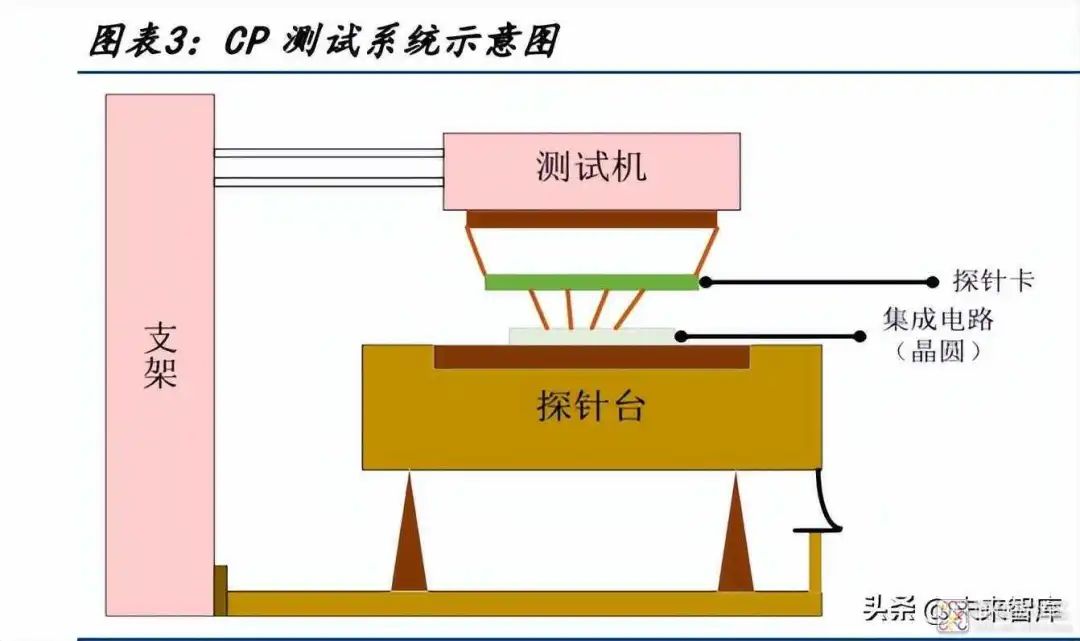

成品测试主要是指晶圆切割变成芯片后,针 对芯片的性能进行最终测试,需要使用的设备主要为测试机和分选机。晶圆测试(Chip Probing),简称 CP 测试,是指通过探针台和测试机的配合使用,对晶圆 上的裸芯片(gross die)进行功能和电学性能参数的测试。

测试过程主要为:探针台将 晶圆逐片传送至测试位置,芯片端点通过探针、专用连接线与测试机的功能模块进行连接, 测试机对芯片施加输入信号并采集输出信号,以判断芯片功能和性能是否达到设计规范要 求。对裸片的测试结果通过通信接口传送至探针台,探针台会根据相应的信息对芯片进行 打点标记,形成晶圆的 Mapping,即晶圆的电性能测试结果。CP 测试设备主要由支架、测 试机、探针台、探针卡等部件组成。CP 测试会统计出晶圆上的芯片合格率、不合格芯片 的确切位置和各类形式的良率等,可用于指导芯片设计和晶圆制造的工艺改进。

芯片成品测试(Final Test),简称 FT,FT 测试是在芯片封装后按照测试规范对电路成品 进行全面的电路性能检测,目的是挑选出合格的成品芯片,保障芯片在任何环境下都可以 维持设计规格书上所预期的功能及性能。通过分选机和测试机配合使用,测试过程主要为:分选机将被测芯片逐个传送至测试工位,被测芯片的引脚通过测试工位上的基座、专用连 接线与测试机的功能模块进行连接,测试机对芯片施加输入信号并采集输出信号,判断芯 片功能和性能是否达到设计规范要求。测试结果通过通信接口传送至分选机,分选机据此 对被测芯片进行标记、分选、收料或编带。

FT 测试系统通常由支架、测试机、分选机、 测试板和测试座组成。FT 测试环节的数据可以用于指导封装环节的工艺改进。CP 测试的主要目的在于挑出坏的裸片,减少后续的封装和 FT 测试成本;FT 测试的主要目 的确保芯片符合交付要求,避免将不合格的芯片交付给下游用户。相比于 FT 测试,CP 测 试的技术要求更高,难度更大。芯片在完成封装后处于良好的保护状态,体积也较晶圆状 态的裸片增加几倍至数十倍,因此 FT 测试对洁净等级和作业精细程度的要求较 CP 测试低 一个级别,但测试作业的工作量和人员用工量更大。CP 测试和 FT 测试在确保芯片良率、 控制生产成本、指导 IC 设计和生产工艺改进等方面都起到了至关重要的作用。

编辑:黄飞

- 相关推荐

- 热点推荐

- 半导体测试

-

半导体测试解决方案2019-07-29 2849

-

TDR测试过程静电危害及其预防2011-12-16 4391

-

IC半导体封装测试流程2016-05-26 1984

-

压力传感器测试过程的可靠性概念概述[图]2018-01-18 4431

-

半导体测试愈发重要,如何进行半导体测试?2019-04-11 16806

-

锂离子电池测试过程的误差分析2019-12-02 7493

-

半导体测试—优质好文推荐2020-10-30 2104

-

渗透测试过程中所使用的抓包方法2023-02-01 2920

-

防静电ESD测试过程展示2021-09-30 3245

-

ATA-5620前置微小信号放大器如何进行半导体测试2023-10-07 1229

-

半导体静态测试参数是什么?纳米软件半导体参数分析系统能否满足测试指标?2023-10-10 2153

-

如何解决车载部品测试过程中峰值电流不足的问题?2023-11-23 1327

-

ATA-5420前置微小信号放大器如何进行半导体测试2024-07-09 994

-

半导体在热测试中遇到的问题2025-01-06 1984

-

宏展科技北京浅谈JEDEC半导体可靠度测试与规范2026-02-02 345

全部0条评论

快来发表一下你的评论吧 !