з”ЁдәҺ SiC MOSFET зҡ„йҡ”зҰ»ж …жһҒй©ұеҠЁеҷЁдҪҝз”ЁжҢҮеҚ—

жҸҸиҝ°

зӮ№еҮ»и“қеӯ—В е…іжіЁжҲ‘们

В В В В В В ВВ

SiC MOSFET еңЁеҠҹзҺҮеҚҠеҜјдҪ“еёӮеңәдёӯжӯЈиҝ…йҖҹжҷ®еҸҠпјҢеӣ дёәе®ғжңҖеҲқзҡ„дёҖдәӣеҸҜйқ жҖ§й—®йўҳе·Іеҫ—еҲ°и§ЈеҶіпјҢ并且价дҪҚе·ІиҫҫеҲ°йқһеёёжңүеҗёеј•еҠӣзҡ„ж°ҙе№ігҖӮйҡҸзқҖеёӮеңәдёҠзҡ„еҷЁд»¶и¶ҠжқҘи¶ҠеӨҡпјҢеҝ…йЎ»дәҶи§Ј SiC MOSFET дёҺ IGBT д№Ӣй—ҙзҡ„е…ұжҖ§е’Ңе·®ејӮпјҢд»Ҙдҫҝз”ЁжҲ·е……еҲҶеҲ©з”ЁжҜҸз§ҚеҷЁд»¶гҖӮжң¬зі»еҲ—ж–Үз« жҰӮиҝ°дәҶе®үжЈ®зҫҺ M 1 1200 V SiC MOSFET зҡ„е…ій”®зү№жҖ§еҸҠй©ұеҠЁжқЎд»¶еҜ№е®ғзҡ„еҪұе“ҚпјҢдҪңдёәе®үжЈ®зҫҺжҸҗдҫӣзҡ„е…Ёж–№дҪҚе®ҪзҰҒеёҰз”ҹжҖҒзі»з»ҹзҡ„дёҖйғЁеҲҶпјҢиҝҳе°ҶжҸҗдҫӣВ NCP51705пјҲз”ЁдәҺ SiC MOSFET зҡ„йҡ”зҰ»ж …жһҒй©ұеҠЁеҷЁпјүзҡ„дҪҝз”ЁжҢҮеҚ—гҖӮжң¬ж–Үдёә第дёүйғЁеҲҶпјҢе°ҶйҮҚзӮ№д»Ӣз»ҚNCP51705 SiC ж …жһҒй©ұеҠЁеҷЁзҡ„дҪҝз”ЁжҢҮеҚ—гҖӮ

зӣёе…іж–Үз« жҺЁиҚҗйҳ…иҜ» В е®үжЈ®зҫҺ M 1 1200 V SiC MOSFET йқҷжҖҒзү№жҖ§еҲҶжһҗ В е®үжЈ®зҫҺ M 1 1200 V SiC MOSFET еҠЁжҖҒзү№жҖ§еҲҶжһҗеҺҹзүҲж–ҮжЎЈиҺ·еҸ–зӮ№еҮ»ж–Үжң«зҡ„вҖңиөһвҖқе’ҢвҖңеңЁзңӢвҖқпјҢ并еҸ‘йҖҒжҲӘеӣҫе’ҢжӮЁзҡ„йӮ®з®ұең°еқҖеҲ°еҗҺеҸ°пјҢеҚіеҸҜйўҶеҸ–еҺҹзүҲж–ҮжЎЈе“Ұ~

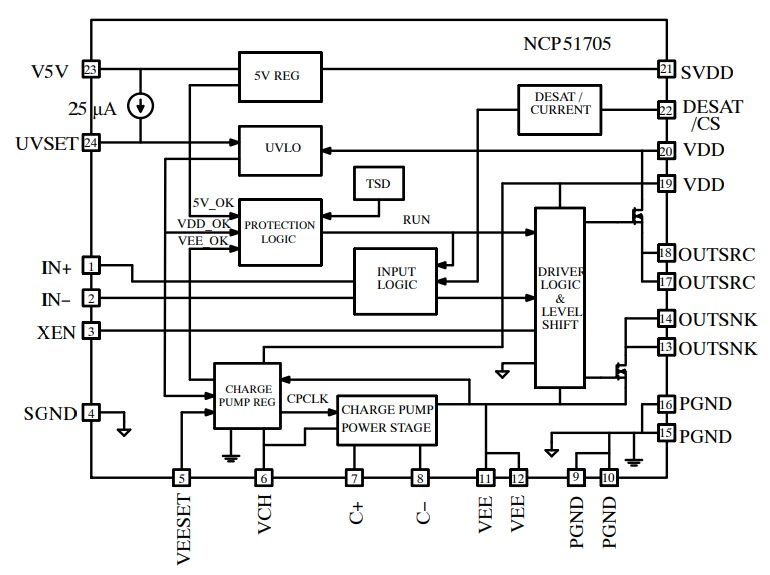

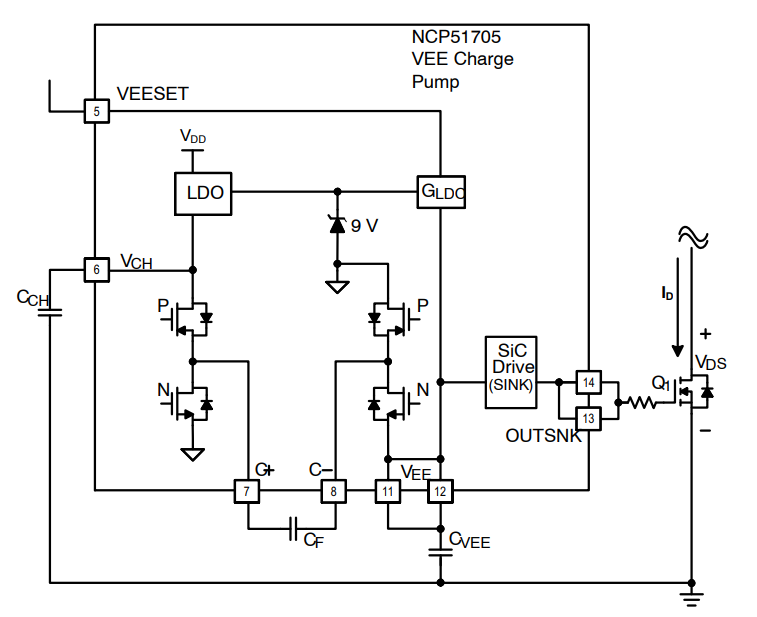

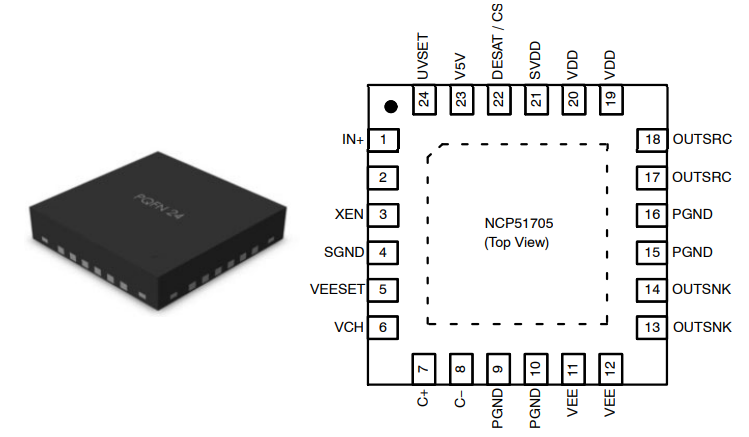

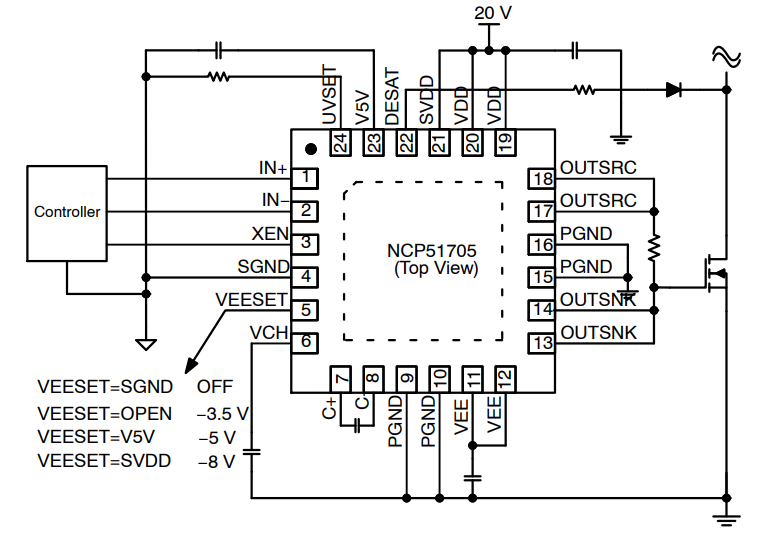

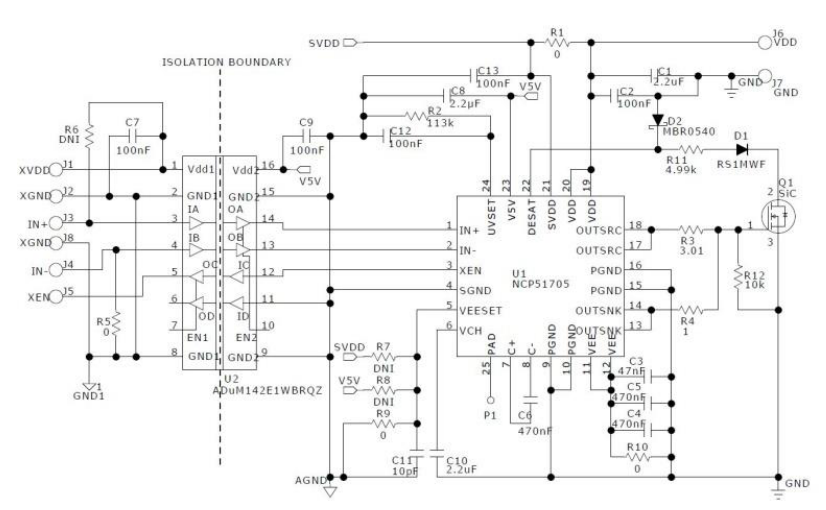

В В ВNCP51705 жҳҜдёҖз§Қ SiC ж …жһҒй©ұеҠЁеҷЁпјҢе…·жңүй«ҳеәҰзҡ„зҒөжҙ»жҖ§е’ҢйӣҶжҲҗжҖ§пјҢдҪҝе…¶дёҺеёӮеңәдёҠзҡ„д»»дҪ• SiC MOSFET е®Ңе…Ёе…је®№гҖӮеҰӮеӣҫ 32 жүҖзӨәпјҢNCP51705 йЎ¶еұӮжЎҶеӣҫеҢ…жӢ¬йҖҡз”Ёж …жһҒй©ұеҠЁеҷЁеёёи§Ғзҡ„и®ёеӨҡеҹәжң¬еҠҹиғҪпјҢеҢ…жӢ¬пјҡ

1.В й«ҳиҫҫ 28 V зҡ„ VDD жӯЈз”өжәҗз”өеҺӢ

2.В й«ҳеі°еҖјиҫ“еҮәз”өжөҒпјҲ6 A жәҗжһҒе’Ң 10 A жјҸжһҒпјү

3.В еҶ…йғЁ 5 V еҸӮиҖғз”өеҺӢеҸҜз”ЁдәҺеҒҸзҪ® 5 VгҖҒй«ҳиҫҫ 20 mA зҡ„дҪҺеҠҹзҺҮиҙҹиҪҪпјҲж•°еӯ—йҡ”зҰ»еҷЁгҖҒе…үиҖҰеҗҲеҷЁгҖҒОјC зӯүпјү

4. еҲҶзҰ»дҝЎеҸ·пјҢз”өжәҗжҺҘең°

5. еҲҶзҰ»жәҗжһҒе’ҢжјҸжһҒиҫ“еҮәеј•и„ҡ

6.В еҶ…йғЁзғӯе…іж–ӯдҝқжҠӨ

7.В еҲҶзҰ»йқһеҸҚзӣёе’ҢеҸҚзӣё TTLгҖҒPWM иҫ“е…Ҙ

еӣҫ 32пјҡNCP51705 SiC ж …жһҒй©ұеҠЁеҷЁжЎҶеӣҫ

В

жӯӨеӨ–пјҢNCP51705 е…·еӨҮдҪҝз”ЁжңҖе°‘зҡ„еӨ–йғЁз»„件и®ҫи®ЎеҸҜйқ зҡ„ SiC MOSFET ж …жһҒй©ұеҠЁз”өи·ҜжүҖеҝ…йңҖзҡ„еҮ дёӘзӢ¬зү№зү№жҖ§пјҲеңЁ TND6237/D дёӯзҡ„еҲҶз«Ӣ SIC ж …жһҒй©ұеҠЁйғЁеҲҶзҡ„ејҖеӨҙеҲ—еҮәпјүгҖӮNCP51705 зӢ¬зү№зү№жҖ§зҡ„дјҳзӮ№е°ҶеңЁдёӢдёҖиҠӮиҜҰз»Ҷд»Ӣз»ҚгҖӮ

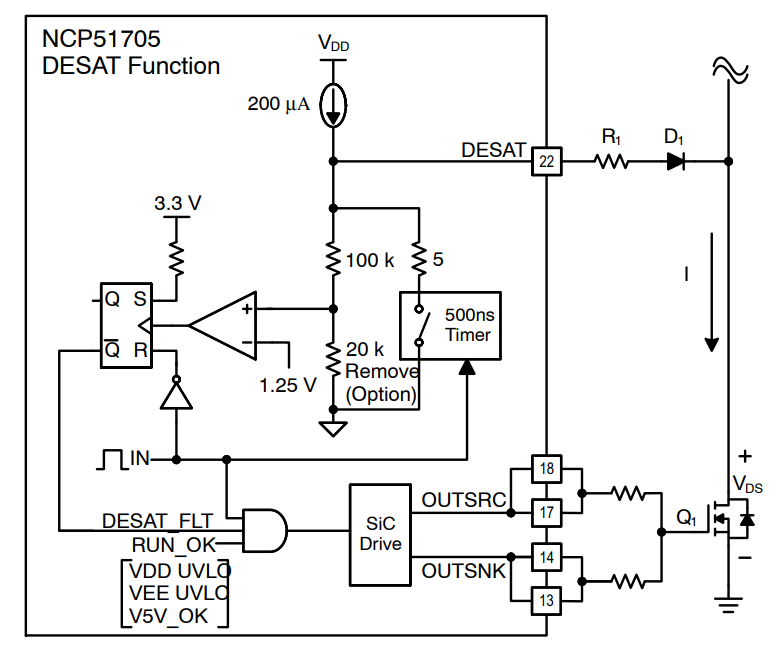

В иҝҮз”өжөҒдҝқжҠӨ вҲ’ DESATNCP51705 DESAT еҠҹиғҪзҡ„е®һзҺ°еҸӘйңҖдҪҝз”ЁдёӨдёӘеӨ–йғЁз»„件гҖӮеҰӮеӣҫ 33 жүҖзӨәпјҢйҖҡиҝҮ DESAT еј•и„ҡзҡ„ R1 е’Ң D1 зӣ‘жөӢ SiC MOSFET, Q1 зҡ„жјҸжһҒ-жәҗжһҒз”өеҺӢгҖӮ

еӣҫ 33пјҡNCP51705 DESAT еҠҹиғҪ

В

еңЁ Q1 е…іж–ӯжңҹй—ҙпјҢжјҸжһҒ-жәҗжһҒз«ҜеӯҗеҸҜиғҪеҮәзҺ°еҮ зҷҫдјҸз”өеҺӢгҖӮдёҖж—Ұ Q1 еҜјйҖҡпјҢжјҸжһҒ-жәҗжһҒз”өеҺӢиҝ…йҖҹдёӢйҷҚпјҢйў„и®ЎеңЁдёҚеҲ°еҮ зҷҫзәіз§’зҡ„ж—¶й—ҙеҶ…е°ұдјҡеҸ‘з”ҹд»Һй«ҳз”өеҺӢеҲ°жҺҘиҝ‘йӣ¶з”өеҺӢзҡ„иҪ¬еҸҳгҖӮеңЁеҜјйҖҡиҪ¬жҚўжңҹй—ҙпјҢDESAT дҝЎеҸ·еүҚжІҝиў«дёҖдёӘ 500 зәіз§’и®Ўж—¶еҷЁж¶ҲйҡҗпјҢиҜҘи®Ўж—¶еҷЁз”ұдёҖдёӘ 5вҲ’О© зҡ„дҪҺйҳ»жҠ—дёӢжӢүз”өйҳ»з»„жҲҗгҖӮиҝҷдҪҝ VDS жңүи¶іеӨҹзҡ„ж—¶й—ҙдёӢйҷҚпјҢеҗҢж—¶зЎ®дҝқ DESAT дёҚдјҡж„ҸеӨ–жҝҖжҙ»гҖӮ500 зәіз§’иҝҮеҗҺпјҢDESAT еј•и„ҡиў«йҮҠж”ҫпјҢ200вҲ’ОјA з”өжөҒжәҗйҖҡиҝҮ R1гҖҒD1е’Ң SiC MOSFET еҜјйҖҡз”өйҳ»жҸҗдҫӣжҒ’е®ҡз”өжөҒгҖӮеңЁеҜјйҖҡж—¶й—ҙеҶ…пјҢеҰӮжһң DESAT еј•и„ҡдёҠеҚҮеҲ° 7.5 V д»ҘдёҠпјҢеҲҷ DESAT жҜ”иҫғеҷЁиҫ“еҮәдјҡеҚҮй«ҳпјҢд»ҺиҖҢи§ҰеҸ‘ RS й”ҒеӯҳеҷЁзҡ„ж—¶й’ҹиҫ“е…ҘгҖӮиҝҷз§Қж•…йҡңе°ҶйҖҗдёӘе‘ЁжңҹиҮӘеҠЁз»Ҳжӯў Q_NOT иҫ“еҮәзҡ„еҗҺжІҝгҖӮSiC MOSFET зҡ„ж …жһҒй©ұеҠЁеӣ жӯӨжңүж•Ҳең°еҮҸе°‘дәҶдёҺеҺ»йҘұе’Ңж•…йҡңж—¶й—ҙжҲҗжҜ”дҫӢзҡ„ж—¶й—ҙйҮҸгҖӮ

В200вҲ’ОјA з”өжөҒжәҗи¶ід»ҘзЎ®дҝқ D1 зҡ„еҸҜйў„жөӢжӯЈеҗ‘еҺӢйҷҚпјҢеҗҢж—¶д№ҹдҪҝ R1 зҡ„еҺӢйҷҚиғҪеӨҹеңЁ SiC MOSFET еҜјйҖҡжңҹй—ҙзӢ¬з«ӢдәҺ VDSгҖӮеҰӮжһңйңҖиҰҒпјҢеҸҜйҖҡиҝҮе°Ҷ DESAT еј•и„ҡжҺҘең°жқҘзҰҒз”Ё DESAT дҝқжҠӨгҖӮзӣёеҸҚпјҢеҰӮжһң DESAT еј•и„ҡеӨ„дәҺжө®еҠЁзҠ¶жҖҒпјҢжҲ–иҖ… R1 ж— жі•жү“ејҖпјҢеҲҷжөҒз»Ҹ 20вҲ’kО© з”өйҳ»еҷЁзҡ„ 200вҲ’ОјA з”өжөҒжәҗеңЁ DESAT жҜ”иҫғеҷЁзҡ„йқһеҸҚзӣёиҫ“е…Ҙз«Ҝж–ҪеҠ жҒ’е®ҡзҡ„ 4 V з”өеҺӢгҖӮиҝҷз§Қжғ…еҶөеҹәжң¬дёҠзҰҒз”ЁдәҶ SiC MOSFET зҡ„ж …жһҒй©ұеҠЁгҖӮдёҖдәӣеә”з”ЁеҸҜиғҪеҖҫеҗ‘дәҺдҪҝз”Ёз”өжөҒжЈҖжөӢеҸҳеҺӢеҷЁжқҘжЈҖжөӢжјҸжһҒз”өжөҒпјҢ并д»ҺеӨ–йғЁй©ұеҠЁ DESAT еј•и„ҡгҖӮеңЁиҝҷз§Қжғ…еҶөдёӢпјҢNCP51705 еҢ…жӢ¬дёҖдёӘ IC йҮ‘еұһйҖү件пјҢз”ЁдәҺ移йҷӨ 20вҲ’kО© з”өйҳ»еҷЁпјҢдҪҝ DESAT еј•и„ҡеҸҜд»Ҙз”ЁдҪңдј з»ҹзҡ„йҖҗи„үеҶІгҖҒиҝҮз”өжөҒдҝқжҠӨеҠҹиғҪгҖӮ

В

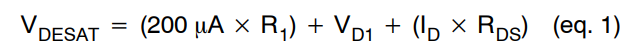

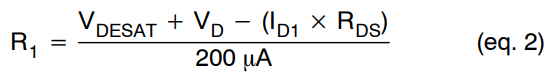

DESAT еј•и„ҡдёҠзҡ„з”өеҺӢ VDESAT з”ұе…¬ејҸпјҲ1пјүзЎ®е®ҡдёәпјҡ

дёә ID еҲҶй…ҚжңҖеӨ§еҖјпјҲз•ҷеҮәйўқеӨ–зҡ„и®ҫи®ЎиЈ•еәҰпјүеҗҺпјҢйҖүжӢ© R1 е’Ң IDпјҢдҪҝ VDESAT < 7.5 VгҖӮйҮҚж–°жҺ’еҲ—е…¬ејҸпјҲ1пјү并жұӮи§Ј R1 еҫ—еҮәпјҡ

йҷӨдәҶи®ҫзҪ®е…Ғи®ёзҡ„жңҖеӨ§ VDESAT з”өеҺӢеӨ–пјҢR1 иҝҳе…·жңүйҷҗеҲ¶йҖҡиҝҮ D1 з»“з”өе®№зҡ„зһ¬ж—¶з”өжөҒзҡ„еҸҢйҮҚзӣ®зҡ„гҖӮеӣ дёә SiC MOSFET дёҠзҡ„жјҸз”өеҺӢ dV/dt жһҒй«ҳпјҢеҰӮжһң R1 зҡ„еӨ§е°ҸдёҚеҗҲйҖӮпјҢйҖҡиҝҮ D1 зҡ„ pвҲ’n з»“з”өе®№зҡ„з”өжөҒеҸҜиғҪдјҡеҸҳеҫ—йқһеёёй«ҳгҖӮеӣ жӯӨпјҢеә”дјҳе…ҲйҖүжӢ©е…·жңүжңҖдҪҺз»“з”өе®№зҡ„еҝ«йҖҹй«ҳеҺӢдәҢжһҒз®ЎгҖӮR1 зҡ„е…ёеһӢеҖје°ҶжҺҘиҝ‘ 5 kО©< R1 < 10 kО© зҡ„иҢғеӣҙпјҢдҪҶиҝҷдјҡж №жҚ®жүҖйҖү SiC MOSFET зҡ„ ID е’Ң RDS еҸӮж•°иҖҢеҸ‘з”ҹеҸҳеҢ–гҖӮеҰӮжһң R1иҝңе°ҸдәҺ 5 kО©пјҢиҝӣе…Ҙ DESAT еј•и„ҡзҡ„зһ¬ж—¶з”өжөҒеҸҜиғҪдёәж•°зҷҫжҜ«е®үгҖӮзӣёеҸҚпјҢеҰӮжһң R1 иҝңеӨ§дәҺ 10 kО©пјҢеҲҷ RC 延иҝҹдёә R1 е’Ң D1з»“з”өе®№зҡ„д№ҳз§ҜгҖӮ延иҝҹеҸҜдёә 100 Ојs йҮҸзә§пјҢд»ҺиҖҢеҜјиҮҙеә”еҜ№ DESAT ж•…йҡңзҡ„йўқеӨ–延иҝҹж—¶й—ҙгҖӮ

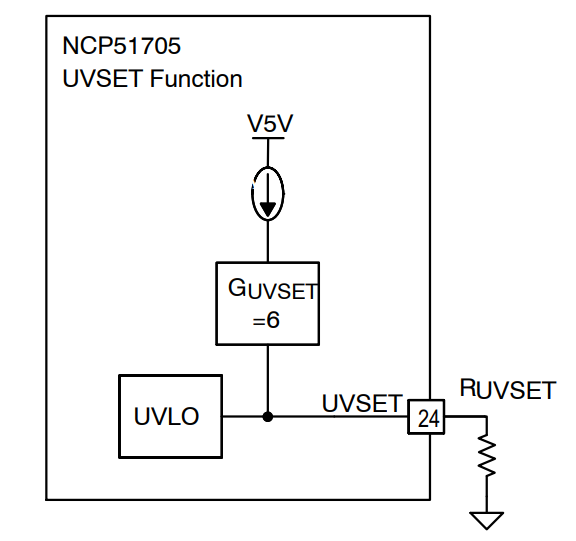

В е……з”өжіө вҖ“ VEE (VEESET)NCP51705 дҪҝз”ЁеҚ•дёҖзҡ„жӯЈз”өжәҗз”өеҺӢиҝҗиЎҢгҖӮд»ҺеҚ•дёҖ VDD з”өжәҗз”өеҺӢиҝҗиЎҢж„Ҹе‘ізқҖеҝ…йЎ»д»Һж …жһҒй©ұеҠЁеҷЁ IC дә§з”ҹиҙҹ VEE з”өеҺӢгҖӮдҪҝз”ЁејҖе…із”өе®№е……з”өжіөжҳҜдә§з”ҹжүҖйңҖиҙҹ VEE з”өеҺӢиҪЁзҡ„еҝ…然йҖүжӢ©гҖӮжһ„е»әе……з”өжіөжңүи®ёеӨҡдёҚеҗҢзҡ„йҖүжӢ©гҖӮдё»иҰҒжҢ‘жҲҳжҳҜеңЁзһ¬жҖҒжқЎд»¶дёӢдҝқжҢҒеҮҶзЎ®зҡ„з”өеҺӢи°ғиҠӮпјҢд»ҘдёҖе®ҡзҡ„йў‘зҺҮејҖе…ід»ҘеҮҸе°Ҹз”өе®№пјҢ并жңҖеӨ§йҷҗеәҰең°еҮҸе°‘еӨ–йғЁз»„件数йҮҸпјҢд»ҺиҖҢйҷҚдҪҺжҲҗжң¬е№¶жҸҗй«ҳеҸҜйқ жҖ§гҖӮ

В

д»Һеӣҫ 34 жүҖзӨәзҡ„е……з”өжіөеҠҹиғҪжЎҶеӣҫеҸҜд»ҘзңӢеҮәпјҢеҸӘйңҖдёүдёӘеӨ–йғЁз”өе®№еҚіеҸҜе»әз«Ӣиҙҹ VEE з”өеҺӢиҪЁгҖӮе……з”өжіөеҠҹзҺҮзә§еҹәжң¬дёҠз”ұдёӨдёӘ PMOS ејҖе…іе’ҢдёӨдёӘ NMOS ејҖе…із»„жҲҗпјҢиҝҷдәӣејҖе…ід»ҘжЎҘејҸз»“жһ„жҺ’еҲ—гҖӮ

еӣҫ 34пјҡNCP51705 VEE е……з”өжіө

ВеҰӮеӣҫжүҖзӨәпјҢеӨ–йғЁйЈһи·Ёз”өе®№ CF иҝһжҺҘеңЁжЎҘзҡ„жҜҸдёӘж”Ҝи·Ҝзҡ„дёӯзӮ№д№Ӣй—ҙгҖӮејҖе…іж—¶еәҸпјҢжҜҸеҪ“дёӨдёӘдёҠйғЁ PMOS еҷЁд»¶еҗҢж—¶еҜјйҖҡж—¶пјҢCF дјҡеҮәзҺ° VDDгҖӮеҗҢж ·пјҢжҜҸеҪ“дёӨдёӘдёӢйғЁ NMOS еҷЁд»¶еҗҢж—¶еҜјйҖҡж—¶пјҢCF дјҡеҮәзҺ° вҲ’VEEгҖӮејҖе…ійў‘зҺҮеңЁеҶ…йғЁи®ҫзҪ®дёә 390 kHzпјҢдёӨдёӘдёҠйғЁ PMOS еҷЁд»¶дёҺдёӨдёӘдёӢйғЁ NMOS еҷЁд»¶ејӮжӯҘеҲҮжҚўгҖӮ290 kHz зҡ„ IC йҮ‘еұһйҖү件д№ҹеҸҜз”ЁдәҺйңҖиҰҒиҫғдҪҺе……з”өжіөејҖе…ійў‘зҺҮзҡ„еә”з”ЁгҖӮ

ВVEE иў«и°ғиҠӮеҲ°еңЁ VCHи®ҫзҪ®зҡ„з”өеҺӢпјҢиҜҘз”өеҺӢз”ұ VEESET еҸҜзј–зЁӢзҡ„еҶ…йғЁдҪҺеҺӢйҷҚзЁіеҺӢеҷЁ (LDO) з”өеҺӢеҶіе®ҡгҖӮVEESET дёҠзҡ„з”өеҺӢдјҡж”№еҸҳеҶ…йғЁ LDO зңӢеҲ°зҡ„еўһзӣҠ (GLDO)гҖӮеҰӮжһң VEESET дҝқжҢҒжө®еҠЁзҠ¶жҖҒпјҲе»әи®®дҪҝз”Ёд»Һ VEESET еҲ° SGND зҡ„ 100вҲ’pF ж—Ғи·Ҝз”өе®№пјүпјҢеҲҷ VEE и®ҫзҪ®дёәеңЁ вҲ’3 V дёӢи°ғиҠӮгҖӮеҜ№дәҺ вҲ’5вҲ’V VEE з”өеҺӢпјҢVEESET еј•и„ҡеә”зӣҙжҺҘиҝһжҺҘеҲ° V5VпјҲеј•и„ҡ 23пјүгҖӮеҰӮжһң VEESET иҝһжҺҘеҲ° 9 V е’Ң VDD д№Ӣй—ҙзҡ„д»»дҪ•з”өеҺӢпјҢеҲҷ VEE иў«з®қдҪҚ并и®ҫзҪ®дёәд»Ҙ вҲ’8 V зҡ„жңҖе°Ҹе……з”өжіөз”өеҺӢиҝӣиЎҢи°ғиҠӮгҖӮеҪ“ VDD > 7.5 V ж—¶пјҢе……з”өжіөеҗҜеҠЁпјҢVEE з”өеҺӢиҪЁеҢ…жӢ¬дёҖдёӘеҶ…йғЁеӣәе®ҡзҡ„ UVLOпјҢи®ҫзҪ®дёәзј–зЁӢ VEE еҖјзҡ„ 80%гҖӮз”ұдәҺ VDD е’Ң VEE еқҮз”ұзӢ¬з«Ӣзҡ„ UVLO з”өи·Ҝзӣ‘жҺ§пјҢNCP51705 и¶іеӨҹжҷәиғҪпјҢеҸҜд»ҘеңЁдёӨдёӘз”өеҺӢиҪЁйғҪеңЁзү№е®ҡ SiC MOSFET иҙҹиҪҪзҡ„е®үе…ЁиҢғеӣҙеҶ…ж—¶е®һзҺ°гҖӮ

В

жҲ–иҖ…пјҢйҖҡиҝҮе®Ңе…ЁзҰҒз”Ёе……з”өжіөпјҢеҸҜд»Ҙе®һзҺ° 0 V < OUT < VDD ејҖе…ігҖӮеҪ“ VEESET иҝһжҺҘеҲ° SGND ж—¶пјҢе……з”өжіөиў«зҰҒз”ЁгҖӮеҪ“е……з”өжіөиў«зҰҒз”Ёдё” VEE зӣҙжҺҘдёҺ PGND зӣёе…іиҒ”ж—¶пјҢиҫ“еҮәеңЁ 0 V < OUT < VDD д№Ӣй—ҙеҲҮжҚўгҖӮйңҖиҰҒжіЁж„Ҹзҡ„жҳҜпјҢжҜҸеҪ“ VEESET дёҺ SGND зӣёе…іиҒ”ж—¶пјҢVEE еҝ…йЎ»дёҺ PGND зӣёе…іиҒ”гҖӮеңЁжӯӨе·ҘдҪңжЁЎејҸжңҹй—ҙпјҢеҶ…йғЁ VEE UVLO еҠҹиғҪд№ҹзӣёеә”зҰҒз”ЁгҖӮ

ВеҸҰдёҖз§ҚеҸҜиғҪзҡ„й…ҚзҪ®жҳҜзҰҒз”Ёе……з”өжіөпјҢдҪҶе…Ғи®ёдҪҝз”ЁеӨ–йғЁиҙҹ VEE з”өеҺӢиҪЁгҖӮжӯӨйҖүйЎ№е…Ғи®ё вҖ“VEE < OUT < VDD еҲҮжҚўпјҢеӣ дёәе……з”өжіөжңӘеҲҮжҚўпјҢжүҖд»ҘеңЁ IC еҠҹиҖ—ж–№йқўз•ҘжңүиҠӮзңҒгҖӮеҪ“ VEESET иҝһжҺҘеҲ° SGND ж—¶пјҢеӨ–йғЁиҙҹз”өеҺӢиҪЁеҸҜд»ҘзӣҙжҺҘеңЁ VEEе’Ң PGND д№Ӣй—ҙиҝһжҺҘгҖӮиҜ·жіЁж„ҸпјҢз”ұдәҺ VEESET дёә 0 VпјҢеҶ…йғЁ VEE UVLO иў«зҰҒз”ЁпјҢеӣ жӯӨ NCP51705 дёҚзҹҘйҒ“ VEE з”өеҺӢж°ҙе№іжҳҜеҗҰеңЁйў„жңҹиҢғеӣҙеҶ…гҖӮ

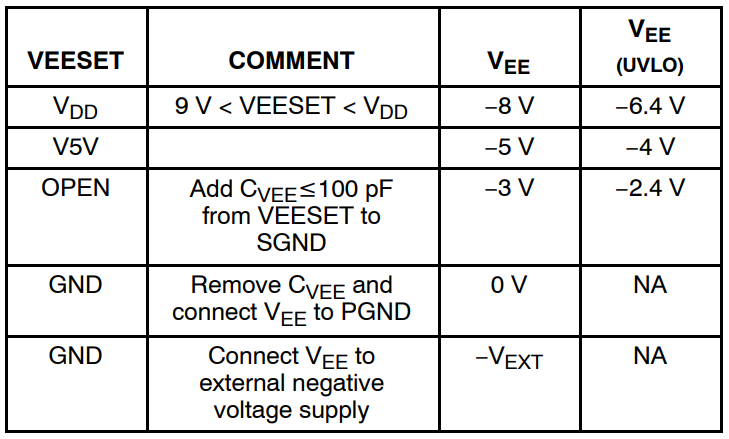

Виҝҷз§Қз®ҖеҚ•зҡ„ VEESET и°ғж•ҙиғҪеӨҹдҪҝз”ЁжңҖе°‘зҡ„еӨ–йғЁз»„件е®һзҺ°жңҖй«ҳзЁӢеәҰзҡ„зҒөжҙ»жҖ§пјҢеҗҢж—¶ж»Ўи¶іжңҖе№ҝжіӣзҡ„ SiC MOSFET з”өеҺӢиҰҒжұӮгҖӮдёәдәҶж–№дҫҝиө·и§ҒпјҢиЎЁ 2 дёӯжҖ»з»“дәҶ VEESET зҡ„еҸҜй…ҚзҪ®жҖ§гҖӮ

В

иЎЁ 2пјҡеҚҠеҜјдҪ“жқҗж–ҷеұһжҖ§

з”ЁдәҺж …жһҒй©ұеҠЁеҷЁ IC зҡ„ UVLO еҜ№дәҺдҝқжҠӨ MOSFET иҮіе…ійҮҚиҰҒпјҢе…¶е·ҘдҪңеҺҹзҗҶжҳҜзҰҒз”Ёиҫ“еҮәпјҢзӣҙеҲ° VDDй«ҳдәҺе·ІзҹҘйҳҲеҖјгҖӮиҝҷдёҚд»…еҸҜд»ҘдҝқжҠӨиҙҹиҪҪпјҢиҖҢдё”еҸҜд»Ҙеҗ‘жҺ§еҲ¶еҷЁйӘҢиҜҒж–ҪеҠ зҡ„ VDDз”өеҺӢй«ҳдәҺеҜјйҖҡйҳҲеҖјгҖӮз”ұдәҺдёҺ SiC MOSFET зӣёе…ізҡ„дҪҺ gmеҖјпјҢжңҖдҪі UVLO еҜјйҖҡйҳҲеҖје№¶йқһвҖңдёҖеҲҖеҲҮвҖқгҖӮеҰӮжһңе…Ғи®ёй©ұеҠЁеҷЁиҫ“еҮәеңЁиҫғдҪҺзҡ„ VDD дёӢеҲҮжҚўпјҢеҸҜиғҪеҜ№жҹҗдёӘ SiC MOSFET дёҚеҲ©пјҢдҪҶж №жҚ®ж•ЈзғӯгҖҒеҶ·еҚҙе’Ң VDD еҗҜеҠЁж—¶й—ҙпјҢеҜ№еҸҰдёҖдёӘ SiC MOSFET иҖҢиЁҖеҸҜиғҪжҳҜеҸҜжҺҘеҸ—зҡ„гҖӮжңҖдҪі UVLO еҜјйҖҡйҳҲеҖјд№ҹдјҡж №жҚ® VDD з”өеҺӢиҪЁзҡ„еҜјеҮәж–№ејҸиҖҢеҸ‘з”ҹеҸҳеҢ–гҖӮдёҖдәӣз”өжәҗзі»з»ҹеҸҜиғҪжңүдёҖдёӘдё“з”Ёзҡ„еҒҸеҺӢз”өжәҗпјҢиҖҢе…¶д»–зі»з»ҹеҲҷеҸҜиғҪдҫқиө–дәҺзұ»дјјдәҺеӣҫ 36 зҡ„ VDD иҮӘдёҫжҠҖжңҜгҖӮ

В

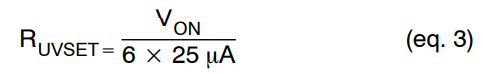

NCP51705 йҖҡиҝҮеҸҜзј–зЁӢ UVLO еҜјйҖҡйҳҲеҖји§ЈеҶідәҶиҝҷдёҖйңҖжұӮпјҢиҜҘйҳҲеҖјеҸҜйҖҡиҝҮ UVSET е’Ң SGND д№Ӣй—ҙзҡ„еҚ•дёҖз”өйҳ»еҷЁи®ҫзҪ®гҖӮеҰӮеӣҫ 35 жүҖзӨәпјҢUVSET еј•и„ҡз”ұ 25вҲ’ОјA з”өжөҒжәҗеҶ…йғЁй©ұеҠЁпјҢдёІиҒ”еўһзӣҠдёә 6гҖӮ

В

UVSET з”өйҳ»еҷЁ RUVSET ж №жҚ®е…¬ејҸпјҲ3пјүдёӯе®ҡд№үзҡ„жүҖйңҖ UVLO еҜјйҖҡз”өеҺӢ VON иҝӣиЎҢйҖүжӢ©гҖӮ

еӣҫ 35пјҡNCP51705 UVSET еҸҜзј–зЁӢ UVLO

В

VON еҖјйҖҡеёёз”ұ SiC MOSFET иҫ“еҮәзү№жҖ§жӣІзәҝеҶіе®ҡпјҢеҰӮ TND6237/D еӣҫ 1 дёӯзӘҒеҮәжҳҫзӨәзҡ„жӣІзәҝгҖӮз”ұдәҺ SiC MOSFET зҡ„еҜјйҖҡз”өйҳ»жҳҫи‘—еўһеҠ пјҢеҚідҪҝ VGS з•ҘжңүйҷҚдҪҺпјҢе…Ғи®ёзҡ„ UVLO ж»һеҗҺеҝ…йЎ»еҫҲе°ҸгҖӮеӣ жӯӨпјҢNCP51705 е…·жңүеӣәе®ҡзҡ„ 1вҲ’V ж»һеҗҺпјҢеӣ жӯӨе…іж–ӯз”өеҺӢ VOFF е§Ӣз»ҲжҜ”и®ҫзҪ®зҡ„ VON дҪҺ 1 VгҖӮ

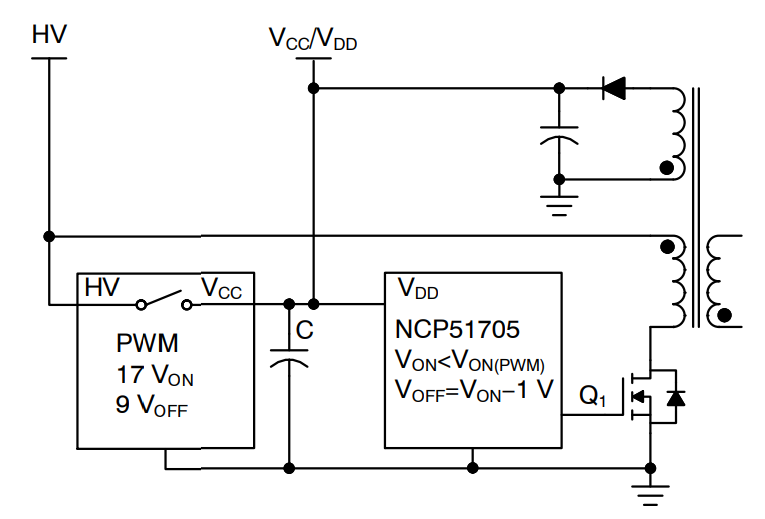

ВеҜ№дәҺеҢ…еҗ«дё“з”ЁеҒҸеҺӢз”өжәҗзҡ„з”өжәҗпјҢеҒҮи®ҫеңЁз”өжәҗзі»з»ҹеӣ ж•…йҡңжҒўеӨҚиҖҢеҗҜеҠЁиҪҜеҗҜеҠЁжҲ–йҮҚеҗҜд№ӢеүҚпјҢVDD й«ҳдәҺжүҖйңҖ VONйҳҲеҖјгҖӮеҜ№дәҺжӯӨзұ»зі»з»ҹпјҢйңҖиҰҒе…·жңү 1вҲ’V UVLO ж»һеҗҺпјҢ并且дёҚдјҡеӣ еҗҜеҠЁжіЁж„ҸдәӢйЎ№иҖҢдә§з”ҹд»»дҪ•еҪұе“ҚгҖӮ然иҖҢпјҢдёҖдәӣз”өжәҗзі»з»ҹд»Һй«ҳз”өеҺӢејҖе§ӢпјҢ然еҗҺдҫқиө–дәҺиҮӘдёҫз»•з»„зҡ„ VDDпјҢеҰӮеӣҫ 36 жүҖзӨәгҖӮ

В

еӣҫ 36пјҡPWM иҮӘдёҫеҗҜеҠЁзӨәдҫӢ

В

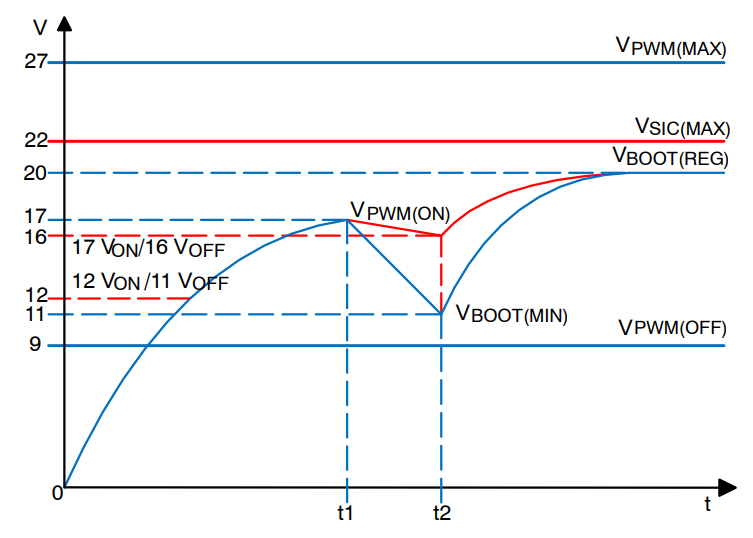

еӣҫдёӯжҳҫзӨәдәҶе…·жңүй«ҳз”өеҺӢ (HV) еҗҜеҠЁиғҪеҠӣд»ҘеҸҠ VON = 17 V е’Ң VOFF= 9 V зҡ„еӣәе®ҡ UVLO йҳҲеҖјзҡ„ PWM жҺ§еҲ¶еҷЁгҖӮж–ҪеҠ HV ж—¶пјҢеҪ“ HV = VON = 17 VпјҢеҶ…йғЁйҖҡйҒ“ејҖе…іжү“ејҖпјҢPWM жҺ§еҲ¶еҷЁд»Һ CVCC жұІеҸ–еҗҜеҠЁз”өжөҒгҖӮеңЁжӯӨжңҹй—ҙпјҢCVCC жӯЈеңЁж”ҫз”өпјҢQ1еҝ…йЎ»ејҖе§ӢеҲҮжҚўпјҢд»ҘеңЁеҸҳеҺӢеҷЁиҮӘдёҫз»•з»„дёӯе»әз«Ӣз”өеҺӢгҖӮиҝҷеҜ№еҸҜд»Һ RUVSET зј–зЁӢзҡ„е…Ғи®ё VON ж–ҪеҠ дәҶйҷҗеҲ¶гҖӮUVSET еҝ…йЎ»и®ҫзҪ®дёәе°ҸдәҺ PWM жҺ§еҲ¶еҷЁзҡ„ UVLO VON зҡ„еҖјгҖӮеӣҫ 37 иҝӣдёҖжӯҘиҜҙжҳҺдәҶиҝҷдәӣеҗҜеҠЁз»ҶиҠӮпјҢе…¶дёӯ PWM з”өеҺӢйҳҲеҖјжҳҫзӨәдёәи“қиүІпјҢNCP51705 жҳҫзӨәдёәзәўиүІгҖӮ

еӣҫ 37пјҡиҮӘдёҫеҗҜеҠЁж—¶еәҸ

В

дёәдәҶеҲҮжҚўе…·жңүжңҖй«ҳ VGS зҡ„ SiC MOSFETпјҢйңҖиҰҒе°Ҷ VONи®ҫзҪ®дёәе°ҪеҸҜиғҪжҺҘиҝ‘ PWM жҺ§еҲ¶еҷЁзҡ„ UVLO еҜјйҖҡгҖӮеңЁиҝҷж ·еҒҡж—¶жүҖиҝӣиЎҢзҡ„жқғиЎЎж„Ҹе‘ізқҖеңЁ О”t (t2вҲ’t1) жңҹй—ҙ О”V = 1 VгҖӮCVCC зҡ„ж”ҫз”өйқһеёёжө…пјҢеӣ жӯӨйңҖиҰҒиҫғеӨ§зҡ„з”өе®№еҖјгҖӮдҫӢеҰӮпјҢеҒҮи®ҫеҗҜеҠЁз”өжөҒдёә 1 mAпјҢО”t = 3 ms дё” О”V = 1 VпјҢеҲҷйңҖиҰҒз”ЁдәҺ CVCC зҡ„ 3вҲ’ОјF з”өе®№гҖӮзӣёеҸҚпјҢеҰӮжһң VON и®ҫзҪ®дёәжҜ”жңҖе°ҸиҮӘдёҫж”ҫз”өз”өеҺӢ VBOOT(MIN) й«ҳ 1 VпјҢеҲҷе…Ғи®ё CVCC еңЁжӣҙе®Ҫзҡ„ О”V (17 V вҲ’ 11 V) иҢғеӣҙеҶ…ж”ҫз”өпјҢ并且еҸҜд»ҘдҪҝз”Ёжӣҙе°Ҹзҡ„з”өе®№еҖјгҖӮз»ҷе®ҡзӣёеҗҢзҡ„ 1 mAпјҢО”t = 3 ms дё”е…Ғи®ё О”V = 6 VпјҢжүҖйңҖзҡ„ CVCC з”өе®№еҖјйҷҚдҪҺиҮі 500 nFпјӣеҮҸе°‘дәҶ 6 еҖҚгҖӮ然иҖҢпјҢз”ұдәҺ SiC MOSFET е°ҶеңЁ VGS = 11 V зҡ„жғ…еҶөдёӢеҲҮжҚўпјҢеӣ жӯӨжүҖдә§з”ҹзҡ„еҪұе“ҚеҸҜиғҪеҫҲеӨ§гҖӮжҳҫ然пјҢеңЁеҗҜеҠЁеүҚе°Ҷ NCP51705 еҒҸзҪ®жҳҜйҰ–йҖүж–№жі•гҖӮ

В ж•°еӯ—еҗҢжӯҘе’Ңж•…йҡңжҠҘе‘Ҡ вҖ“ XENXEN дҝЎеҸ·жҳҜ VGS еҸҚзӣёзҡ„ 5 V ж•°еӯ—иЎЁзӨәгҖӮдёәдәҶжҠҘе‘Ҡй©ұеҠЁеҷЁвҖңзҠ¶жҖҒвҖқпјҢPWM иҫ“е…Ҙиў«и®ӨдёәжӣҙеҮҶзЎ®пјҢеӣ дёәе®ғжқҘиҮӘ SiC ж …жһҒз”өеҺӢпјҢдј ж’ӯ延иҝҹеӨ§еӨ§еҮҸе°‘гҖӮжӯӨдҝЎеҸ·еҸҜд»ҘеңЁеҚҠжЎҘз”өжәҗжӢ“жү‘дёӯз”ЁдҪңж•…йҡңж Үеҝ—е’ҢеҗҢжӯҘдҝЎеҸ·пјҢдёәе®һж–ҪдәӨеҸүдј еҜјпјҲйҮҚеҸ пјүдҝқжҠӨжү“дёӢеҹәзЎҖгҖӮжҜҸеҪ“ XEN дёәй«ҳгҖҒVGSдёәдҪҺж—¶пјҢеҲҷ SiC MOSFET дёәе…іж–ӯзҠ¶жҖҒгҖӮеӣ жӯӨпјҢеҰӮжһң XEN е’Ң PWM иҫ“е…ҘдҝЎеҸ·еқҮдёәй«ҳпјҢеҲҷжЈҖжөӢеҲ°ж•…йҡңзҠ¶жҖҒпјҢ并иҝӣиЎҢж•°еӯ—еҲҶй…ҚпјҢд»ҘйҮҮеҸ–еҸҜиғҪйңҖиҰҒзҡ„д»»дҪ•йў„йҳІжҺӘж–ҪгҖӮ

В е°ҒиЈ…WBG еҚҠеҜјдҪ“дҪҝй«ҳеҺӢиҪ¬жҚўеҷЁиғҪеӨҹеңЁжӣҙжҺҘиҝ‘дҪҺеҺӢпјҲдҪҺдәҺ 100 VпјүејҖе…ійў‘зҺҮзҡ„жғ…еҶөдёӢе·ҘдҪңгҖӮеҜ№дәҺдҪҺеҺӢиҪ¬жҚўеҷЁиҖҢиЁҖпјҢеҚҠеҜјдҪ“е°ҒиЈ…зҡ„еҸ‘еұ•еҜ№еҪ“д»ҠејҖе…іжҖ§иғҪзҡ„е®һзҺ°иө·еҲ°дәҶе…ій”®дҪңз”ЁгҖӮзЎ… MOSFET е°ҒиЈ…еҸ–еҫ—дәҶиҝӣжӯҘпјҢдҫӢеҰӮеҸҢйқўеҶ·еҚҙгҖҒеӨ№з„ҠгҖҒзғӯеўһејәеҠҹзҺҮе°ҒиЈ…е’ҢдҪҺз”өж„ҹгҖҒж— еј•зәҝе°ҒиЈ…гҖӮеҗҢж ·пјҢж …жһҒй©ұеҠЁеҷЁ IC е°ҒиЈ…д№ҹвҖңзҳҰиә«вҖқжҳҺжҳҫгҖӮжӣҙзҹӯзҡ„з®ЎиҠҜеҲ°еј•зәҝгҖҒй”®еҗҲзәҝиҝһжҺҘпјҢеҠ дёҠжЁЎеҲ¶ж— еј•зәҝе°ҒиЈ… (MLP)пјҢеҜ№дәҺжңҖеӨ§йҷҗеәҰең°еҮҸе°‘й©ұеҠЁеҷЁдҫ§зҡ„еҜ„з”ҹз”өж„ҹиҮіе…ійҮҚиҰҒгҖӮй©ұеҠЁеҷЁе’Ң MOSFET (DrMOS) е…ұе°ҒиЈ…жҳҜеҮҸе°‘еҜ„з”ҹз”өж„ҹгҖҒжҸҗй«ҳж•ҲзҺҮе’Ңзј©е°Ҹз”өи·Ҝжқҝйқўз§Ҝзҡ„жңҖж–°жӯҘйӘӨгҖӮDrMOS зӯүж”№иҝӣжүҖж¶үеҸҠзҡ„з”өеҺӢзӣёеҪ“дҪҺпјҢеӣ жӯӨеҸҜд»Ҙе®һзҺ°гҖӮ

В

еңЁй«ҳеҺӢиҪ¬жҚўеҷЁйўҶеҹҹпјҢзҲ¬з”өи·қзҰ»е’Ңз”өж°”й—ҙйҡҷзӯүжңҖе°Ҹй—ҙи·қиҰҒжұӮдҪҝеҫ—й«ҳжҖ§иғҪ SiC MOSFET дҫқ然йҮҮз”ЁдҪҺжҖ§иғҪ TOвҲ’220 еһӢе’Ң TOвҲ’247 еһӢе°ҒиЈ…гҖӮиҝҷдәӣе°ҒиЈ…е·Із»ҸеҚҒеҲҶе®Ңе–„пјҢй•ҝжңҹд»ҘжқҘдёҖзӣҙжҳҜиЎҢдёҡж ҮеҮҶгҖӮе®ғ们йқһеёёйҖӮеҗҲе·Ҙдёҡеә”з”ЁпјҢеқҡеӣәдё”жҳ“дәҺж•ЈзғӯпјҢдҪҶе…¶й•ҝеј•зәҝе’ҢеҶ…йғЁй”®еҗҲзәҝеҜјиҮҙеҜ„з”ҹз”өж„ҹжӣҙй«ҳгҖӮSiC MOSFET зҺ°еңЁдҪҝиҝҷдәӣеҜ„з”ҹз”өж„ҹеҸ—еҲ°зғӯеә”еҠӣгҖҒйў‘зҺҮе’Ң dV/dt йҖҹзҺҮзҡ„еҪұе“ҚпјҢд»ҘеүҚеңЁй«ҳеҺӢзЎ…жҷ¶дҪ“з®ЎдёӯпјҢиҝҷжҳҜд»ҺжңӘи®ҫжғіеҲ°зҡ„гҖӮеҸҜд»ҘиҜҙпјҢSiC дҝғиҝӣдәҶеҜ№й«ҳеҺӢеҲҶз«Ӣе°ҒиЈ…зҡ„йҮҚж–°жҖқиҖғгҖӮ

В

е°Ҫз®ЎеҲҶз«Ӣ组件并йқһеҰӮжӯӨпјҢдҪҶ SiC ж …жһҒй©ұеҠЁеҷЁиғҪеӨҹе……еҲҶеҲ©з”ЁдёҺдҪҺеҺӢиҪ¬жҚўеҷЁй©ұеҠЁеҷЁзӣёеҗҢзҡ„е°ҒиЈ…ж”№иҝӣгҖӮNCP5170 з®ЎиҠҜе°ҒиЈ…жҲҗ 24 еј•и„ҡгҖҒ4 Г— 4 mmгҖҒзғӯеўһејә MLPпјҢеҰӮеӣҫ 38 жүҖзӨәгҖӮ

еӣҫ 38пјҡNCP51705 24 еј•и„ҡгҖҒ4 4 mmгҖҒMLP е°ҒиЈ…е’Ңеј•и„ҡиҫ“еҮә

ВжүҖжңүй«ҳз”өжөҒз”өжәҗеј•и„ҡйғҪзҝ»еҖҚпјҢдҪҚдәҺ IC зҡ„еҸіеҚҠйғЁеҲҶгҖӮжӯӨеӨ–пјҢжҜҸдёӘзҝ»еҖҚеј•и„ҡйғҪйҖҡиҝҮеҶ…йғЁеҸҢй”®еҗҲзәҝиҝһжҺҘеҲ°з®ЎиҠҜпјҢд»Ҙе®һзҺ°е°ҪеҸҜиғҪжңҖдҪҺзҡ„з”өж„ҹгҖӮжүҖжңүдҪҺеҠҹиҖ—ж•°еӯ—дҝЎеҸ·д»…дёәеҚ•еј•и„ҡпјҢдҪҚдәҺ IC зҡ„е·ҰеҚҠйғЁеҲҶпјҢдёә PWM жҲ–ж•°еӯ—жҺ§еҲ¶еҷЁжҸҗдҫӣдәҶж–№дҫҝгҖҒзӣҙжҺҘзҡ„жҺҘеҸЈгҖӮ

ВNCP51705 е°ҒиЈ…зҡ„еә•йғЁеҢ…жӢ¬дёҖдёӘз”өз»қзјҳгҖҒеҜјзғӯгҖҒжҡҙйңІзҡ„з„ҠзӣҳгҖӮиҜҘз„ҠзӣҳжңӘиҝһжҺҘеҲ° PGND жҲ– SGNDпјҢдҪҶдјҡйҖҡиҝҮзғӯйҖҡеӯ”иҝһжҺҘеҲ°йҡ”зҰ»й“ң PCB з„ҠзӣҳиҝӣиЎҢж•ЈзғӯгҖӮ

В

еҰӮжһңж•ЈзғӯжҲҗдёәдёҖдёӘй—®йўҳпјҢеә”зү№еҲ«жіЁж„ҸеӣӣдёӘдё»иҰҒзҡ„еҠҹиҖ—еӣ зҙ пјҡ

1. дёҺй©ұеҠЁеӨ–йғЁ SiC MOSFET зӣёе…ізҡ„ OUTSRC е’Ң OUTSNK жҚҹиҖ—гҖӮиҝҷдәӣжҳҜдёҺејҖе…ійў‘зҺҮжҲҗжҜ”дҫӢзҡ„ж …жһҒз”өиҚ·зӣёе…іжҚҹиҖ—гҖӮйҷҚдҪҺејҖе…ійў‘зҺҮе°ҶйҷҚдҪҺеҠҹиҖ—

2. VDDе’Ң V5V д№Ӣй—ҙзҡ„ LDOпјҢиғҪеӨҹжҸҗдҫӣй«ҳиҫҫ 20 mA зҡ„з”өжәҗгҖӮеҲҮеӢҝеҠ иҪҪи¶…иҝҮж•°еӯ—йҡ”зҰ»еҷЁжҲ–е…үиҖҰеҗҲеҷЁеҒҸеҺӢзҡ„ V5V

3. VDD е’Ң VCH д№Ӣй—ҙзҡ„ LDOпјҢиҝҷжҳҜеҶ…йғЁе……з”өжіөзҡ„дёҖйғЁеҲҶ

4. еҶ…йғЁе……з”өжіөз”өжәҗејҖе…іпјҢеҸҜзҰҒ用并用еӨ–йғЁиҙҹеҒҸеҺӢжӣҝжҚўпјҢеҰӮе……з”өжіөвҖ“VEE (VEESET) дёҖиҠӮжүҖиҝ°

В

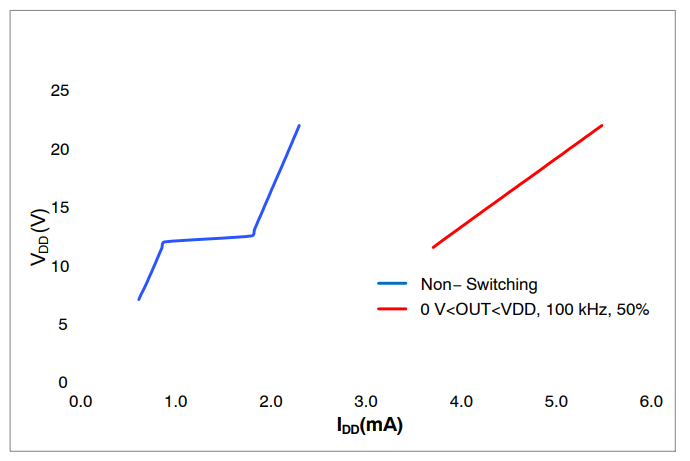

В зі»з»ҹжҖ§иғҪеҜ№дәҺ VDD> 7 VпјҢйқҷжҖҒз”өжөҒзәҝжҖ§зј“еҚҮпјҢзӣҙиҮіи¶…иҝҮи®ҫзҪ®зҡ„ UVLO йҳҲеҖјгҖӮеӣҫ 39 жүҖзӨәзҡ„и“қиүІиҝ№зәҝиЎЁзӨә VDD дёҺ IDDпјҢж— иҫ“е…ҘпјҲйқһејҖе…іпјүпјҢVDD(UVLO)= 12 VпјҢV5V и°ғиҠӮеҷЁж— иҙҹиҪҪгҖӮеҜ№дәҺ 7 V < VDD < 22 VпјҢIDD жөӢйҮҸдёә 0.6 mA < IDD< 2.3 mAгҖӮеҪ“ VDD и¶…иҝҮ UVLO йҳҲеҖјж—¶пјҢдёӯй—ҙзҡ„е№іеқҰзәҝиЎЁзӨә IDD з”өжөҒеўһеҠ зәҰ ~1вҲ’mAгҖӮ

ВзәўиүІиҝ№зәҝиЎЁзӨәеңЁзҰҒз”ЁеҶ…йғЁе……з”өжіөзҡ„еҗҢж—¶еҗ‘ IN+ ж–ҪеҠ 100 kHzгҖҒ50% и„үеҶІиҫ“е…Ҙзҡ„жғ…еҶөгҖӮдҪҝз”Ё 4.99 О© + 2.2 nF иҙҹиҪҪпјҢиҝҷжҳҜе…ёеһӢ SiC MOSFET зҡ„зӯүж•Ҳиҫ“е…ҘгҖӮеӨ–йғЁжәҗжһҒе’ҢжјҸжһҒз”өйҳ»дёә 3О©гҖӮеҜ№дәҺ 12 V < VDD < 22 VпјҢIDD жөӢйҮҸдёә 3.7 mA < IDD < 5.5 mAгҖӮ

еӣҫ 39пјҡVDD дёҺ IDDпјҢйқһејҖе…ідёҺејҖе…і

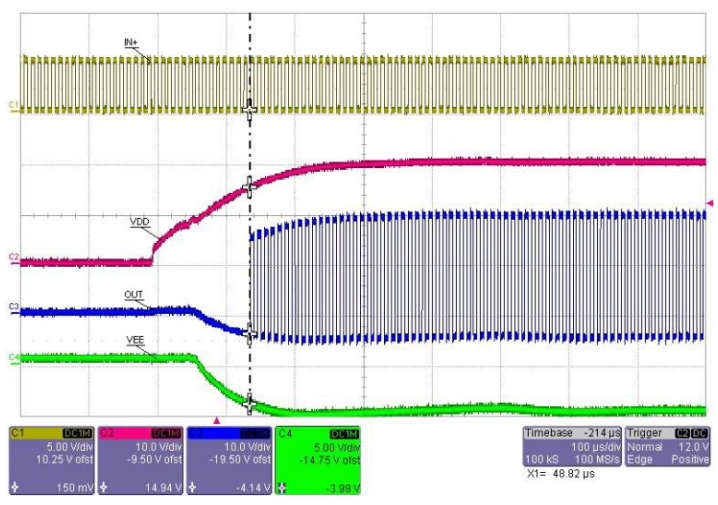

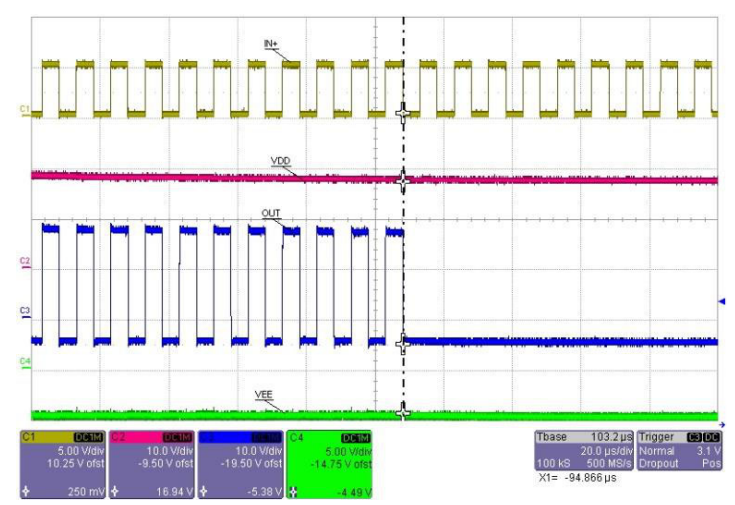

Веӣҫ 40 жүҖзӨәзҡ„еҗҜеҠЁжіўеҪўжҳҫзӨәдәҶ VDD д№ӢеүҚеҮәзҺ°зҡ„ IN +гҖӮVDD д»Һ 0 V дёҠеҚҮиҮі 20 VпјҢUVSET = 2 VпјҲжңӘжҳҫзӨәпјүпјҢзӣёеҪ“дәҺ VDD(UVLO) = 12 VгҖӮVEE иў«и®ҫзҪ®дёәеңЁ вҲ’5 V и°ғиҠӮпјҢVEESET = V5VпјҲжңӘжҳҫзӨәпјүпјҢзӣёеҪ“дәҺ VEE(UVLO) = вҲ’4 VгҖӮеҪ“ VEE = вҲ’4 V ж—¶пјҢиҫ“еҮәдҫҝдјҡеҗҜз”ЁпјҢеҚідҪҝ VDD > 12 V (VDD= 15 V)гҖӮиҝҳиҰҒжіЁж„ҸпјҢеңЁиҝ‘ 100 Ојs зҡ„ж—¶й—ҙеҶ…пјҢOUT (VGS) е°ҸдәҺ 20 VгҖӮж №жҚ® VDD еҗҜеҠЁзҡ„ dV/dt йҖҹзҺҮпјҢиҜҘж—¶й—ҙеҸҜиғҪжӣҙй•ҝпјҢеӣ жӯӨпјҢеңЁзј–зЁӢ UVSET ж—¶еә”иҖғиҷ‘ SiC MOSFET зҡ„зғӯеә”еҠӣгҖӮ

еӣҫ 40пјҡCH1вҲ’IN+пјҢCH2вҲ’VDDпјҢCH3вҲ’OUTпјҢCH4вҲ’VEEпјӣVDD(UVLO) = 12 VпјҢVEE(UVLO) = вҲ’4 V

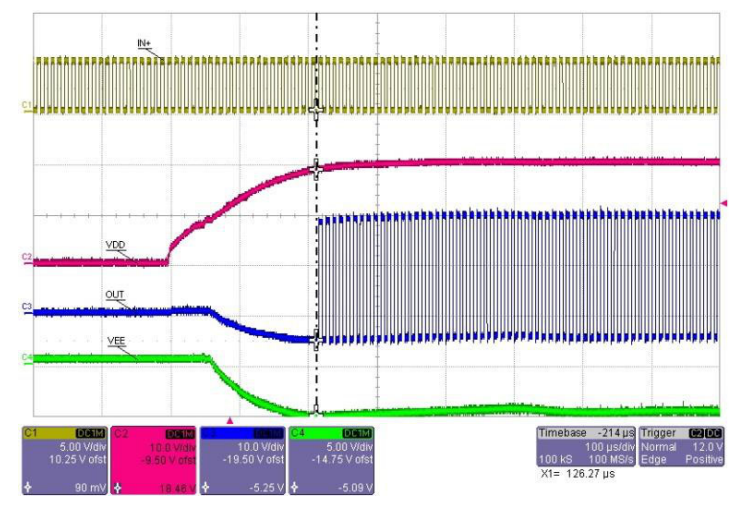

Веӣҫ 41 дёӯжҳҫзӨәдәҶзӣёеҗҢзҡ„еҗҜеҠЁжіўеҪўпјҢдҪҶ UVSET = 3 VпјҲжңӘжҳҫзӨәпјүпјҢзӣёеҪ“дәҺ VDD(UVLO) = 18 VгҖӮеңЁиҝҷз§Қжғ…еҶөдёӢпјҢеҪ“ VDD = 18 V ж—¶пјҢOUT (VGS) дҫҝдјҡеҗҜз”ЁпјҢеҚідҪҝ VEE < вҲ’4 V (VEE= вҲ’5 V)гҖӮе“ӘдёӘ UVLO еҚ дјҳеҠҝеҸ–еҶідәҺ VDD дёҺ VEE зҡ„ dV/dt йҖҹзҺҮгҖӮе…ій”®зӮ№жҳҜ NCP51705 иҫ“еҮәиў«зҰҒз”ЁпјҢзӣҙеҲ° VDD е’Ң VEE йғҪй«ҳдәҺжҲ–дҪҺдәҺеҗ„иҮӘзҡ„ UVLO йҳҲеҖјгҖӮдёҺеӣҫ 40 зӣёжҜ”пјҢиҜ·жіЁж„Ҹиҫғй«ҳзҡ„ UVLO и®ҫзҪ®еҜ№ OUT (VGS) зҡ„еҪұе“ҚпјҢе…¶дёӯ第дёҖдёӘ OUT и„үеҶІеҮәзҺ°еңЁ 20 V е’Ң вҲ’5 V йҷ„иҝ‘гҖӮ

еӣҫ 41пјҡCH1вҲ’IN+пјҢCH2вҲ’VDDпјҢCH3вҲ’OUTпјҢCH4вҲ’VEEпјӣVDD(UVLO) = 18 VпјҢVEE(UVLO) = вҲ’4 V

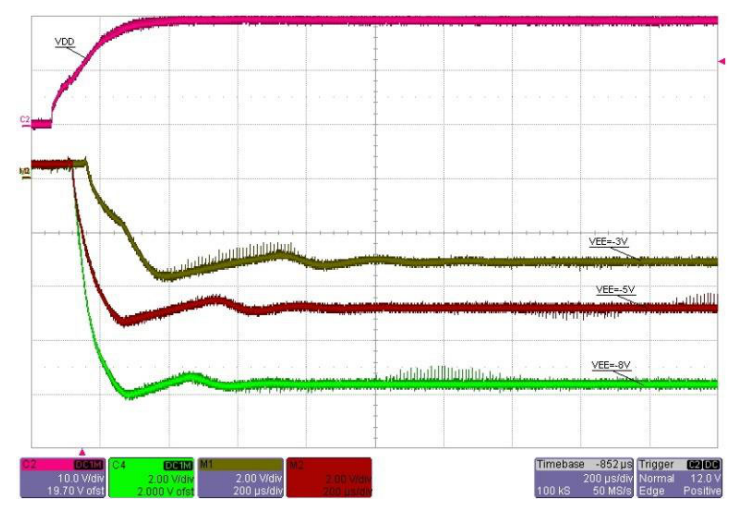

ВNCP51705 еҶ…йғЁе……з”өжіөжңүдёҖдёӘзј“ж…ўзҡ„жҺ§еҲ¶еӣһи·ҜпјҢе…¶ж•ҲжһңеҸҜд»Һ VEE еҗҜеҠЁжңҹй—ҙи§ӮеҜҹеҲ°зҡ„иҪ»еҫ®дёӢеҶІе’Ң <400 Ојs ж ЎжӯЈдёӯзңӢеҮәпјҢеҰӮеӣҫ 42 жүҖзӨәгҖӮи¶…иҝҮ 400 Ојs ж—¶пјҢVEE з”өеҺӢзЁіе®ҡиҮі вҲ’3 VгҖҒвҲ’5 V жҲ– вҲ’8 V зҡ„и°ғиҠӮи®ҫе®ҡеҖјгҖӮ

еӣҫ 42пјҡVEE еҗҜеҠЁ

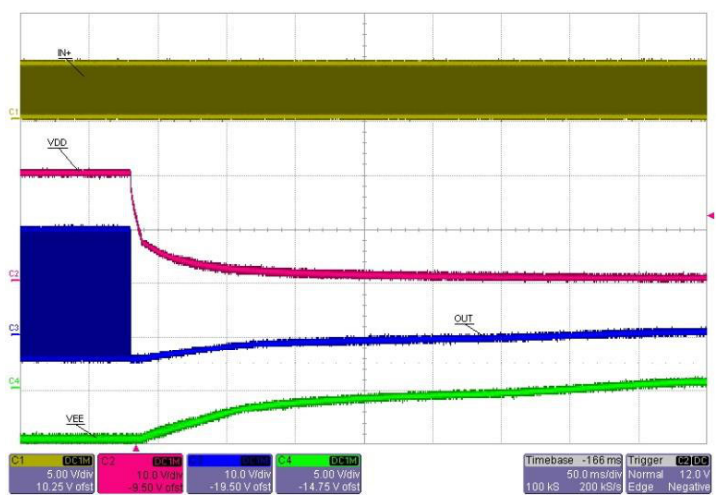

Ве…іжңәж“ҚдҪңе№ізЁіпјҢж— жҜӣеҲәгҖӮеҰӮеӣҫ 43 жүҖзӨәпјҢOUT еҒңжӯўеҲҮжҚўе№¶и·ҹиёӘеҚёиҪҪзҡ„ VEEгҖӮVEE д»Һ вҲ’5 V еҲ° 0 V зҡ„ж”ҫз”өж—¶й—ҙзәҰдёә 300 msгҖӮ

еӣҫ 43пјҡCH1вҲ’IN+пјҢCH2вҲ’VDDпјҢCH3вҲ’OUTпјҢCH4вҲ’VEEпјӣе…іжңә

Веӣҫ 44 жҳҫзӨәдәҶеӣҫ 43 дёӯж—¶й—ҙеҹәеҮҶзҡ„ж”ҫеӨ§еӣҫгҖӮUVSET иў«й…ҚзҪ®дёә 3 V (VDD(UVLO) = 18V)пјҢеҶ…йғЁ VDD UVLO ж»һеҗҺеңЁеҶ…йғЁеӣәе®ҡдёә 1 VгҖӮеҪ“иҫ“еҮәиў«зҰҒз”Ёж—¶пјҢе…үж ҮдҪҚзҪ®жҳҫзӨә VDD = 17 VпјҲ18 VвҲ’1 V ж»һеҗҺпјүпјҢеҚідҪҝ VEE= вҲ’4.5 V (VEESET = V5V)пјҢе№¶дё”ж №жҚ®е…¶ вҲ’4 V UVLO д»ҚеӨ„дәҺжҙ»еҠЁзҠ¶жҖҒгҖӮе°Ҫз®Ў VDD зҡ„иЎ°еҮҸеҫҲж…ўпјҢдҪҶеңЁ UVLO_OFF д№ӢеҗҺпјҢд№ҹеҸҜд»ҘзңӢеҲ°жңҖеҗҺдёҖдёӘиҫ“еҮәи„үеҶІзҡ„з»ҲжӯўеҫҲе№ІеҮҖпјҢжІЎжңүжқӮж•Ји„үеҶІжҲ–жҜӣеҲәгҖӮ

еӣҫ 44пјҡCH1вҲ’IN+пјҢCH2вҲ’VDDпјҢCH3вҲ’OUTпјҢCH4вҲ’VEEпјӣе…іжңәпјҢVDD_UVLO(OFF) = 17 V

ВеҜјйҖҡдј ж’ӯ延иҝҹзҡ„жөӢйҮҸиҢғеӣҙд»Һ 90% IN+ дёҠеҚҮиҮі 10% OUT дёҠеҚҮгҖӮе°Ҫз®Ў SiC й©ұеҠЁеҷЁе°ҶеңЁжӣҙй«ҳзҡ„ VDD дёӢе·ҘдҪңпјҢдҪҶеӨ§еӨҡж•° MOSFET дј ж’ӯ延иҝҹиў«жҢҮе®ҡдёәеҲҮжҚўеҲ° VDD = 12 V зҡ„ 1вҲ’nF иҙҹиҪҪгҖӮ

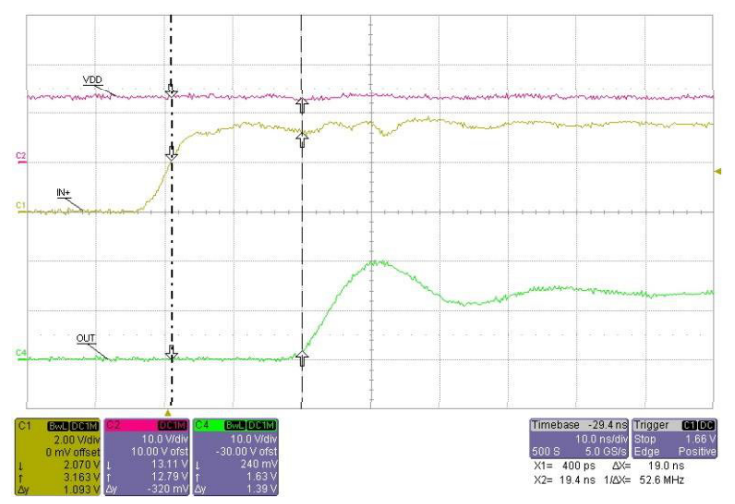

Веӣҫ 45 жҳҫзӨәдәҶеңЁиҝҷдәӣж ҮеҮҶжөӢиҜ•жқЎд»¶дёӢжөӢеҫ—зҡ„еҜјйҖҡдј ж’ӯ延иҝҹдёә 19 nsгҖӮ

В

еӣҫ 45пјҡCH1вҲ’IN+пјҢCH2вҲ’VDDпјҢCH4вҲ’OUTпјӣдёҠеҚҮжІҝдј ж’ӯ延иҝҹ

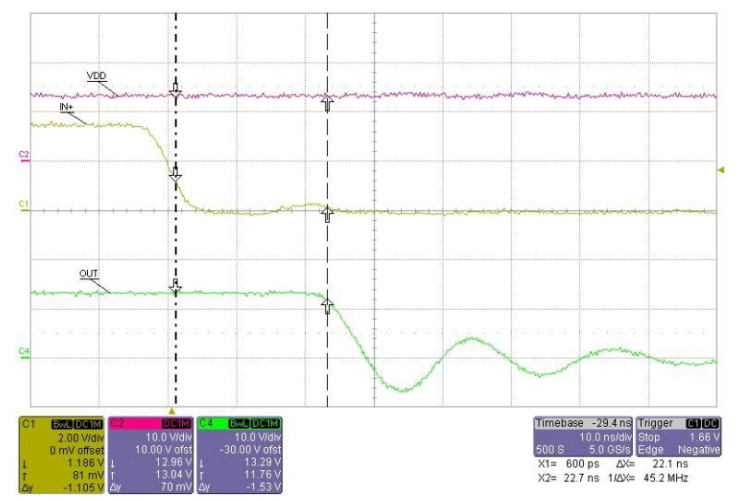

ВеҗҢж ·пјҢе…іж–ӯдј ж’ӯ延иҝҹзҡ„жөӢйҮҸиҢғеӣҙд»Һ 10% IN+ дёӢйҷҚиҮі 90% OUT дёӢйҷҚгҖӮеӣҫ 46 жҳҫзӨәдәҶеңЁзӣёеҗҢж ҮеҮҶжөӢиҜ•жқЎд»¶дёӢжөӢеҫ—зҡ„е…іж–ӯдј ж’ӯ延иҝҹдёә 22 nsгҖӮжҜҸдёӘиҫ№зјҳзҡ„иҫ“еҮәдёҠеҚҮе’ҢдёӢйҷҚж—¶й—ҙзәҰдёә 5 nsгҖӮ

В

еӣҫ 46пјҡCH1вҲ’IN+пјҢCH2вҲ’VDDпјҢCH4вҲ’OUTпјӣдёӢйҷҚжІҝдј ж’ӯ延иҝҹ

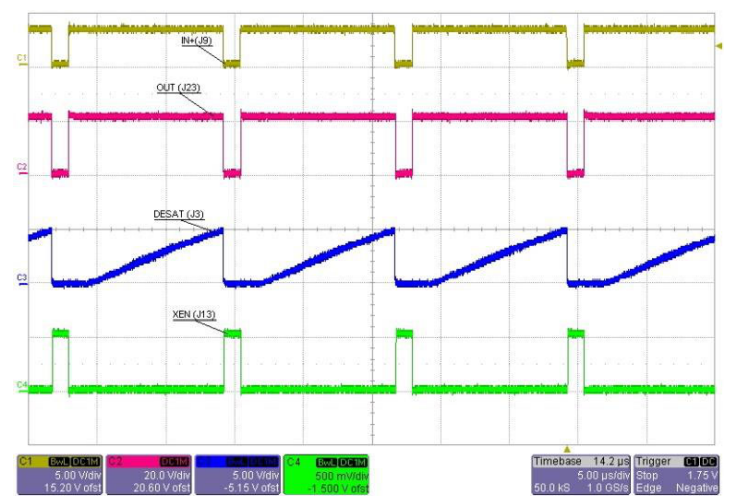

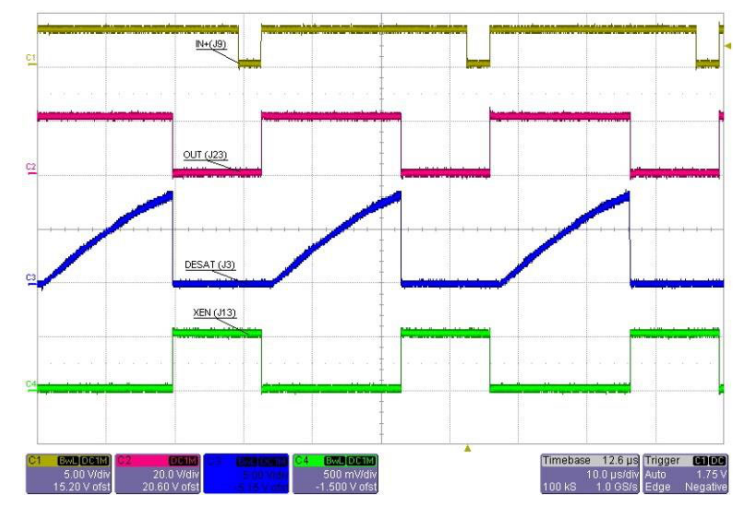

ВDESAT е’Ң XEN жіўеҪўеҲҶеҲ«еҰӮеӣҫ 47 е’Ңеӣҫ 48 жүҖзӨәгҖӮз”ұдәҺжөӢиҜ•д»…з”ЁдәҺ IC йӘҢиҜҒпјҲж— еҠҹзҺҮзә§пјүпјҢеӣ жӯӨе°Ҷ 100вҲ’pF еӣәе®ҡз”өе®№иҝһжҺҘеҲ° DESAT еј•и„ҡгҖӮеӣҫ 47 жүҖзӨәзҡ„жіўеҪўиЎЁжҳҺ DESAT дҪҺдәҺ 7.5 V йҳҲеҖјпјҢиҫ“еҮәеңЁжӯЈеёёж“ҚдҪңдёӢеҲҮжҚўгҖӮеҰӮжһң IN+ йў‘зҺҮйҷҚдҪҺпјҲеҜјйҖҡж—¶й—ҙеўһеҠ пјүпјҢеҲҷ 100вҲ’pF DESAT з”өе®№е°ҶеҸҜд»Ҙе……з”өиҮіжӣҙй«ҳзҡ„з”өеҺӢгҖӮеҰӮеӣҫ 48 жүҖзӨәпјҢDESAT з”өеҺӢе·ІиҫҫеҲ° 7.5вҲ’V йҳҲеҖјгҖӮиҫ“еҮәеҗҺжІҝеңЁиҫ“е…Ҙз”өеҺӢеҲҮжҚўдёәдҪҺд№ӢеүҚз»ҲжӯўгҖӮDESAT е°Ҹж–ңеқЎз”ЁдәҺејәи°ғз»Ҳжӯўзҡ„ OUT и„үеҶІдёҠжІЎжңүеҮәзҺ°жҜӣеҲәзҡ„дәӢе®һгҖӮеңЁејҖе…із”өжәҗеә”з”ЁдёӯпјҢDESAT еј•и„ҡдёҠеҸҜд»ҘдҪҝз”Ёе°ҸеһӢ (<100 pF) еӨ–йғЁз”өе®№иҝӣиЎҢй«ҳйў‘еҷӘеЈ°ж»ӨжіўгҖӮ

ВXEN дҝЎеҸ·дёҺ OUT дҝЎеҸ·зӣёеҸҚгҖӮж— и®әй©ұеҠЁеҷЁжҳҜжӯЈеёёиҝҗиЎҢиҝҳжҳҜйқўдёҙ DESAT ж•…йҡңпјҢXEN дҝЎеҸ·йғҪиғҪеҮҶзЎ®и·ҹиёӘд»»дёҖжғ…еҶөдёӢзҡ„еҸҚеҗ‘ OUT дҝЎеҸ·гҖӮ

еӣҫ 47пјҡCH1вҲ’IN+пјҢCH2вҲ’OUTпјҢCH3вҲ’DESATпјҢCH4вҲ’XENпјӣVDESAT < 7.5 V

В

еӣҫ 48пјҡCH1вҲ’IN+пјҢCH2вҲ’OUTпјҢCH3вҲ’DESATпјҢCH4вҲ’XENпјӣVDESAT = 7.5 V

В еә”з”ЁSiC MOSFET еҸҜд»ҘйҖӮз”ЁдәҺзӣ®еүҚдҪҝз”Ё IGBT зҡ„еҗ„з§Қеә”з”ЁеңәжҷҜгҖӮдёҖдәӣиҫғеёёи§Ғзҡ„з”ЁйҖ”еҢ…жӢ¬й«ҳеҺӢејҖе…із”өжәҗгҖҒж··еҗҲеҠЁеҠӣе’Ңз”өеҠЁжұҪиҪҰе……з”өеҷЁгҖҒз”өж°”еҢ–й“Ғи·Ҝиҝҗиҫ“гҖҒз„ҠжңәгҖҒжҝҖе…үеҷЁгҖҒе·Ҙдёҡи®ҫеӨҮеҸҠе…¶д»–жіЁйҮҚй«ҳжё©ж“ҚдҪңзҡ„зҺҜеўғгҖӮе°Өе…¶еҖјеҫ—дёҖжҸҗзҡ„дёӨдёӘйўҶеҹҹжҳҜеӨӘйҳіиғҪйҖҶеҸҳеҷЁе’Ңй«ҳеҺӢж•°жҚ®дёӯеҝғгҖӮжӣҙй«ҳзҡ„зӣҙжөҒз”өеҺӢжңүеҲ©дәҺеҮҸе°Ҹзәҝ规еҺҡеәҰгҖҒжҺҘзәҝзӣ’гҖҒдә’иҝһпјҢ并жңҖз»ҲжңҖеӨ§йҷҗеәҰең°еҮҸе°‘дј еҜјжҚҹиҖ—пјҢд»ҺиҖҢжҸҗй«ҳж•ҲзҺҮгҖӮзӣ®еүҚпјҢеӨ§еӨҡж•°еӨ§еһӢе…үдјҸзі»з»ҹеқҮйҮҮз”Ё 1вҲ’kV зӣҙжөҒжҖ»зәҝпјҢжңӘжқҘи¶Ӣеҗ‘дәҺйҮҮз”Ё 1.5вҲ’kV жҖ»зәҝгҖӮеҗҢж ·пјҢдҪҝз”Ё 380вҲ’V й…Қз”өзҪ‘з»ңзҡ„ж•°жҚ®дёӯеҝғеҸҜд»Ҙе°ҶзӣҙжөҒз”өеҺӢжҸҗеҚҮиҮі 800 VгҖӮ

ВNCP5170 зҡ„еҮ дёӘеҹәжң¬еә”з”ЁзӨәдҫӢеҰӮдёӢжүҖзӨәгҖӮ

В1.дҪҺеҺӢдҫ§ејҖе…і

еӣҫ 49 жҳҫзӨәдәҶз”ЁдәҺдҪҺеҺӢдҫ§ејҖе…іеә”з”Ёзҡ„ NCP51705 зҡ„йЎ¶еұӮзӨәж„ҸеӣҫгҖӮжңӘжҳҫзӨәйҡ”зҰ»пјҢеӣ жӯӨжҺ§еҲ¶еҷЁе’Ңй©ұеҠЁеҷЁд№Ӣй—ҙдёәзӣҙиҝһжҺҘеҸЈпјҢдҪҶжғ…еҶө并йқһжҖ»жҳҜиҝҷж ·гҖӮжӯӨзӨәж„Ҹеӣҫж—ЁеңЁиҜҙжҳҺпјҢиҰҒжҸҗдҫӣе…ЁеҠҹиғҪгҖҒеҸҜйқ е’ҢзЁіеҒҘзҡ„ SiC ж …жһҒй©ұеҠЁз”өи·ҜпјҢеҸӘйңҖз”ҡе°‘зҡ„еӨ–йғЁз»„件гҖӮиҝҳеә”жҸҗеҸҠпјҢе°Ҫз®ЎеҸӘйңҖиҰҒеҚ•дёҖ VDD з”өеҺӢиҪЁпјҢдҪҶе…¶йўқе®ҡеҖјеә”иҮіе°‘дёә 50 V/nsпјҢд»ҘйҳІжӯўTND6237/D дёӯзҡ„еҲҶз«Ӣ SIC ж …жһҒй©ұеҠЁдёҖиҠӮдёӯзҡ„еҲҶз«Ӣж …жһҒй©ұеҠЁиҜҙжҳҺжүҖиҝ°зҡ„жқӮж•Јз”өжөҒи„үеҶІгҖӮеҰӮжһң VDD з”өеҺӢиҪЁз”ұдё“з”Ёиҫ…еҠ©з”өжәҗжҸҗдҫӣпјҢеҲҷеә”зү№еҲ«жіЁж„Ҹи®ҫи®Ўе…·жңүи¶…дҪҺдёҖж¬Ў-дәҢж¬ЎжқӮж•Јз”өе®№зҡ„еҸҳеҺӢеҷЁгҖӮ

В

еӣҫ 49пјҡдҪҺеҺӢдҫ§ејҖе…ізӨәдҫӢ

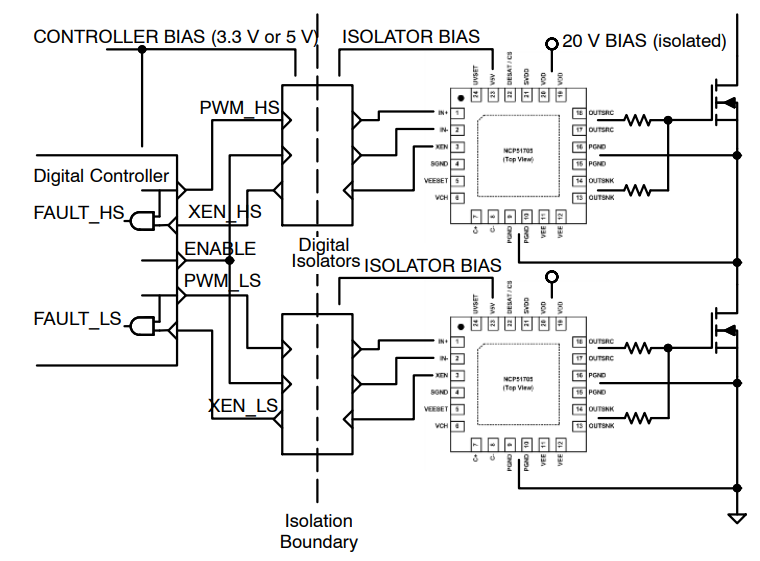

В2.еҚҠжЎҘжҰӮеҝө

еңЁеҚҠжЎҘз”өжәҗжӢ“жү‘дёӯеҸҜд»ҘжүҫеҲ° SiC MOSFET жӣҙзҺ°е®һзҡ„з”ЁйҖ”пјҢеҰӮеӣҫ 50 жүҖзӨәгҖӮй«ҳеҠҹзҺҮеә”з”ЁеҖҫеҗ‘дәҺеңЁй«ҳеҺӢдҫ§е’ҢдҪҺеҺӢдҫ§йғҪдҪҝз”Ёйҡ”зҰ»й©ұеҠЁеҷЁгҖӮиҝҷж„Ҹе‘ізқҖйңҖиҰҒдёӨдёӘж•°еӯ—йҡ”зҰ»еҷЁгҖӮж №жҚ®и·Ёи¶Ҡйҡ”зҰ»иҫ№з•Ңзҡ„ IO зҡ„йҮҸпјҢжӯӨзұ»еә”з”Ёзҡ„дәҢж¬Ўдҫ§жҺ§еҲ¶еҸҜиғҪеӯҳеңЁеҫҲеӨ§дәүи®®гҖӮеңЁиҝҷдёӘз®ҖеҢ–зӨәдҫӢдёӯпјҢIn+ е’Ң In-пјҲеҗҜз”ЁпјүжҳҜжқҘиҮӘж•°еӯ—жҺ§еҲ¶еҷЁзҡ„д»…жңүзҡ„дёӨдёӘдҝЎеҸ·пјҢXEN д»Һ NCP51705 иҜ»еҸ–гҖӮXEN еҸҜд»ҘдҪңдёәејҖеҸ‘ж …жһҒй©ұеҠЁж—¶еәҸгҖҒдәӨеҸүеҜјйҖҡйў„йҳІгҖҒжӯ»еҢәж—¶й—ҙи°ғж•ҙе’Ңж•…йҡңжЈҖжөӢзҡ„ж—¶еәҸдҝЎжҒҜеҹәзЎҖгҖӮжӯӨеӨ–пјҢжё©еәҰж„ҹжөӢгҖҒзғӯз®ЎзҗҶпјҲйЈҺжүҮжҺ§еҲ¶пјүе’Ңжӣҙй«ҳзә§еҲ«зҡ„ж•…йҡңе“Қеә”д№ҹеҸҜд»Ҙз”ұж•°еӯ—жҺ§еҲ¶еҷЁе®ҢжҲҗгҖӮNCP51705 зҡ„ V5V еҸҜз”ЁдәҺдёәжҜҸдёӘж•°еӯ—йҡ”зҰ»еҷЁзҡ„дәҢж¬Ўдҫ§дҫӣз”өпјҢеҰӮеӣҫ 50 жүҖзӨәгҖӮ

В

еӣҫ 50пјҡеҚҠжЎҘжҰӮеҝө

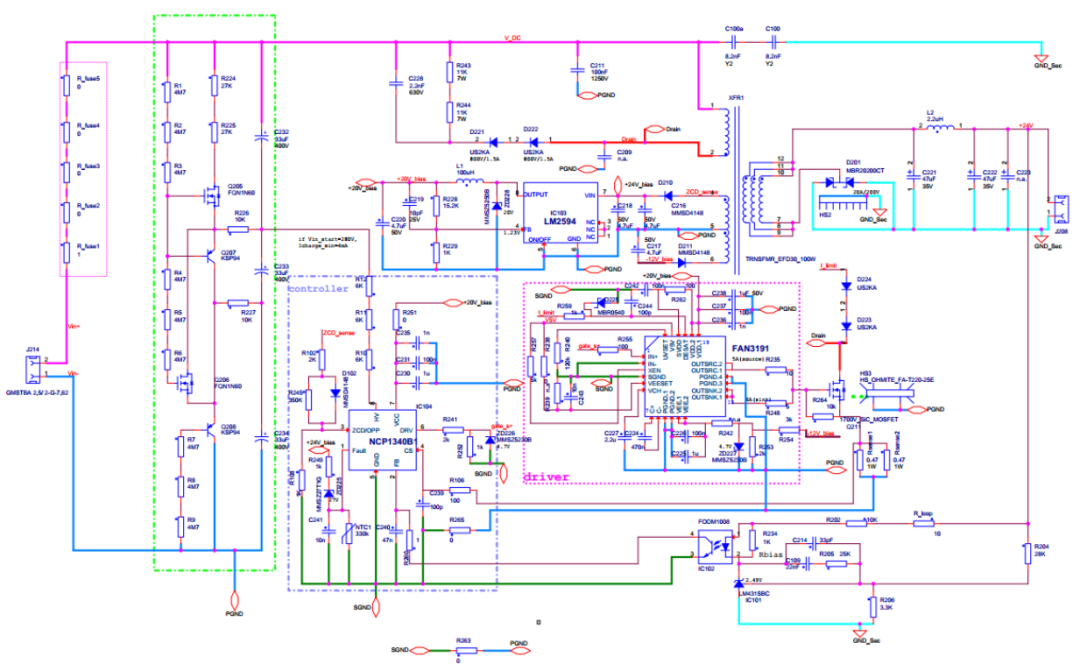

В3.еҮҶи°җжҢҜ (QR) еҸҚжҝҖејҸ

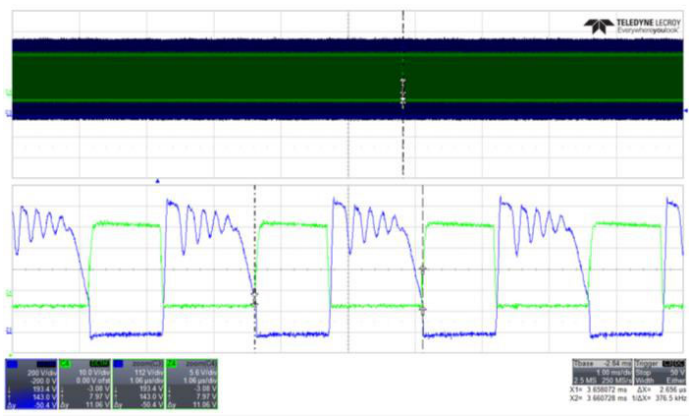

дҪҝз”Ё NCP1340B1 жҺ§еҲ¶еҷЁе’Ң NCP51705 SiC й©ұеҠЁеҷЁи®ҫи®ЎдәҶдёҖдёӘ 100вҲ’W зҡ„ QR еҸҚжҝҖејҸиҪ¬жҚўеҷЁпјҢеҸҜеңЁ 300 V < VIN< 1 kV зҡ„е®Ҫиҫ“е…ҘиҢғеӣҙеҶ…е·ҘдҪңгҖӮжӯӨзұ»иҪ¬жҚўеҷЁеёёи§ҒдәҺе…үдјҸе’Ңе·Ҙдёҡеә”з”ЁпјҢдҪҶеҪ“еҹәдәҺ IGBT еҠҹзҺҮзә§ж—¶пјҢејҖе…ійў‘зҺҮеңЁ 65 kHz зҡ„иҢғеӣҙеҶ…гҖӮеӣҫ 51 жүҖзӨәзҡ„зӨәж„Ҹеӣҫдёә QR еҸҚжҝҖејҸпјҢеңЁ VIN = 300 V ж—¶пјҢйў‘зҺҮеңЁ 377 kHz < FS < 430 kHz д№Ӣй—ҙеҸҳеҢ–пјҢиҙҹиҪҪд»Һ 100% еҲ° 25% дёҚзӯүгҖӮ

еӣҫ 51пјҡ1000 V иҮі 24 VгҖҒ100 WгҖҒ400 kHzгҖҒQR еҸҚжҝҖејҸ

В4.QR еҸҚжҝҖејҸ

еҜ№дәҺ VIN= 300 VпјҢжјҸжһҒ-жәҗжһҒз”өеҺӢжіўеҪўжҳҜиҫ“е…Ҙз”өеҺӢе’ҢеҸҚе°„иҫ“еҮәз”өеҺӢд№Ӣе’ҢгҖӮеӣҫ 52 жүҖзӨәзҡ„жіўеҪўзӘҒеҮәжҳҫзӨәдәҶеңЁе…ЁеҚ з©әжҜ”ж“ҚдҪң (VIN= 300 V) дёӢиҝҗиЎҢзҡ„иҪ¬жҚўеҷЁпјҢе…¶дёӯ 720 V еҮәзҺ°еңЁ SiC MOSFET зҡ„жјҸжһҒ-жәҗжһҒдёҠгҖӮVDS дёҠеҚҮиҝҮжёЎзәҰдёә 30 nsпјҢзӣёеҪ“дәҺ dVDS/dt = 24 V/nsгҖӮNCP1340B1 QR жҺ§еҲ¶еңЁ VDS дёӢйҷҚжІҝе®һзҺ°иҪҜи°җжҢҜиҝҮжёЎе’Ңи°·еҖјејҖе…іпјҲеңЁжңҖе°Ҹ VDS и°җжҢҜж—¶вҖңжҺҘиҝ‘ ZVSвҖқеҜјйҖҡпјүпјҢиҝҷеңЁи“қиүІжіўеҪўдёҠжё…жҷ°еҸҜи§ҒгҖӮз”ұдәҺ QR еҸҚжҝҖејҸжҳҜд»…йҷҗдҪҺеҺӢдҫ§зҡ„еә”з”ЁпјҢ并且 dVDS/dt дёӢйҷҚжІҝдёәи°җжҢҜпјҢеӣ жӯӨ SiC MOSFET еҸҜиғҪеңЁ 0 V < VGS < 20 V д№Ӣй—ҙеҸҜйқ еҲҮжҚўгҖӮе°Ҫз®ЎеҰӮжӯӨпјҢеӣҫ 51 жүҖзӨәзҡ„и®ҫи®ЎйҖүжӢ©еңЁ вҲ’5 V < VGS < 20 V д№Ӣй—ҙеҲҮжҚўпјҢд»ҺиҖҢеңЁеўһеҠ ж …жһҒз”өиҚ·зҡ„иҪ»еҫ®д»Јд»·дёӢпјҢе®һзҺ°жӣҙзЁіеҒҘзҡ„еҲҮжҚўгҖӮ

В

еӣҫ 52пјҡCH3 = VDSпјҢCH4 = VGSпјӣVIN = 300 VпјҢVOUT = 24 VпјҢIOUT = 4 AпјҢFS = 377 kHz

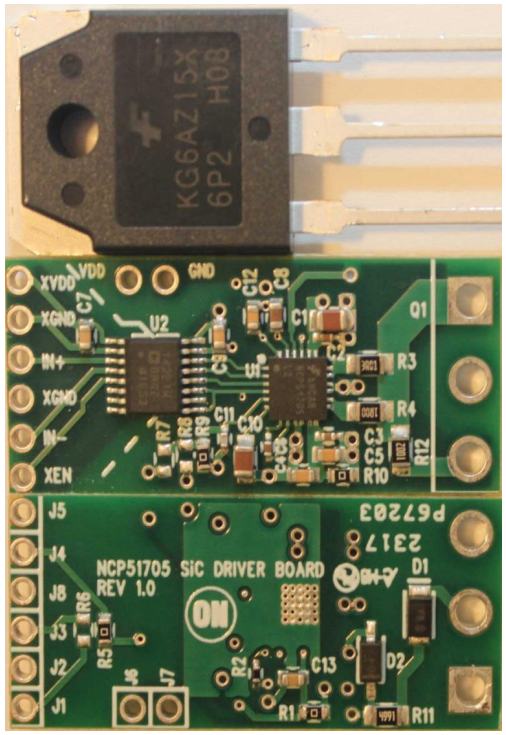

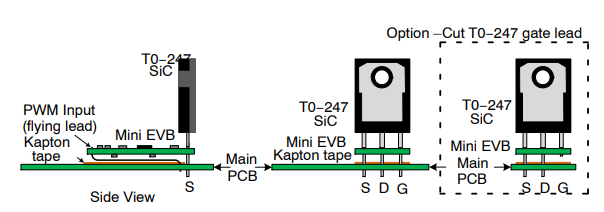

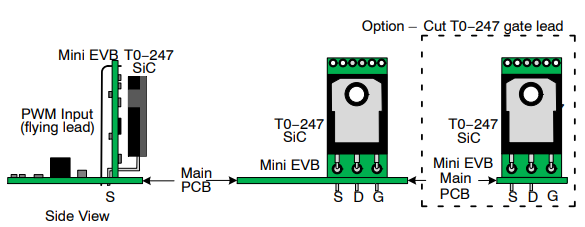

В йҖҡз”Ё NCP5170 е®ўжҲ· EVBйҖҡз”ЁиҜ„дј°жқҝ (EVB) ж—ЁеңЁиҜ„дј° NCP51705 еңЁж–°и®ҫи®ЎжҲ–зҺ°жңүи®ҫи®Ўдёӯзҡ„жҖ§иғҪгҖӮEVB дёҚеҢ…жӢ¬еҠҹзҺҮзә§пјҢдёҚдё“з”ЁдәҺд»»дҪ•зү№е®ҡжӢ“жү‘пјҢз”ұжӯӨеҸҜи§Ғе®ғжҳҜйҖҡз”Ёзҡ„гҖӮе®ғеҸҜз”ЁдәҺд»»дҪ•дҪҺеҺӢдҫ§жҲ–й«ҳеҺӢдҫ§з”өжәҗејҖе…іеә”з”ЁгҖӮеҜ№дәҺжЎҘжҺҘй…ҚзҪ®пјҢеҸҜд»ҘеңЁеӣҫи…ҫжҹұеһӢй©ұеҠЁй…ҚзҪ®дёӯзҡ„жҜҸдёӘ SiC MOSFET еӨ„дҪҝз”Ёиҝҷдәӣ EVB дёӯзҡ„дёӨдёӘжҲ–д»ҘдёҠгҖӮEVB еҸҜиў«и§Ҷдёәйҡ”зҰ»еҷЁ + й©ұеҠЁеҷЁ + TOвҲ’247 еҲҶз«ӢжЁЎеқ—гҖӮEVB зӨәж„ҸеӣҫеҰӮеӣҫ 53 жүҖзӨәгҖӮ

ВйҮҚзӮ№жҳҜжҸҗдҫӣдёҖз§Қи¶…зҙ§еҮ‘зҡ„и®ҫи®ЎпјҢе…¶дёӯ TOвҲ’247 SiC MOSFET зҡ„еј•зәҝеҸҜд»ҘзӣҙжҺҘиҝһжҺҘеҲ°еҚ°еҲ·з”өи·Ҝжқҝ (PCB)гҖӮеӣҫ 54 еҗҢж—¶жҳҫзӨәдәҶзӣёйӮ» TOвҲ’247 е°ҒиЈ…ж—Ғиҫ№зҡ„ EVB зҡ„йЎ¶и§Ҷеӣҫе’Ңеә•и§ҶеӣҫиҝӣиЎҢе°әеҜёзј©ж”ҫгҖӮ

еӣҫ 53пјҡNCP5170 Mini EVB зӨәж„Ҹеӣҫ

еӣҫ 54пјҡNCP5170 Mini EVB вҖ“ йЎ¶и§Ҷеӣҫ (35 mm x 15 mm)

В

еҪ“е®үиЈ…еҲ°зҺ°жңүз”өжәҗи®ҫи®ЎдёӯпјҢ并且 TOвҲ’247 еүҚйқўжңүеҸҜз”Ёзҡ„ PCB еҢәеҹҹж—¶пјҢEVB еҸҜд»Ҙж°ҙе№іе®үиЈ…еҲ°дё»з”өжәҗжқҝдёҠпјҢеҰӮеӣҫ 55 жүҖзӨәгҖӮеҰӮжһңеҸҜиғҪпјҢиҝҷеә”иҜҘжҳҜйҰ–йҖүзҡ„е®үиЈ…ж–№жі•гҖӮ

еӣҫ 55пјҡж°ҙе№і EVB е®үиЈ…

ВеҰӮжһңдё»з”өжәҗжқҝдёҠзҡ„еӨ§еһӢ组件еҰЁзўҚж°ҙе№іе®үиЈ…пјҢеҲҷ第дәҢз§ҚйҖүжӢ©жҳҜеһӮзӣҙе®үиЈ… EVBпјҢдҪҝе…¶дёҺ T0вҲ’247 е°ҒиЈ…е№іиЎҢжҲ–з•Ҙеҫ®еҖҫж–ңгҖӮз”ұдәҺй©ұеҠЁеҷЁдёҺ TOвҲ’247 жјҸжһҒжҺҘеӨҙеҸ‘еҮәзҡ„й«ҳ dV/dt йқһеёёжҺҘиҝ‘пјҢеӣ жӯӨдёҚеӨӘеҖҫеҗ‘дәҺйҮҮз”Ёиҝҷз§Қж–№ејҸе®үиЈ…гҖӮеңЁд»»дҪ•дёҖз§Қжғ…еҶөдёӢпјҢTOвҲ’247 е°ҒиЈ…зҡ„еҗҺжҺҘеӨҙйғҪдҝқжҢҒжҡҙйңІзҠ¶жҖҒпјҢеҰӮжңүеҝ…иҰҒпјҢеҸҜе°Ҷе…¶иҝһжҺҘеҲ°ж•ЈзғӯеҷЁдёҠгҖӮжңүе…іе®үиЈ…е’Ңж“ҚдҪңиҜҰз»ҶдҝЎжҒҜпјҢиҜ·еҸӮи§Ғ EVB з”ЁжҲ·жҢҮеҚ—гҖӮ

еӣҫ 56пјҡеһӮзӣҙ EVB е®үиЈ…

еӣҫ 56пјҡеһӮзӣҙ EVB е®үиЈ…

EVB жңҖеҲқй…ҚзҪ®дёәжҺҘеҸ—жӯЈиҫ“е…ҘйҖ»иҫ‘зҡ„ PWM дҝЎеҸ·пјҲиҝһжҺҘеҲ° GND1 зҡ„ INвҲ’пјүгҖӮдҪҶеҰӮжһңйңҖиҰҒпјҢINвҲ’ еҸҜиҪ»жқҫз”ЁдҪңдё»еҠЁеҗҜз”ЁжҲ–йҮҚж–°й…ҚзҪ®дёәеҸҚзӣёиҫ“е…ҘйҖ»иҫ‘гҖӮй©ұеҠЁеҷЁиҫ“еҮәйў„й…ҚзҪ®дёә 0 V < VOUT < VDD ејҖе…ігҖӮжүҖжңүиҝһжҺҘе’Ңз”өйҳ»еҷЁеҚ дҪҚз¬ҰйғҪеҸҜз”ЁдәҺдёә вҲ’3 VгҖҒвҲ’5 V жҲ– вҲ’8 V VEEејҖе…ійҮҚж–°й…ҚзҪ® VEESETгҖӮжңҖеҗҺпјҢUVSET йҖүйЎ№иў«йў„зј–зЁӢдёә 17вҲ’V еҜјйҖҡж“ҚдҪңпјҢиҝҷиў«и®ӨдёәжҳҜ SiC MOSFET зҡ„е®үе…Ёзә§еҲ«гҖӮ

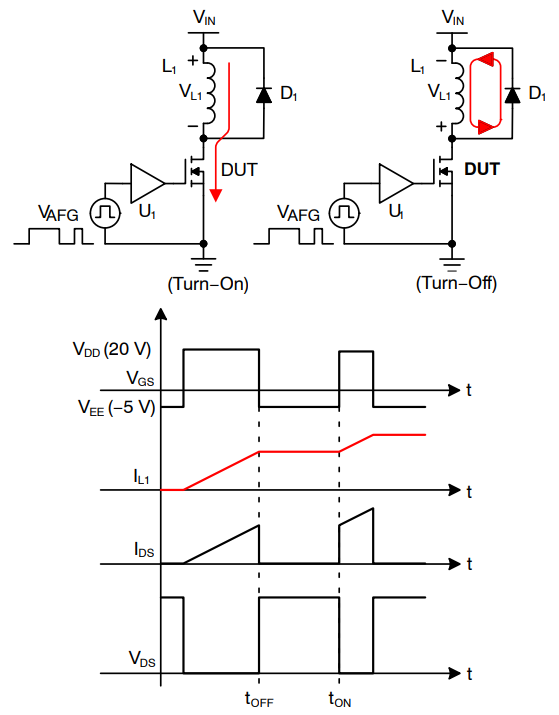

В еҸӮж•°жҖ§иғҪдҪҝз”Ёдј—жүҖе‘ЁзҹҘзҡ„еҸҢи„үеҶІжөӢиҜ•е№іеҸ°еҜ№ MOSFET е’Ң IGBT иҝӣиЎҢеҸӮж•°еҢ–иЎЁеҫҒгҖӮеҸҢи„үеҶІжөӢиҜ•ж–№жі•еҹәжң¬дјҡеҗ‘иў«жөӢеҷЁд»¶ (DUT) дҪҺеҺӢдҫ§ SiC MOSFET зҡ„ж …жһҒ-жәҗжһҒж–ҪеҠ дёӨдёӘи„үеҶІгҖӮDUT иў«жҸ’е…ҘеҲ°дёҺеӣҫ 57 жүҖзӨәзҡ„й’ідҪҚз”өж„ҹејҖе…із”өи·Ҝзӣёиҝһзҡ„жҸ’еә§дёӯгҖӮ

еӣҫ 57пјҡеҸҢи„үеҶІжөӢиҜ•з”өи·Ҝе’ҢжіўеҪў

Ви°ғж•ҙ第дёҖдёӘи„үеҶІзҡ„еҜјйҖҡж—¶й—ҙпјҢд»ҘиҺ·еҫ—жүҖйңҖзҡ„еі°еҖјжјҸжһҒ-жәҗжһҒз”өжөҒгҖӮз”өж„ҹеҷЁеҫҲеӨ§пјҢе…іж–ӯж—¶й—ҙи¶іеӨҹзҹӯпјҢеӣ жӯӨ IL1 еңЁе…іж–ӯз»ӯжөҒжңҹй—ҙеҮ д№ҺдҝқжҢҒжҒ’е®ҡгҖӮеӣ жӯӨпјҢ第дәҢдёӘжӣҙзҹӯзҡ„и„үеҶІд»ҘзӣёеҗҢзҡ„жјҸжһҒ-жәҗжһҒз”өжөҒе№…еәҰж–ҪеҠ гҖӮиҜҘжөӢиҜ•ж–№жі•еҸҜзІҫзЎ®жҺ§еҲ¶ ID е’Ң VDSпјҢиҝҷжҳҜе»әз«ӢеҠЁжҖҒејҖе…ігҖҒеҸӮж•°жҖ§иғҪд»ҘеҸҠеҜ№еҷЁд»¶иҝӣиЎҢеҹәеҮҶжөӢиҜ•жүҖеҝ…йңҖзҡ„гҖӮ

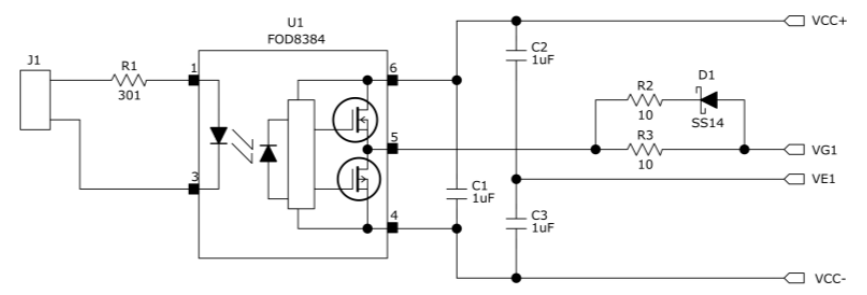

ВеҸҢи„үеҶІжөӢиҜ•ж–№жі•д№ҹеҸҜз”ЁдәҺиЎЁеҫҒж …жһҒй©ұеҠЁеҷЁжҖ§иғҪгҖӮеңЁ SiCгҖҒDUT еӣәе®ҡзҡ„жғ…еҶөдёӢпјҢеҪ“ U1 жҲҗдёәж–°зҡ„вҖңDUTвҖқж—¶пјҢеҸҜд»ҘеҜ№еҗ„з§Қж …жһҒй©ұеҠЁз”өи·ҜиҝӣиЎҢиЎЁеҫҒгҖӮеңЁеӣҫ 53 е’Ңеӣҫ 54 жүҖзӨәзҡ„ NCP5170 EVB е’Ңеӣҫ 58 жүҖзӨәзҡ„з®ҖеҚ•е…үиҖҰеҗҲеҷЁж …жһҒй©ұеҠЁз”өи·Ҝд№Ӣй—ҙпјҢеҜ№ dV/dt е’Ң dI/dt ејҖе…іжҖ§иғҪиҝӣиЎҢдәҶжҜ”иҫғгҖӮ

еӣҫ 58пјҡFOD8384 SiC е…үиҖҰеҗҲеҷЁж …жһҒй©ұеҠЁз”өи·Ҝ

ВFOD8384 е…үиҖҰеҗҲеҷЁй©ұеҠЁеҷЁиғҪеӨҹжүҝеҸ—й«ҳиҫҫ 30 V зҡ„ VDD еҒҸеҺӢпјҢеӣ жӯӨйқһеёёйҖӮеҗҲвҲ’5 V < VGS< 20 V ејҖе…ігҖӮдёҺеӣҫ 58 дёӯзҡ„зӨәдҫӢзұ»дјјпјҢFOD8384 й©ұеҠЁеҷЁдёҚжҳҜе®Ңж•ҙзҡ„ SiC MOSFET ж …жһҒй©ұеҠЁз”өи·ҜгҖӮеӣ жӯӨпјҢз”ұдәҺдёӨз§Қз”өи·Ҝзҡ„зү№жҖ§жІЎжңүеҸҜжҜ”жҖ§пјҢжөӢиҜ•з»“жһңе’ҢжҜ”иҫғд»…йҷҗдәҺеҠЁжҖҒејҖе…ігҖӮ

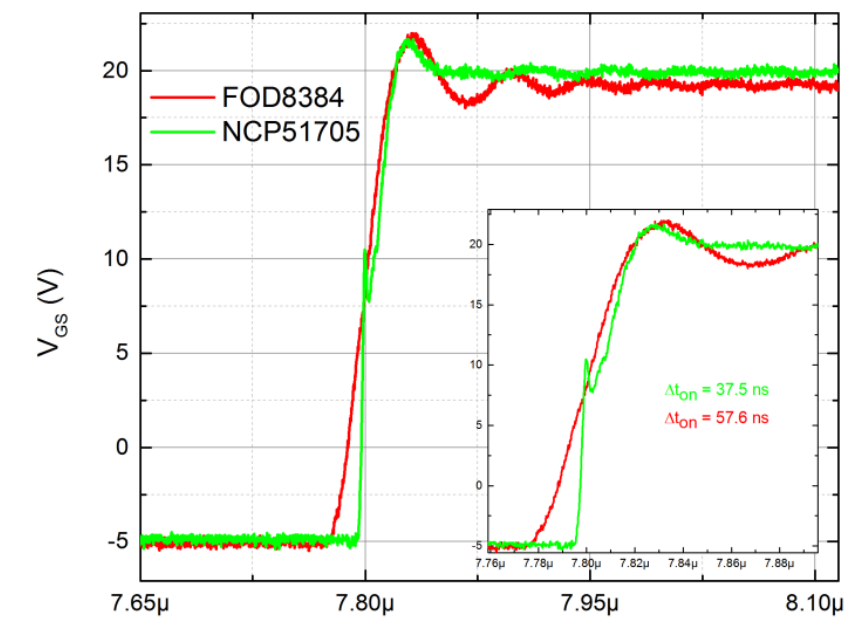

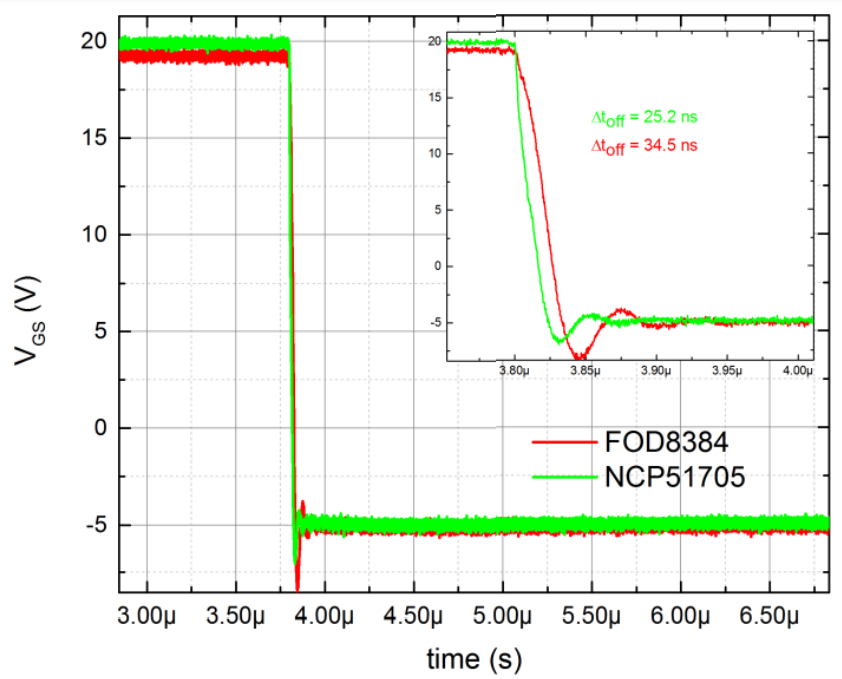

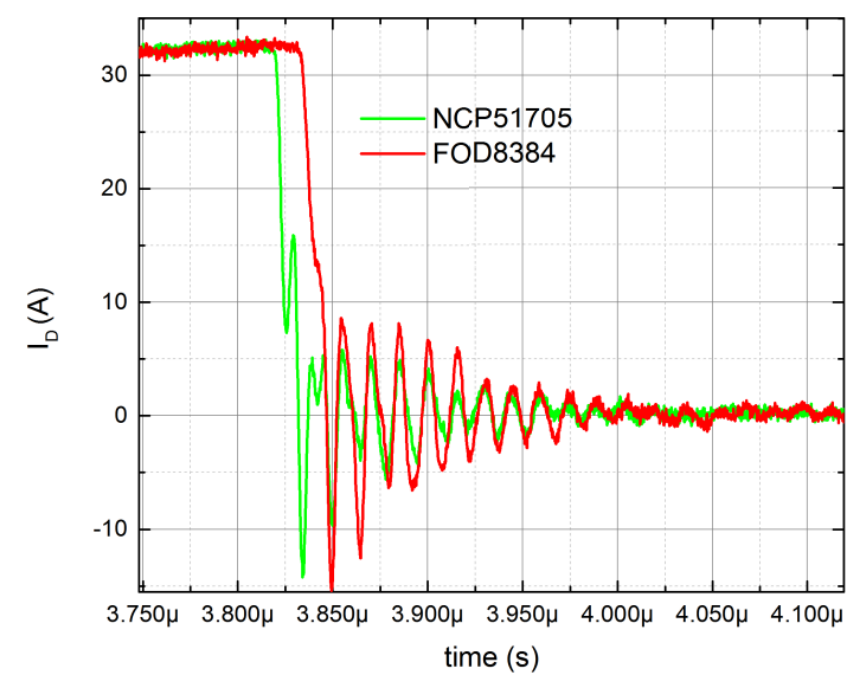

Веӣҫ 59 е’Ңеӣҫ 60 еҲҶеҲ«жҳҫзӨәдәҶдёӨз§Қз”өи·Ҝзҡ„дёҠеҚҮе’ҢдёӢйҷҚ VGS жіўеҪўпјҢд»ҘдҫӣжҜ”иҫғгҖӮдёӨз§Қз”өи·ҜйғҪдҪҝз”ЁдәҶ 1 О© зҡ„жәҗжһҒе’ҢжјҸжһҒж …жһҒз”өйҳ»гҖӮиҝҷдәӣж …жһҒй©ұеҠЁиҫ№зјҳиў«жҳҫзӨәдёәй©ұеҠЁ 1.2 kVгҖҒSiC MOSFETпјҢVDS дёҠжҳҫзӨә 600 VпјҢжөҒиҝҮ ID зҡ„з”өжөҒдёә 30 AгҖӮNCP51705гҖҒVGS дёҠеҚҮжІҝеңЁ вҲ’5 V < VGS < 10 V ж—¶иЎЁзҺ°дёәзәҜз”өйҳ»пјҢ然еҗҺеңЁ 10 V < VGS < 20 V ж—¶дёәз”өе®№жҖ§ RC е……з”өгҖӮиҝҷжҳҫзӨәдәҶ NCP51705гҖҒ6 APK зҡ„жәҗз”өжөҒдёҺ FOD8384 зҡ„ 1 APK жәҗз”өжөҒзҡ„жҜ”иҫғжғ…еҶөгҖӮNCP51705 зҡ„ VGS дёҠеҚҮж—¶й—ҙдёә 37.5 nsпјҢиҖҢ FOD8384 ејҖе…іеңЁзӣёеҗҢжөӢиҜ•жқЎд»¶дёӢеҲҷдёә 57.6 nsгҖӮеҗҢж ·пјҢNCP51705 зҡ„ VGS дёӢйҷҚж—¶й—ҙдёә 25.2 nsпјҢиҖҢ FOD8384 еҲҷдёә 34.5 nsгҖӮ

еӣҫ 59пјҡVGS дёҠеҚҮжІҝжҜ”иҫғ

еӣҫ 60пјҡVGS дёӢйҷҚжІҝжҜ”иҫғ

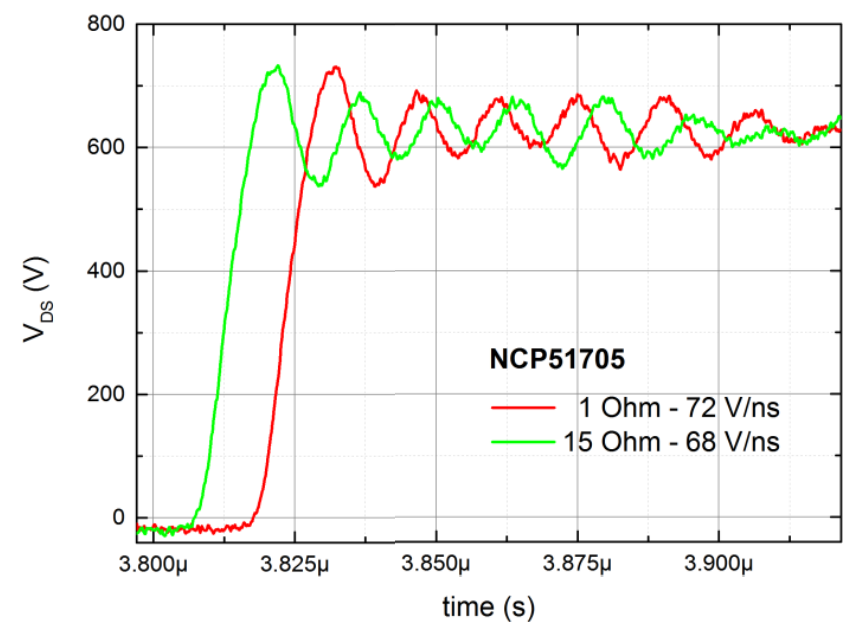

Ви®ҫи®ЎиүҜеҘҪзҡ„ж …жһҒй©ұеҠЁеҷЁ IC еҢ…жӢ¬дҪҺжәҗжһҒе’ҢжјҸжһҒйҳ»жҠ—пјҢдҪҝеҫ— SiC MOSFET жјҸжһҒеҸҜд»Ҙз”ұж …жһҒзІҫзЎ®жҺ§еҲ¶гҖӮе…¶ж¬ЎпјҢжңҖеӨ§йҷҗеәҰең°йҷҚдҪҺй©ұеҠЁеҷЁиҫ“еҮәйҳ»жҠ—еҜ№дәҺе…Ғи®ё SiC MOSFET иҫҫеҲ°жңҖй«ҳиҮӘ然 dV/dt иҮіе…ійҮҚиҰҒгҖӮSiC MOSFET зҡ„иҮӘ然 dV/dt йҷҗеҖјдёҺ RLO + RGATE + RGI жҲҗеҸҚжҜ”гҖӮеҪ“ RLO й«ҳдәҺеҝ…иҰҒеҖјж—¶пјҢSiC MOSFET зҡ„иҮӘ然 dV/dt йҷҗеҖјйҷҚдҪҺгҖӮиҝҷдҪҝеҫ—еҷЁд»¶жӣҙе®№жҳ“еҸ—еҲ° dV/dt еј•иө·зҡ„еҜјйҖҡзҡ„еҪұе“ҚпјҢ并йҷҗеҲ¶дәҶйҖҡиҝҮйҖүжӢ© RGATE еҸҜд»Ҙе®һзҺ°зҡ„ dVDS/dt жҺ§еҲ¶йҮҸгҖӮеӣҫ 61 жүҖзӨәзҡ„ NCP51705 VDS жіўеҪўжҸӯзӨәдәҶж”№еҸҳ RGATE еҚіеҸҜе®һзҺ°зҡ„й«ҳеәҰ dVDS/dt жҺ§еҲ¶гҖӮеҜ№дәҺ RGATE = 1 О©пјҢdVDS/dt = 72 V/nsгҖӮе°Ҷ RGATE д»Һ 1 О© еўһеҠ еҲ° 15 О© дјҡдҪҝ dVDS/dt д»Һ 72 V/ns йҷҚдҪҺеҲ° 68 V/nsгҖӮиҝҷиЎЁжҳҺпјҢеҰӮжһңйңҖиҰҒпјҢеҸҜд»ҘдҪҝз”Ёй«ҳеҫ—еӨҡзҡ„ RGATE жқҘйҖҗжӯҘйҷҚдҪҺ dVDS/dtгҖӮ

еӣҫ 61пјҡNCP51705 VDS дёҠеҚҮжІҝпјҢеҸҜеҸҳж …жһҒз”өйҳ»

В

дҪҝз”Ё FOD8384 е…үиҖҰеҗҲеҷЁж …жһҒй©ұеҠЁеҷЁе®ҢжҲҗдәҶзӣёеҗҢзҡ„е®һйӘҢгҖӮд»Һеӣҫ 62 жүҖзӨәзҡ„жіўеҪўдёӯеҸ‘зҺ°пјҢRGATE д»Һ 1 О© еҸҳжҲҗ 15 О© еҜјиҮҙ dVDS/dt йҖҹзҺҮеҸҳеҢ–и¶…иҝҮ 2:1гҖӮз”ұдәҺ FOD8384 й©ұеҠЁеҷЁиҫ“еҮәйҳ»жҠ—жӣҙй«ҳпјҢdVDS/dt жҺ§еҲ¶жӣҙеҸ— RGATE иҫғе°ҸеҸҳеҢ–зҡ„еҪұе“ҚгҖӮжӯӨеӨ–пјҢиҜ·жіЁж„ҸпјҢNCP51705 зҡ„ dVDS/dt дёҠеҚҮзӣёеҜ№иҖҢиЁҖжӣҙдёәзәҝжҖ§гҖӮ

еӣҫ 62пјҡFOD8384 VDS дёҠеҚҮжІҝпјҢеҸҜеҸҳж …жһҒз”өйҳ»

В

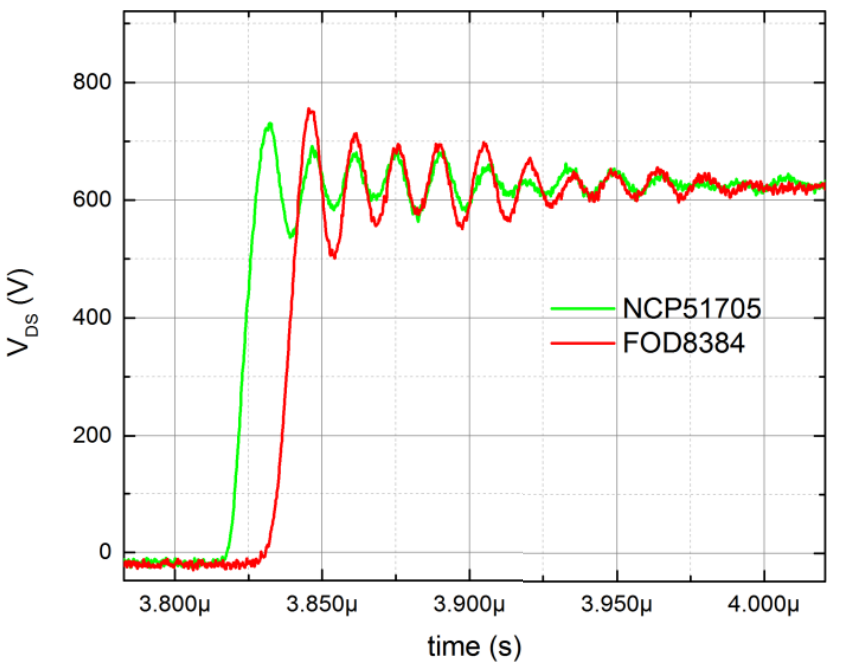

еӣҫ 63 жүҖзӨәзҡ„жіўеҪўжҜ”иҫғдәҶеңЁ RGATE = 1 О© зҡ„жғ…еҶөдёӢпјҢд»Һ вҲ’5 V < VGS < 20 V еҲҮжҚўзӣёеҗҢиҙҹиҪҪзҡ„жҜҸдёӘй©ұеҠЁеҷЁзҡ„ VDSгҖӮdVDS/dt йҖҹзҺҮеңЁ 72 V/ns дёҺ 64 V/ns ж—¶иЎЁзҺ°зӣёеҪ“гҖӮNCP51705 иЎЁзҺ°еҮәжӣҙеҘҪзҡ„йҳ»е°је’ҢжӣҙдҪҺжҢҜе№…зҡ„жҢҜй“ғгҖӮ

еӣҫ 63пјҡVDS дёҠеҚҮжІҝжҜ”иҫғпјҢ1 О© ж …жһҒз”өйҳ»

В

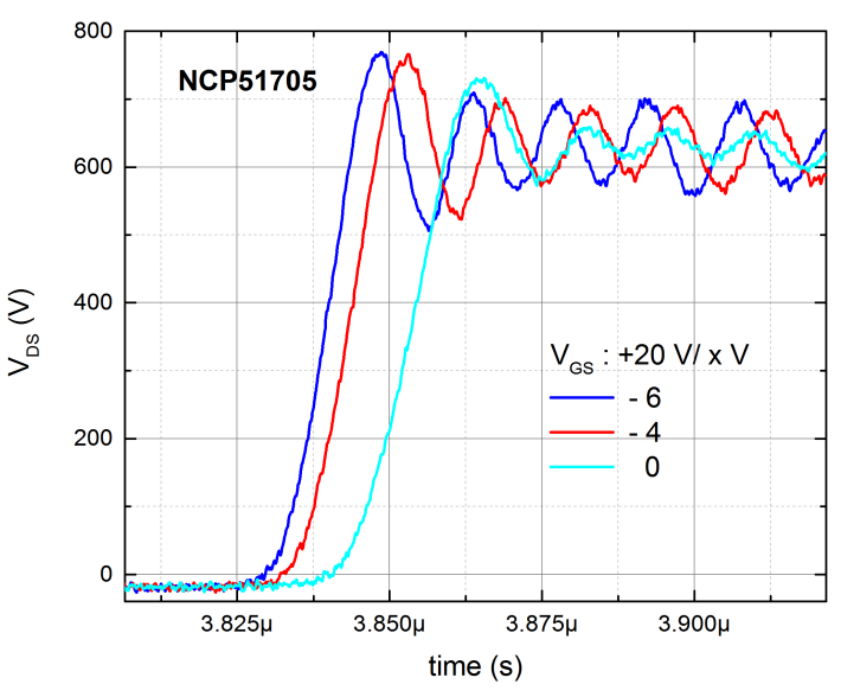

NCP51705 е®һзҺ° dVDS/dt жҺ§еҲ¶зҡ„еҸҰдёҖз§Қж–№ејҸжҳҜйҖҡиҝҮж”№еҸҳ VEE зҡ„иҙҹжҢҜе№…з”өе№ігҖӮиҝҷеҸҜд»ҘйҖҡиҝҮж №жҚ®иЎЁ 2 й…ҚзҪ® VEESET еј•и„ҡжҲ–дҪҝз”Ёж–ҪеҠ еҲ° VEE зҡ„еӨ–йғЁиҙҹ DC з”өжәҗжқҘе®һзҺ°гҖӮеӣҫ 64 дёӯзҡ„жіўеҪўжҳҫзӨәдәҶеҪ“ VEE еңЁ вҲ’6 V < VEE < 0 V д№Ӣй—ҙеҸҳеҢ–ж—¶ dVDS/dt зҡ„еҸҳеҢ–гҖӮиҜ·жіЁж„ҸеңЁ 0 V < VGS < 20 V ж—¶дҪҺ VDS дёӢзҡ„ејәжӢҗзӮ№е’Ңз”өе®№зү№жҖ§гҖӮиҝҷжҳҜеӣ дёә SiC MOSFET зҡ„дёҖдәӣеү©дҪҷж …жһҒз”өиҚ·жІЎжңүе®Ңе…Ёе…іж–ӯпјҢ并зӘҒеҮәдәҶеңЁе…іж–ӯжңҹй—ҙй©ұеҠЁ VGS иҙҹжһҒзҡ„йҮҚиҰҒжҖ§гҖӮ

еӣҫ 64пјҡNCP51705 VDS дёҠеҚҮжІҝпјҢеҸҜеҸҳ VEE

В

еӣҫ 65 жүҖзӨәзҡ„жјҸжһҒз”өжөҒжөӢйҮҸжҳҜдҪҝз”Ё Pearson з”өжөҒжҺўеӨҙиҝӣиЎҢзҡ„гҖӮNCP51705 з”өжөҒеңЁ dID/dt = 3.2 A/ns ж—¶дёӢйҷҚпјҢдҪҶдёҺ FOD8384 й©ұеҠЁз”өи·ҜзӣёжҜ”пјҢиЎЁзҺ°еҮәзҡ„жҢҜй“ғиҫғе°‘гҖӮNCP51705 жӣҙеҝ«зҡ„ dID/dt дёҺеӣҫ 60 жүҖзӨәзҡ„ VGS дёӢйҷҚжІҝжіўеҪўеҜҶеҲҮзӣёе…ігҖӮ

еӣҫ 65пјҡID дёӢйҷҚжІҝжҜ”иҫғ

ВеҸҢи„үеҶІжөӢиҜ•ж–№жі•жҳҜдј з»ҹдёҠз”ЁдәҺиЎЁеҫҒеҲҶз«ӢеҠҹзҺҮеҚҠеҜјдҪ“еҷЁд»¶зҡ„еҠЁжҖҒејҖе…іжҖ§иғҪзҡ„жөӢиҜ•зЁӢеәҸгҖӮз”ұдәҺеңЁеҜјйҖҡе’Ңе…іж–ӯжңҹй—ҙеҸҜд»ҘзІҫзЎ®жҺ§еҲ¶ж–ҪеҠ зҡ„ VDS е’ҢеҲқе§Ӣ IDпјҢиҜҘжөӢйҮҸжҠҖжңҜе·Іиў«иҜҒжҳҺжҳҜиЎЁеҫҒз®қдҪҚз”өж„ҹејҖе…іеә”з”Ёз”өи·Ҝдёӯж …жһҒй©ұеҠЁеҷЁ IC жҖ§иғҪзҡ„еҸҜйқ ж–№жі•гҖӮ

еҺҹзүҲж–ҮжЎЈиҺ·еҸ–зӮ№еҮ»ж–Үжң«зҡ„вҖңиөһвҖқе’ҢвҖңеңЁзңӢвҖқпјҢ并еҸ‘йҖҒжҲӘеӣҫе’ҢжӮЁзҡ„йӮ®з®ұең°еқҖеҲ°еҗҺеҸ°пјҢеҚіеҸҜйўҶеҸ–еҺҹзүҲж–ҮжЎЈе“Ұ~

В В В

В

еҺҹж–Үж Үйўҳпјҡз”ЁдәҺ SiC MOSFET зҡ„йҡ”зҰ»ж …жһҒй©ұеҠЁеҷЁдҪҝз”ЁжҢҮеҚ—

ж–Үз« еҮәеӨ„пјҡгҖҗеҫ®дҝЎе…¬дј—еҸ·пјҡе®үжЈ®зҫҺгҖ‘ж¬ўиҝҺж·»еҠ е…іжіЁпјҒж–Үз« иҪ¬иҪҪиҜ·жіЁжҳҺеҮәеӨ„гҖӮ

- зӣёе…іжҺЁиҚҗ

- зғӯзӮ№жҺЁиҚҗ

- е

-

жұҪиҪҰзұ»еҸҢйҖҡйҒ“SiC MOSFETж …жһҒй©ұеҠЁеҷЁеҢ…жӢ¬BOMеҸҠеұӮеӣҫ2018-10-16 2913

-

дҪҝз”Ёйҡ”зҰ»ејҸIGBTе’ҢSiCж …жһҒй©ұеҠЁеҷЁзҡ„HEV/EVзүөеј•йҖҶеҸҳеҷЁи®ҫи®ЎжҢҮеҚ—2022-11-02 16824

-

йқўеҗ‘SiC MOSFETзҡ„STGAP2SICSNйҡ”зҰ»ејҸеҚ•йҖҡйҒ“ж …жһҒй©ұеҠЁ2023-09-05 871

-

жңҖе®һз”Ёзҡ„ж …жһҒй©ұеҠЁиҠҜзүҮйҖүеһӢжҢҮеҚ—2019-01-29 30858

-

ADIйҡ”зҰ»ж …жһҒй©ұеҠЁеҷЁе’ҢWOLFSPEED SiC MOSFET2021-05-27 1543

-

з”ЁдәҺSiC MOSFETзҡ„ж …жһҒй©ұеҠЁеҷЁ2022-08-03 2921

-

дҪҝз”Ёйҡ”зҰ»ејҸж …жһҒй©ұеҠЁеҷЁзҡ„е®һз”Ёи®ҫи®ЎжҢҮеҚ—2022-11-14 878

-

дҝқе§Ҷзә§ж”»з•Ҙ | дҪҝз”Ёйҡ”зҰ»ејҸж …жһҒй©ұеҠЁеҷЁзҡ„и®ҫи®ЎжҢҮеҚ—пјҲдёҖпјү2023-02-05 2243

-

дҪҝз”Ёйҡ”зҰ»ејҸж …жһҒй©ұеҠЁеҷЁзҡ„и®ҫи®ЎжҢҮеҚ—пјҲдёҖпјү2023-11-28 1744

-

йҡ”зҰ»ејҸж …жһҒй©ұеҠЁеҷЁзҡ„жј”еҸҳпјҲIGBT/SiC/GaNпјү2023-12-18 1153

-

дҪҝз”Ёйҡ”зҰ»ејҸ IGBT е’Ң SiC ж …жһҒй©ұеҠЁеҷЁзҡ„ HEV/EV зүөеј•йҖҶеҸҳеҷЁи®ҫи®ЎжҢҮеҚ—2024-09-11 541

-

з”өйҡ”зҰ»ж …жһҒй©ұеҠЁеҷЁйҖүеһӢжҢҮеҚ—2024-11-11 1852

-

йҮҮз”Ё LLC жӢ“жү‘з»“жһ„и®ҫи®Ўйҡ”зҰ»ејҸж …жһҒй©ұеҠЁеҷЁз”өжәҗ,дҪҺжҲҗжң¬ LLC иҪ¬жҚўеҷЁзҡ„и®ҫи®ЎжҢҮеҚ—2025-01-08 3087

-

UCC21737-Q1 жұҪиҪҰзә§SiC/IGBTйҡ”зҰ»ж …жһҒй©ұеҠЁеҷЁжҠҖжңҜи§Јжһҗ2025-09-09 1223

-

з”ЁдәҺSiC MOSFETзҡ„еёҰеҸҜй…ҚзҪ®жө®еҠЁеҸҢжһҒжҖ§иҫ…еҠ©з”өжәҗзҡ„йҡ”зҰ»ж …жһҒй©ұеҠЁIC2025-12-19 581

е…ЁйғЁ0жқЎиҜ„и®ә

еҝ«жқҘеҸ‘иЎЁдёҖдёӢдҪ зҡ„иҜ„и®әеҗ§ !