电平设计基础:电平匹配设计

电子说

描述

一,单端逻辑电平匹配

单端逻辑电平的匹配是我们平时在硬件设计中最经常碰到的,我们在《TTL&CMOS电平》章节中已经对TTL和COMS电平的匹配设计做了一些分析,一般3.3V LVTTL和LVCMOS是可以直接相互驱动的。但是其它不同逻辑电平之间呢?举个栗子,3.3V逻辑电平和1.8V逻辑电平之间呢?

1,门电路电平匹配方案

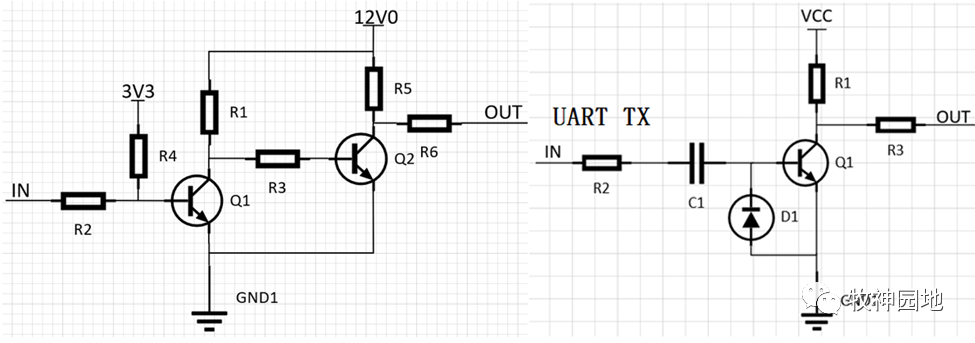

如下图所示,利用三极管/MOS管搭建不同电平之间的电路匹配;

- 如果输入/输出侧接至CPLD/FPGA等逻辑器件的话,可以只用1个三极管/MOS管来实现电平的转换,但是此时逻辑上是取“非”的关系,需要在CPLD/FPGA内部再取“非”操作;

- 一般电源模块(DC-DC,LDO等)的PG或EN信号,如果没有合适的电平时,适用这种电平转换方式;

- 由于三极管/MOS管的逻辑电平切换需要时间(开关时间),所以信息传递的延时会比较大;

1, 三极管/MOS管本身切换时间比较慢(具体原因分析,请参考《三极管基础》和《MOS管结构和原理》相关章节);

2, 三极管/MOS管在B/G极需要达到一定的电压才能导通三极管/MOS管,而在此电压之前三极管/MOS管不会有大动作(开关),会造成一定的延时。

- 对于较低速率信号,如上右图所示UART数据传输,可以通过三极管来实现不同电平的匹配和防挂死;

——对于数据(非电平状态)的传输,需要对三极管相关参数进行设计,保证其在特定传输速率下能够正常工作(信号边沿时间,占空比,传输延时以及三极管/MOS管支持的最大开关频率等等)。

- 三极管/MOS管的开启电压VBE/VGS(th) 大小,一般情况下SOT23封装的三极管/MOS管极限开启电压(最大值)可能在1V左右,所以如果是电压在1.0V左右,采用该电平转换方案存在一定的风险;

- 如左上图所示结构,如果采用三极管/MOS管来作为电源是否OK的判断,那么需要确定确定监测门限,来确定对输入电压的分压大小;

——举个栗子,假如监测2.5V电源是否OK,如果直接输入至MOS管G极,其开启电压:VGS(th)假设为1.0V,那么当2.5V电源电压上升至1.0V时,我们就认为2.5V这路电源电压OK了,这是有问题的;需要对2.5V电源电压进行分压,比如串联1KΩ后再下拉1KΩ,进行50%电源电压的分压,那么当2.5V电源电压上升为2.0V时我们才判断其电源电压OK。当然这是一种粗略且方便的监测设计。

2,逻辑器件电平匹配方案

如果规模较大的硬件电路,我们往往会CPLD来作单板的管理和信号汇聚功能(具体关于CPLD的设计及功能,后续在《硬件详细设计流程-CPLD设计》中详细描述)。我们知道CPLD的I/O管脚有很多个不同的Bank组成,而不同的Bank可以支持不同的供电电源。如下图所示,为Lattice MachXO2系列CPLD支持的不同单端I/O电源电压;其支持1.2V~3.3V的多种电平电压,基本上可以涵盖了一般硬件电路中所涉及到的电平。

那采用CPLD实现不同逻辑电平之间的转换,举个栗子(如下图所示):器件A是1.2V逻辑电平需要接到3.3V逻辑电平的器件B,设计CPLD的Bank0可以供1.2V而Bank1供3.3V,那么将器件A的信号接至CPLD的Bank0,而器件B的信号接至CPLD的Bank1;只要在CPLD逻辑内部将器件A和器件B的信号线连在一起,就完美地实现了电平转换。但在实际硬件设计上有这么完美么?(完美只存在于“理念世界”)

- CPLD有VCC和VCCIO两种电源,VCC电源(Core 电源)和VCCIO电源是否有什么关系呢?

1, VCC电源电压要求与VCCIO不一样,如下图所示(Lattice MachXO2系列CPLD支持的Core 电压),core电源电压与VCCIO电源电压本质上是两种不同的电源需求;所以两者可以合用也可以分开来提供,看怎样简单;

2, CPLD器件本身的上电时序,一般会要求VCC要先于或同时于VCCIO上电(后续《硬件详细设计:单板电源分析》详细介绍),否则可能会导致漏电,即VCCIO漏向VCC。

- 当单板中有多个器件使用了同样的电压,但那些器件由于上电时序的控制要求(或则布局要求,电源本身特殊需求等等),不能同时上电;那么CPLD的VCCIO电源要如何设置呢?

——举个栗子,器件A的I/O电源电压是+1.2V,器件B的I/O电源电压也是+1.2V,但是器件A的I/O电源电压要早于器件B上电,那么CPLD的VCCIO电源要选哪个呢?

1, 建议CPLD的VCCIO电源选择最早的那路,因为一些信号(举个栗子:复位、时钟等)需要器件上电时就要有明确的状态输入,如果CPLD的VCCIO电源较迟上电,那么会导致器件上电和CPLD 的VCCIO上电间隙的状态不确定;

2, CPLD的VCCIO电源早于器件的I/O电源上电,那么在器件的I/O电源还未上电时,CPLD输出的信号线上就有高电平输出到器件I/O管脚上,那么会导致电源电流的倒灌,并产生漏电压;

——举个栗子,如下图所示:P3V3_COM电源先于P3V3_IO上电,当在上电时序间隙,P3V3_COM电源会沿着输入管脚,通过防护二极管漏导P3V3_IO,使得P3V3_IO电源电压抬升;但电源电压被抬升就一定不允许么?1,如果器件资料中明确漏电压必须小于的电压值,那么必须严格执行;因为器件一旦监测到该路电源超过了某电压值,就表示开启了Power On 流程,但实际上漏电流无法支持器件正常工作所需的电流,会导致器件异常(可能需要完全下电后才能恢复);2,如果器件资料未明确规定漏电压的大小,建议漏电压小于0.5V。

- 我们已经明确了CPLD选择的VCCIO电源要早或同时于其它器件的上电时序,但是也会引入漏电压的问题,那如何来解决?

1, 与CPLD相连的信号线上拉电源,均使用器件侧I/O电源电压(而不是CPLD的VCCIO电源),这样避免了由于上拉电源导致的漏电流(如上图所示);

2, CPLD监测单板各路电源的上电状态,

(1)对于CPLD输出管脚:在监测到对接器件I/O电源上电之前,输出保持高阻态,在监测到对接器件I/O电源OK后,输出正常逻辑状态;

(2)对于CPLD输入管脚:保持输入状态,在监测到对接器件I/O电源上电之前,不对输入信号做响应。

3, 特殊信号,举个栗子:复位信号;器件要求上电之前需要保持低电平,而如果信号外接是通过电阻上拉,则需要特殊处理,以保持满足器件的要求。

——对不同的信号做不同的处理:由具体的器件、硬件系统以及应用需求所决定,并非有一个绝对的标准可遵循;所以做硬件设计之前,首先需要明确的是产品应用需求,然后分解系统需求,再是硬件需求,然后才是选择器件,制定硬件设计方案,我们所设计的每个器件、每条走线都是从上述需求中分解下来了的,可以进行验证和解释的。

- 解决了上述漏电压的问题后,CPLD方案也并非是一个万能的解决方案;如下图所示,CPLD内部的传输延时会比较大(typ:7ns左右),一般情况下7ns的延时是不会产生影响的,但是对于较高速的总线传输来说就会有问题了;此时最好采用专用电平转换器件(延时:百ps级别)。

——举个栗子:50MHz的SPI总线通过CPLD进行电平转换(3.3V—>1.8V),此时的读时序就会受到非常大的影响,导致读失败(关于SPI总线的读时序,后续《总线设计基础》详细分析)。

采用CPLD实现电平转换的设计,虽然整体看起来有点复杂,但这是系统性解决整板电平匹配最简洁、方便的方案。同时,CPLD由于较好的过冲防护设计,以及输出驱动可调等特性,所以在很多应用场合可以省去源端匹配电阻设计,进一步简化单板硬件设计。如下图所示。

3,专用器件电平匹配方案

这类器件非常多,有4路、8路、16路等驱动器(举个栗子:74LVX4245MTCX,SN74LVC16T245等等),只要在对应端口的Vcc电源管脚接上对应的电源电压即可实现电平转换;其延时小,无需考虑漏电电压的问题,对于简单小数量信号线的电平转换是非常好的选择。

除此之外,我们还经常会用到IIC(OD,双向)的电平转换器件,这类双向数据传输的电平转换,如果采用CPLD,实现起来需要比较复杂的逻辑(需识别读、写操作),所以使用专用电平转换器件会方便很多,举个栗子:PCA9517等。

另外,还有一类是自动识别方向的双向电平转换器件,这类器件无需进行方向控制,可以自动识别并进行驱动,举个栗子:TXS0108EPWR等;其好处是使用方便,缺点是如果信号质量设计有问题(不匹配导致过冲),会使得器件的方向识别错误,导致产生信号振荡。

专用器件来实现电平的转换,对于局部电路来说更加简单、方便,也是平时硬件设计中最常用的方法,适合两个器件之间的多个信号的电平转换;如果一个电平转换器件对应多个器件之间的互连,或需要大量使用电平转换器件,那样会导致单板面积和器件成本的增加;可以考虑CPLD。

-

模组串口电路常见电平匹配方法2023-06-07 12121

-

什么是LVDS电平#电路设计小鱼教你模数电 2021-11-22

-

高电平和低电平之间的电平芯片会识别成什么#硬声新人计划小鱼教你模数电 2021-11-26

-

按键按下电平如何修改橙群微电子 2023-03-14

-

一个微动开关同时控制2路不同电平的信号做高低翻转!李开鸿 2023-05-23

-

关于N-MOS管电平匹配的问题2018-12-29 4947

-

TTL电平与CMOS电平的区别2007-10-10 9014

-

ECL电平、LVDS电平、TTL电平_简单的比较2016-08-29 2163

-

常用的电平转换方案分享2020-11-03 5410

-

【经验】TTL与COMS的关系总结:TL和COMS电平匹配以及电平转换的方法资料下载2021-04-17 1550

-

LTC6406阻抗匹配电平移位演示电路差动放大器2021-06-07 822

-

几种电平转换电路2021-12-09 1718

-

逻辑电平--差分信号(PECL、LVDS、CML)电平匹配2022-11-10 18080

-

电平设计基础:差分逻辑电平匹配2023-06-25 8116

-

电平匹配问题,简单却容易被忽视2024-12-20 2354

全部0条评论

快来发表一下你的评论吧 !