电平设计基础:差分逻辑电平匹配

电子说

描述

二,差分逻辑电平匹配

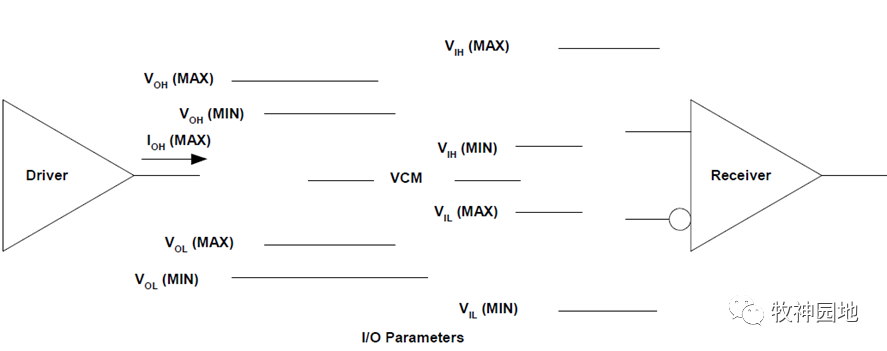

差分逻辑电平之间的匹配,主要应用于时钟和高速信号。通过之前章节关于差分逻辑电平的电路结构分析,为保证差分信号输出与输入的匹配,则要满足如下几个条件:

- 对于输出端来说,要保证从输出±端的回流通路(电流模式);

- 对于输入端来说,要保证输入共模电压和差分摆幅(差模电压)满足输入端要求(如下图所示);

- 对于传输线来说,要保证传输线阻抗匹配(终端并联),保证信号传输质量。

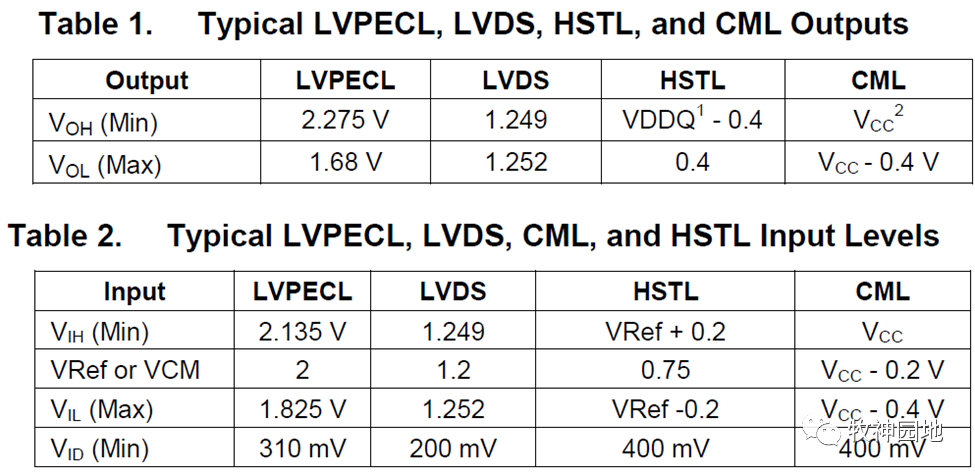

LVPECL,LVDS,HSTL以及CML差分逻辑电平之间的输出和输入判断电平如下图所示。

1,LVPECL驱动输出

LVPECL电路逻辑输出必须要有对地直流偏置通路,作为其共模输出电压。

1.1 LVPECL to LVPECL

LVPECL直流耦合输出的两种匹配电路如下图所示。

- 左下图中终端上下来电阻用于阻抗匹配和共模电压设置:

1, 终端上下拉电阻(83Ω和130Ω)用于传输线阻抗匹配: 83//130 = 50Ω;

2, 直流耦合方式中终端匹配接至Vcc-2V偏置电压,达到Vcc-1.3V = 2V的共模输入电压要求(具体原因请参考《ECL电平》章节相关内容)。

- 右下图中终端匹配电阻网络的设计,此方案相比于第一个方案节省了一个电阻。

LVPECL交流耦合输出的两种匹配电路如下图所示。

- 左下图中输出端采用150Ω下拉,终端上下来电阻用于阻抗匹配和共模电压设置:

1, 终端上下拉电阻(83Ω和130Ω)用于传输线阻抗匹配:83//130 = 50Ω;并提供LVPECL共模输入电压:Vcc -1.3V = 2V;

2, 150Ω下拉电阻用于提供LVPECL输出直流偏置,以及为输出电流提供直流电流路径。

——细心的胖友们应该还记得,在《ECL电平》章节中推荐设计的终端上下拉电阻以及输出端下拉电阻阻值与本章计算的电阻值有所不同,这主要是跟器件本身相关,后续遇到LVPECL相关设计,需要根据器件资料的推荐进行设计。

- 右下图中终端匹配电阻网络设计中,带电容的终端匹配网络主要用于:消除差分信号抖动导致的共模噪声;VBB一般在接收端器件内部提供。

1.2 LVPECL to LVDS

LVPECL直流耦合LVDS,如下左图所示,当LVPECL输出对于LVDS输入端电压太高时,通常需要33Ω串联电阻用于减小输入电压范围;但大多数LVDS接收机能够接收LVPECL信号,不需要在LVDS输入端对LVPECL信号进行衰减,因为LVDS输入端的共模范围很宽。

LVPECL交流耦合LVDS,如下图所示;在交流耦合时LVPECL输出端的150Ω下拉电阻还是需要的,它为输出端提供了直流偏置通路;终端100Ω差分阻抗匹配电阻,用于提供足够的信号摆幅来驱动LVDS输入端,两个10kΩ电阻将LVDS共模输入电压设置为1.65V,在LVDS接收机共模电压范围内。

——很多LVDS输入端已经集成了100Ω电阻,那么外部的100Ω电阻可以去掉。

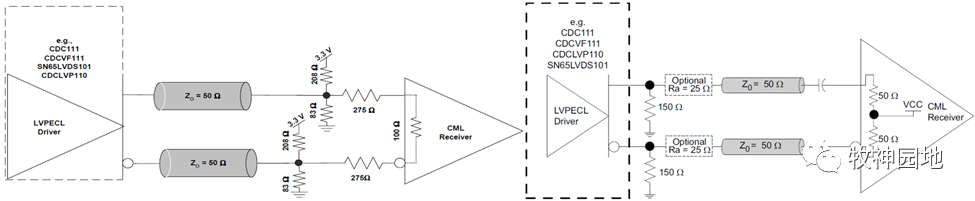

1.3 LVPECL to CML

如下左图所示为直流耦合电路,为了匹配CML的输入,需要做复杂的电路匹配设计;所以交流耦合设计更加简洁、方便,推荐使用交流耦合匹配的方式。交流耦合LVPECL在输出端设计150Ω下拉电阻,用于提供直流偏置回路;LVPECL输出摆幅是750mv而CML要求输入摆幅是400mV(68%),那么如下图所示需要进行分压:50/(50+23) = 0.68,所以串联电阻Ra = 23Ω,实际设计选择Ra = 25Ω。

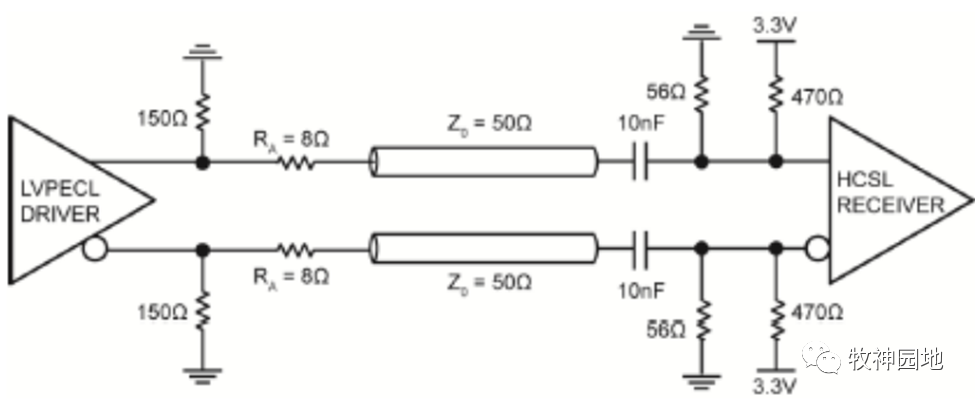

1.4 LVPECL to HCSL

如下图所示,在LVPECL交流耦合HSCL,输出端150Ω电阻下拉提供直流偏置;为了将800mV的LVPECL摆幅衰减到700mV的HCSL摆幅时,必须在150Ω电阻之后放置一个衰减电阻(Ra =8Ω);HCSL输入端需要重新偏置,可以通过将470Ω电阻连接3.3V和56Ω电阻到GND上来实现HCSL输入端350 mV的共模偏置电压。

2,LVDS驱动输出

2.1 LVDS to LVPECL

如下图所示,LVDS输出直流耦合LVPECL输入,83Ω与130Ω并联匹配提供LVPECL输入共模电压:2V;同时提供了差分线的阻抗匹配:83Ω//130Ω = 50Ω。

如下图为交流耦合匹配电路,LVDS输出端不需要提供直流偏置回路,所以我们只需设计LVPECL输入端的共模偏置电压(Vcc – 1.3V = 2V),和终端阻抗匹配(差分:100Ω,单端:50Ω)。

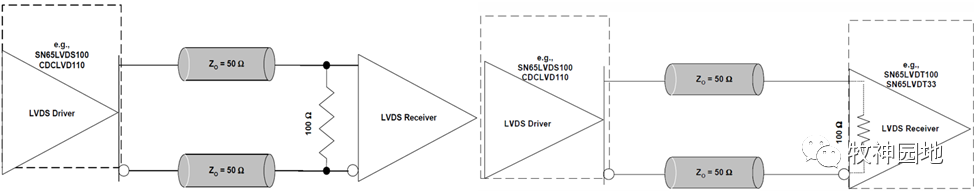

2.2 LVDS to LVDS

LVDS输出直流耦合LVDS输入,如下图所示;电路匹配非常简单,只需在终端跨接100Ω电阻,如果输入端已集成100Ω终端电阻,那么可以去掉外部电阻;共模偏置电压直接由输出端提供。

LVDS输出交流耦合LVDS输入,同样只需要跨接100Ω作为终端端接;但此时输入端共模偏置电压需要外部提供,具体如下图所示。如果器件内部集成了100Ω终端电阻以及内部偏置,那么交流耦合直连即可,具体需要看器件规格书,再决定采用直流还是交流耦合更加方便。

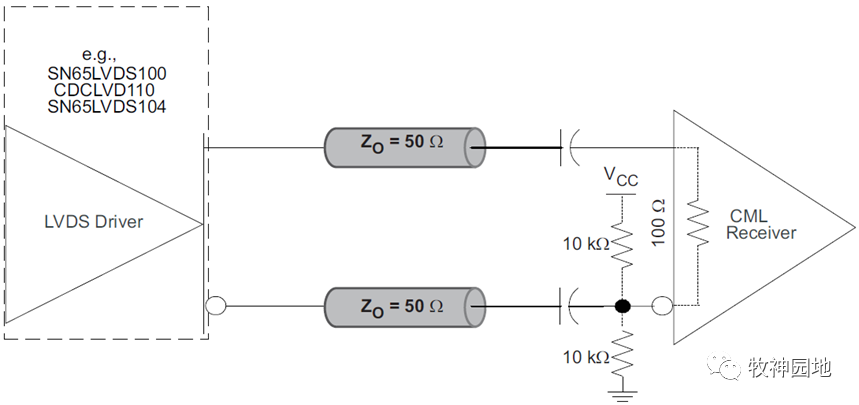

2.3 LVDS to CML

大多数CML接收器有片上终端匹配(100Ω),不需要额外电阻。而且只有当CML输入端不提供偏置电压时,才需要两个10KΩ电阻。但这些都需要根据实际的器件规格书来确定具体的匹配方式。

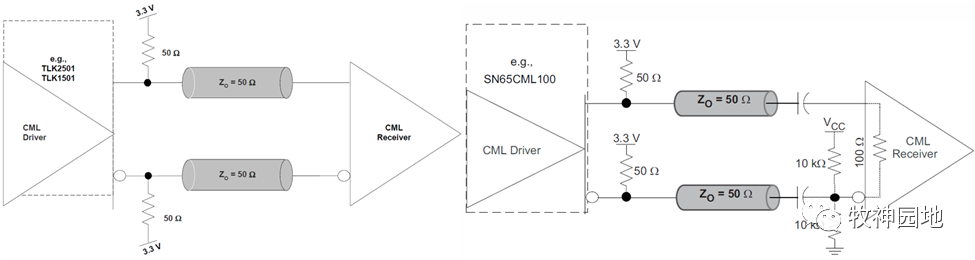

3,CML驱动输出

3.1 CML to LVPECL

如下图所示,CML输出到LVPECL输入一般推荐使用交流耦合的方式;50Ω上拉电阻用于CML输出的直流偏置,并提供一个源端匹配(这个50Ω电阻本来是在CML输入端上拉的,需要外部匹配,具体参考《LVDS&CML 电平》相关章节内容);如下左图所示,LVPECL输入端器件内置了匹配电路。

如下右图交流耦合匹配电路,R1应大于50Ω以防止CML输出损耗和PCB损耗过大,无法满足LVPECL输入端的最小差分输入电压摆幅要求。

3.2 CML to LVDS

一般来说CML输出到LVDS输入,建议采用AC耦合的方式;原理同上,输出端需要50Ω上拉电阻已提供CML输出直流偏置和匹配;LVDS输入端则需提供共模偏置电压和100Ω电阻以提供差模电压摆幅。如果输入端LVDS已经集成了100Ω电阻和共模偏置电压,那么可以直接通过交流耦合接至输入端。

3.3 CML to CML

如果CML输出端和接收端都有相同的VCC电源电压和片上上拉电阻(50Ω),那么可以直接连接,无需外部元件;如果输出端不提供一个内部50Ω的上拉电阻,那么50Ω上拉电阻需要放置在输出端或接收端。而对于交流耦合方式,如下右图所示;只有当CML接收端不提供共模偏置电压,才需要两个10kΩ的电阻。匹配连接的方式需具体根据器件规格书再确定。

4,HCSL驱动输出

3.1 HCSL to LVDS

如下图所示, HCSL输出端电流在0和14mA之间切换:当一个输出管脚为低电平(0)时,另一个为高电平(驱动14mA)。HCSL驱动器的等效负载电阻为43Ω,与50Ω阻抗并联后相当于23.11Ω,计算可得LVDS输入的摆幅为14mA * 23.11Ω= 323mV。LVDS输入需要重新偏置,可以通过将一个8.7KΩ电阻连接到3.3V和5KΩ电阻连接到GND来实现LVDS接收器输入共模的1.2V 直流电平;如果LVDS接收器差分输入端上已内置100Ω电阻和共模偏置电压,则不需要外部100Ω电阻和共模偏置电阻。

写在最后

电平匹配设计并不是一成不变的,首先需要根据器件规格书从理论上对输出端和输入端的电路结构,高电平范围,摆幅等进行理论分析;然后进行电路匹配的设计,一般交流耦合更加简单方便(除非是相同电平标准,而且输出与输入规格相匹配的情况);最后单板回来后需要进行实际测试,确定匹配设计能够满足输入端的信号质量要求。

-

差分平衡电平接口的原理与优势2025-02-04 1745

-

什么是逻辑电平?如何实现电平转换?(原理讲解+电路图)2023-11-24 14309

-

电平设计基础:电平匹配设计2023-06-25 4884

-

逻辑电平--差分信号(PECL、LVDS、CML)电平匹配2022-11-10 18123

-

高电平和低电平之间的电平芯片会识别成什么#硬声新人计划小鱼教你模数电 2021-11-26

-

互联逻辑电平之差分互联综述2021-09-10 923

-

差分逻辑电平,LVDS、xECL、CML、HCSL/LPHCSL、TMDS等2021-07-17 6675

-

LVDS和CML与LVPECL的同种差分逻辑电平之间的互连教程2021-01-07 2147

-

逻辑电平的一些基本概念详细说明2021-01-06 2218

-

信号逻辑电平标准的详细说明2021-01-05 1879

-

常见逻辑电平介绍和基本概念2021-01-02 26571

-

常见差分逻辑电平和相关输入输出原理2020-12-23 17874

-

浅谈LVDS、CML、LVPECL三种差分逻辑电平之间的互连2020-12-20 41493

全部0条评论

快来发表一下你的评论吧 !