深度解析电源顶部散热封装的发展和优势

电源/新能源

描述

当前,低碳化和数字化正推动电源管理技术朝着全新趋势大步迈进,提高效率、减轻设备重量、提高功率密度以及为电动汽车提高续航里程,都是大家在日常中共同关心的话题。在半导体行业中的相当长一段时间内,功率半导体、模拟半导体和数字半导体技术的演进都围绕着低碳化发展,例如数字芯片工艺节点一路演进,功率半导体的演进主要是在晶圆部分,不断向更小的芯片尺寸和更低的导通阻抗发展。

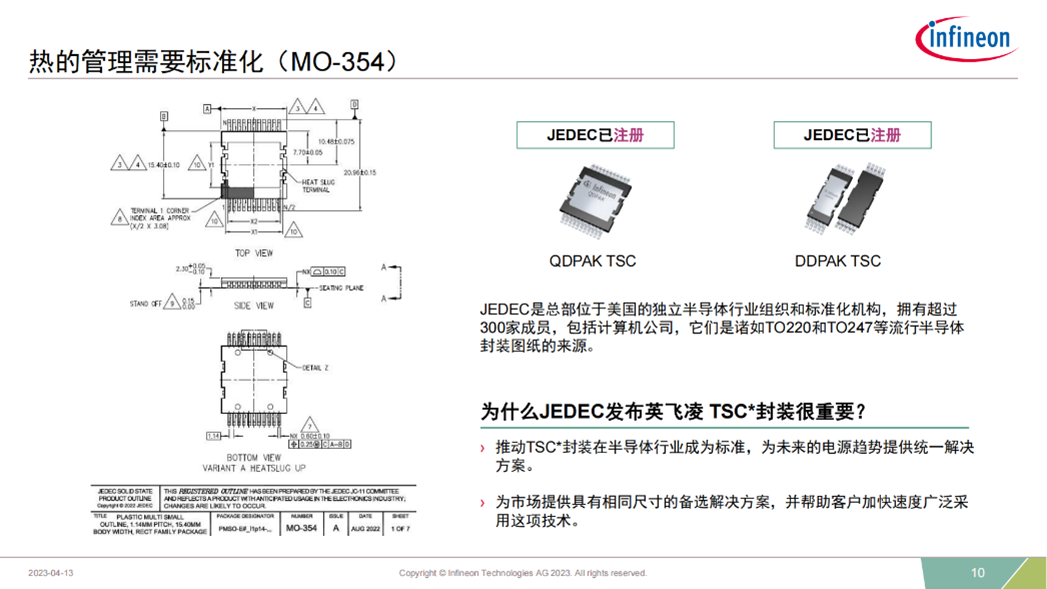

以硅基功率半导体为例,在Figure Of Merit系数(简称FOM值)上,高压超结(Super Junction)技术基本上已经达到其物理极限,在此情况下要继续把导通阻抗或能效做得更好,封装成为了必须突破的瓶颈。 “英飞凌在低碳化——也就是在减少能耗和提高能效方面所做的一个努力,就是在JEDEC标准组织注册的顶部散热封装技术(TSC)。” 在近日举行的一场媒体沟通会上,英飞凌科技电源与传感系统事业部大中华区应用市场总监程文涛介绍了该公司用于高压MOSFET 的 QDPAK 和 DDPAK 顶部冷却 (TSC) 封装,他同时表示,除了硅基功率器件,目前大热的碳化硅(SiC)、氮化镓(GaN)等第三代半导体也都仰仗更新的封装技术,把芯片性能发挥到极致。

英飞凌科技电源与传感系统事业部大中华区应用市场总监 程文涛

顶部散热封装的发展和优势

顶部散热(TSC)封装 QDPAK和 DDPAK的前身,其实是大家熟悉的DPAK(TO252)封装。QDPAK大致相当于4个DPAK并排,DDPAK则是两个DPAK并排(Double DPAK),这类封装的主要优势在于:

满足更大功率需求:优化利用电路板空间,采用开尔文源极连接,减少源极寄生电感;

提高功率密度:顶部散热可实现最高电路板利用率;

提高效率: 经优化的结构具有低电阻和超低寄生电感,可实现更高效率;

减轻重量:综合优化散热和发热,有助于打造更小巧的外壳,从而减少用料,减轻重量

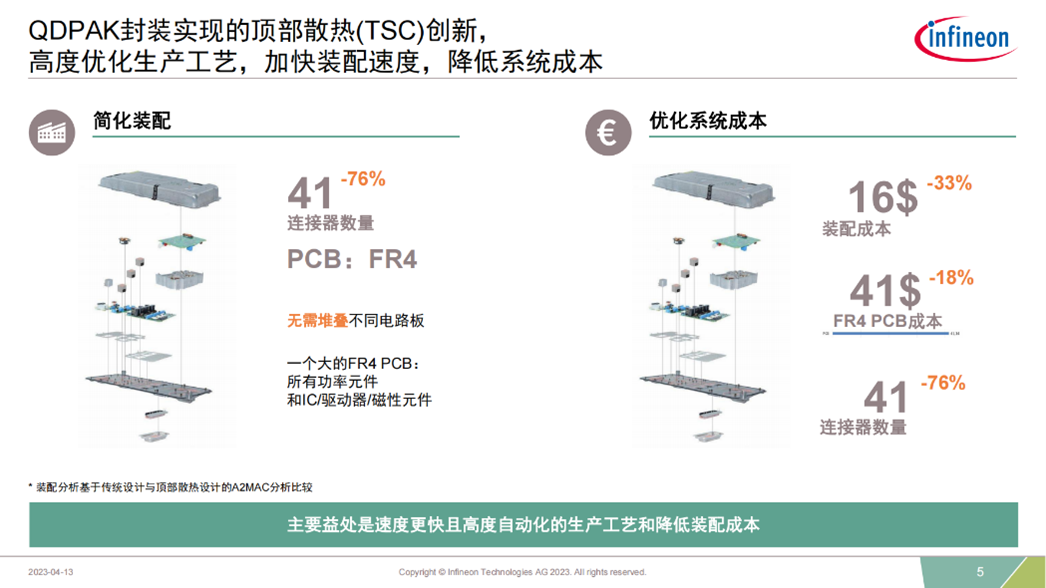

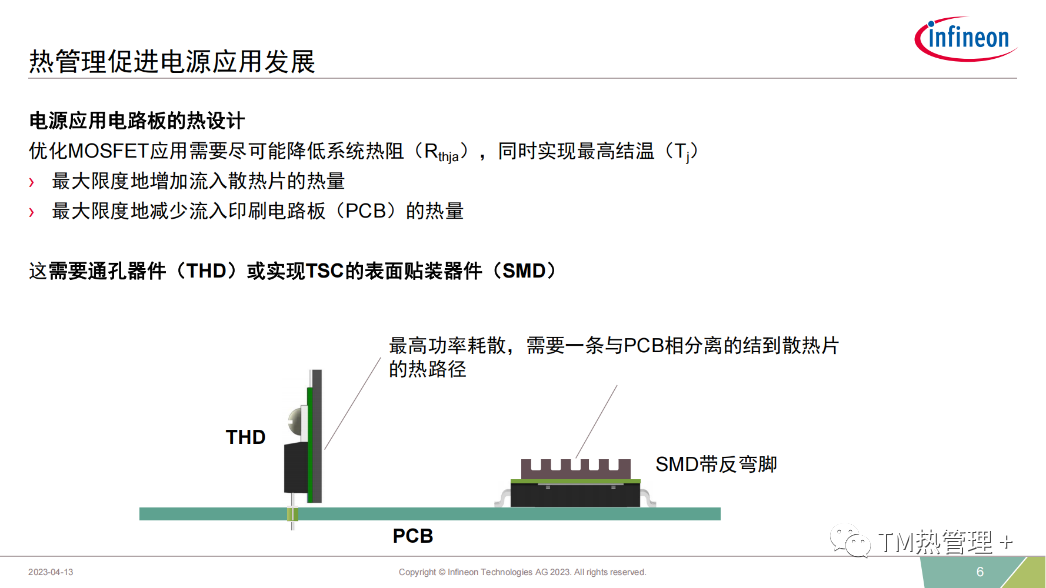

程文涛表示,这两种顶部层散热封装技术在用户层面能够解决的问题包括,让整个装配过程步骤变少,自动化制造流程更简洁,最终在下游厂商端实现包括PCB数量、层级和板间连接器用量减少,带来装配及整体系统成本大幅降低。 优化MOSFET应用需要尽可能降低系统热阻(Rthja),同时实现最高结温(Tj)。如此一来能够最大限度地增加流入散热片的热量,并最大限度地减少流入PCB的热量。 熟悉功率半导体行业的读者应该还有印象,10年前的大功率应用器件(千瓦及以上的功率)基本以通孔器件封装(THD)为主,例如大家熟知的TO247、TO220封装。这类插件封装的优势在于,在当时的装配和封装工艺下能最大限度地利用外加散热片,高效地把芯片内部产生的热量带出芯片,让芯片能够工作在大功率应用场景中。

但随着数据中心、4G及5G无线通信宏基站等设备对于功率密度的要求越来越高,设备尺寸越做越小,开始要求电源应用的电路板设计中采用更少或不用独立散热片,同时把更多的热量均匀地散发到整个设备之外。 贴片化是从带独立散热片的插件封装,走向更高功率散热的第一步。但这对于紧贴PCB表面的贴装器件(SMD)来说,很难做到。 “这是两个很矛盾的需求,尤其在最近的5年之内越来越凸显。我们用了很长时间与产业链下游的行业头部客户以及工程师讨论,最终达成共识,就是顶层散热才是解决这个矛盾的根本途径。” 程文涛说到。

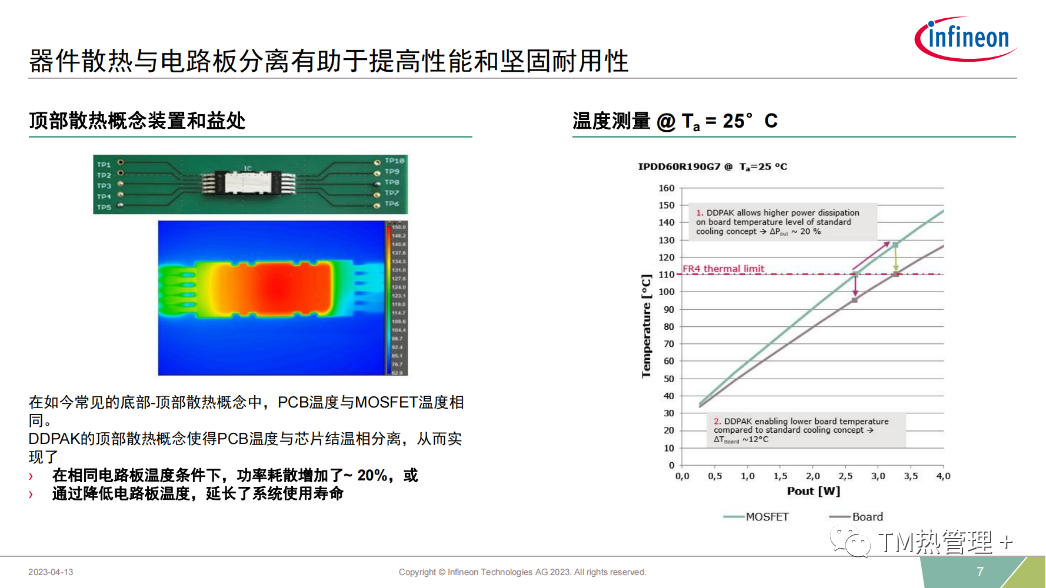

如上图(左)所示,一般贴片封装器件的散热主要靠芯片底部与PCB之间的接触,靠PCB铜箔把芯片产生的热量传导出去。这样做的坏处是需要耗费较大的PCB铜箔面积,才能有效散热,如果铜箔不够大,在芯片底部就会形成一个热点,给PCB带来很大压力。 目前业界常用的PCB材质均为FR4,这类材质在业界标准中存在110度左右的最高温度上限。在这样的要求下,如果利用贴片和PCB之间的结合均匀地将更多热量传递出去是个挑战,在这方面,底部散热封装慢慢地走到了瓶颈。 而上图(右)显示在使用增加散热片的顶部散热模式后,可以不靠底部铜箔散热,在同样的PCB材质下,能够更有效、更均匀地把热量散出去。如此一来给用户带来的好处是,在同样的散热面积下,设备整体能够传递出的功率耗散得到了增加。

顶部散热封装的主要应用市场

其实利用芯片顶部层散热的方式,在早期的手机充电器中已经有尝试,当时的做法有的靠灌胶,有的靠通过塑料封装将热量传导到机壳上。可以说顶部散热方式覆盖的功率段范围相当广泛。而英飞凌提供的这类顶部带铜箔的顶部散热封装在功率约为200-300W的应用场景中,就开始凸显其价值了,采用该封装方式,可以实现取消独立散热片,或替代插件器件;而一般功率在1000W时,顶部带裸铜的顶部散热封装就是一个必选项。 程文涛举例到,在5G或通信领域,目前基站基本都是无风扇设计,与手机充电器的环境类似。但基站一般靠密闭的金属外壳散热,如果不用顶部带裸铜的封装方式,功率器件无法有效、均匀地把热量传导到外壳上。第二个主要场景是数据中心,从最近火爆的ChatGPT可以看到人类对数据无止境的需求增长是近似指数级的,在这种情况下对电源转换的效率,以及对同样机房尺寸中能够安装的设备数量提出了更高要求。 还有一种应用场景是新能源汽车,目前为了满足电动汽车的设计要求,业界在不断增加功率半导体能效的同时,还致力于减少它所占用的PCB面积,这时候对功率密度的要求也很高。顶部散热能够帮助工程师在设计新能源汽车时,把更多空间留给电池动力部分。 据悉英飞凌在这几个领域的头部客户已经在积极采用顶部散热封装的功率器件。

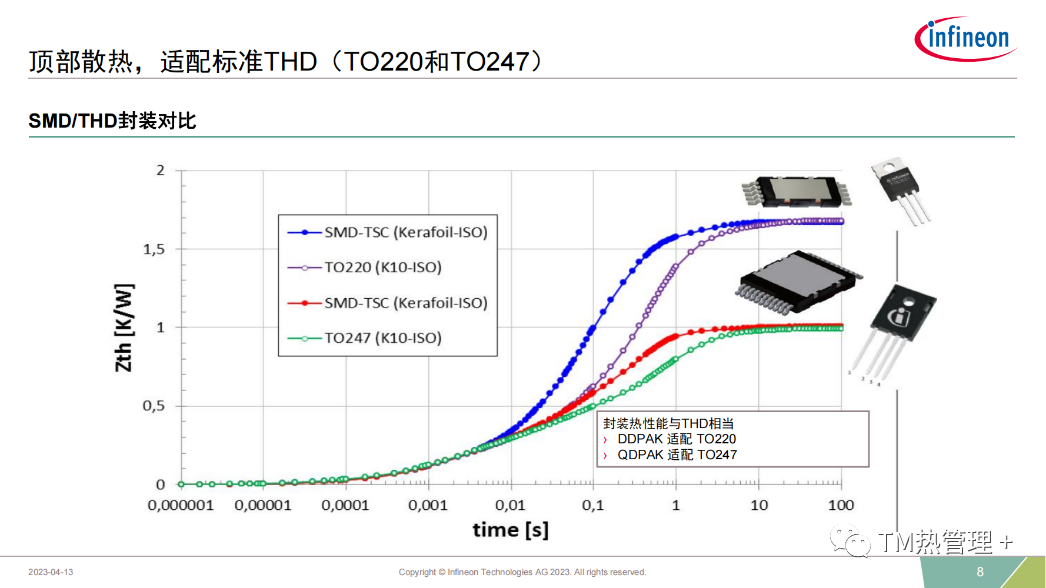

由上图可见,基于这个考量标准,英飞凌的QDPAK和DDPAK封装,在温度稳定之后的散热能力与TO220/TO247实现了对等。

行业整体接受度如何?

“在顶部层散热芯片刚刚开始推行的时候,主要的质疑来自于行业里电源领域的工程师,因为他们之前最信赖的、能够有效散热的封装是TO247和TO220,所以工程师们需要我们新提出的顶部散热封装在散热能力上能够与TO247和TO220对等。” 程文涛回忆到,“这也是我们研发QDPAK和DDPAK时的主要考量——对标TO220和TO247。在同样的功率等级以及更高功率密度的情况下,如果QDPAK和DDPAK没有更好的效能,很难说服工程师从原来的插件封装方式顺利切换到贴片方式。” 由于顶部散热封装是一种新的封装形式,三年前英飞凌在向行业头部客户介绍该技术时,遇到的最大阻力主要来自于生产线上的加工工艺还不能完全适应顶部散热这一概念。 其中,最需要解决的问题是——在同一个PCB上贴装很多顶部散热芯片后,怎么保证这些芯片的高低一致?同一个模具所加工出来的平面散热片,怎样才能均匀地贴在这些顶部散热的芯片上,并且能够保证它们之间的热阻基本一致? 程文涛表示,对此英飞凌花了近两年时间,通过自己实验以及一些头部厂商工程师的配合,逐渐摸索出了一套行之有效的方法。

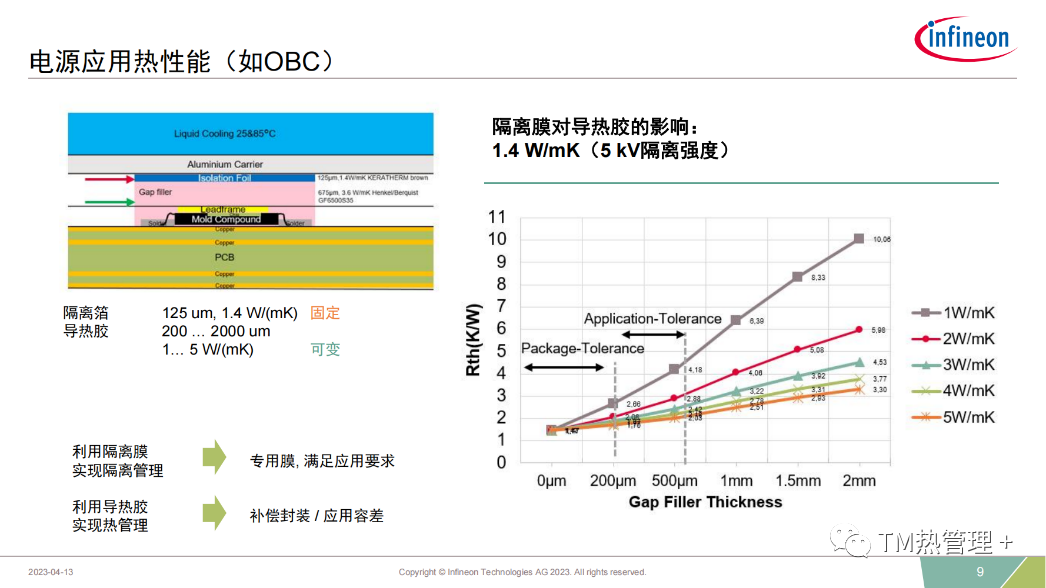

以用在功率半导体上的顶部散热芯片为例,一般顶部散热接触的电平是处理高压的MOS管漏极,需要经过安全可靠的隔离才能接触外部设备,这一点与插件式封装非常类似。但在多个并联或并排摆放的顶部散热芯片方案中,要平均地把热量传导出去,目前英飞凌认为最有效的方式是用Gap Filler导热胶,均匀地把热传导到顶部散热片中。 上图列出了不同导热能力的导热胶所产生的效果。在目前采用顶部散热方式的大多数应用中,主要使用的散热方法是第一层放置隔离片,上面加一层能够适应公差的导热胶,让所有并排摆放的顶部散热芯片的热量能够均匀地传导到同一个平面散热片上。此外还有单个芯片所采用的锁螺丝、铜夹子或焊接散热片的其他导热方式,但从加工速度、制造成本和符合安规要求等角度来讲,导热胶仍是最行之有效的方法。

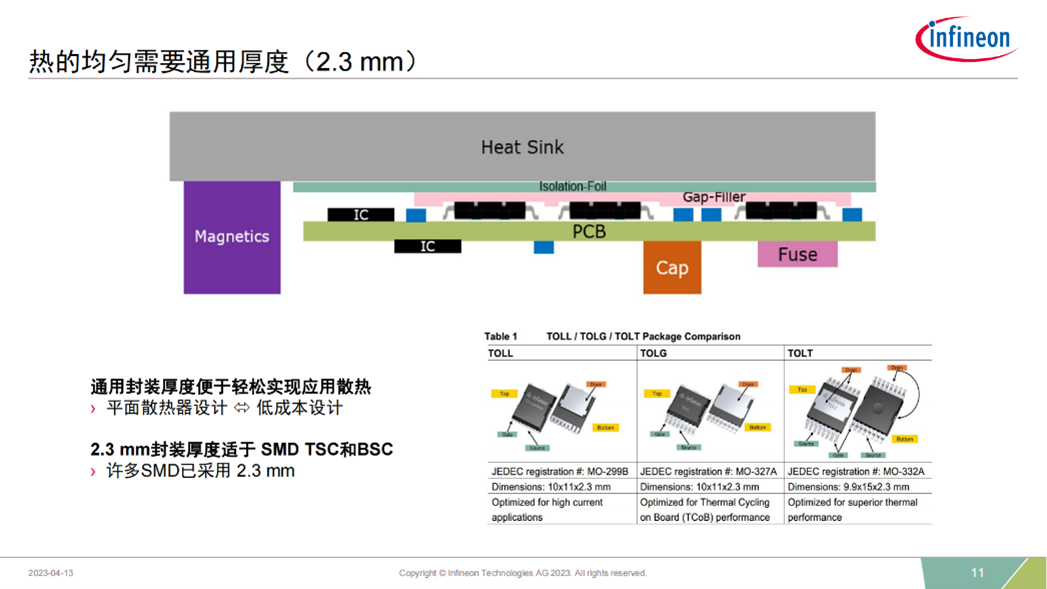

据介绍,除了QDPAK和DDPAK,英飞凌还有其它一些顶部散热的封装方式,比如TOLT封装。对于这类贴片的顶部散热封装,需要所有的器件都贴在同一个平面的PCB板上,并且出于成本的考量,这些器件需要利用同一块平面散热片把热量均匀地传导出去。 这时候同样的器件高度标准至关重要。英飞凌对于顶部及底部散热功率器件需要的通用封装厚度的定义是2.3毫米,关于选择这个厚度的缘由,程文涛表示首先要考虑到顶部散热的做法不能成为其它非顶部散热芯片的应用障碍,如果其它非顶部散热的封装比较厚,那么顶部散热的封装就不能比它薄,否则会产生热量散不掉的问题,或是需要加很厚的散热垫。“我们研究了行业中很多的贴片封装尺寸,在大部分的非顶部散热以及顶部散热封装共存的情况下,选择了2.3毫米。这样的厚度能够让足够多的器件并存在同一块PCB板上。” 他同时表示,希望通过这次与JEDEC标准组织的互动,能够使2.3毫米的封装厚度成为业界通用标准。

成为JEDEC标准对顶部散热(TSC)

封装推广的重要性

资料显示,JEDEC组织是总部位于美国的独立半导体组织和标准化机构,拥有超过300家成员,其中包括计算机公司,他们是诸如TO220和TO247等流行半导体封装图纸的来源。注册成为JEDEC标准之所以对于英飞凌的顶部散热(TSC)封装如此重要,主要是因为这样可以推动TSC封装在半导体行业成为标准,为未来的电源技术发展提供统一解决方案;其次还能为市场提供具有相同尺寸的备选解决方案,帮助客户加快速度广泛采用这项技术。 程文涛透露,在功率半导体领域业界有一个不成文的规定,“任何一家厂商选定一款功率半导体时,至少要有一个备选方案,也就是Second Source,理想的情况是有三四种备选方案。”

一种或多种备选方案能够保障供应的稳定性,在生产制造过程中不会因某一家供应商或某个地区的不可抗因素而导致断供。如果需要多个备选方案,用户的直接诉求往往是能直接将一家厂商的器件不加设计或改造地替代另一厂商的器件。这种情况下标准至关重要,如果厂商之间在器件的引脚长度、宽度、中间间隙以及器件厚度等参数公差上没有统一标准,做出来的产品会有很大的差异,导致客户难以直接对器件进行替换。 “JEDEC标准目前在半导体行业中,是大家公认会采纳且免费的标准。一家厂商的技术注册和认证成为JEDEC标准之后,其他厂商便可以免费从JEDEC标准组织下载这些标准,遵守它所定义的尺寸和公差,就能够在行业里声称是跟JEDEC标准兼容,不设置专利门槛。

厂家要做的就是制造符合这个业界通行标准的产品,这样为产品做推广时也会更方便,” 程文涛说到。 另外,JEDEC标准组织也让行业中的创新想法得到了快速推行。英飞凌的QDPAK和DDPAK,以及一些其它的顶部散热封装技术,也正是得益于在JEDEC标准组织中的注册,推行速度相比于过去几年越来越快,让整个半导体行业从中受益。

编辑:黄飞

-

博通HSMH - H150单色顶部安装芯片LED深度解析2025-12-30 88

-

顶部散热封装QDPAK安装指南2025-12-22 214

-

QDPAK顶部散热封装简介2025-12-18 506

-

Wolfspeed推SiC MOSFET/SBD新品:顶部散热封装2025-07-08 3478

-

新品 | 采用顶部散热 Q-DPAK封装的 CoolSiC™ 1200V G2 SiC MOSFET2025-05-29 1046

-

新品 | 采用顶部散热QDPAK的CoolSiC™ 1200V G2 SiC MOSFET半桥产品2025-05-27 1254

-

华润微持续发力MOSFET先进封装,三款顶部散热封装产品实现量产2024-11-15 2690

-

插件封装技术VS顶部散热封装技术2023-05-06 1348

-

功率器件顶部散热封装技术的优势及普及挑战2023-04-29 8599

-

详解高效散热的MOSFET顶部散热封装2023-03-10 2457

-

CCPAK - GaN FET顶部散热方案2023-02-09 886

-

CCPAK-GaN FET顶部散热方案2022-08-30 2158

-

如何实现电源应用的散热仿真2021-04-07 2782

-

TI推出通过封装顶部散热的标准尺寸功率MOSFET2010-01-22 1190

全部0条评论

快来发表一下你的评论吧 !