握手机制、通道依赖性及AXI-Lite握手实例

描述

AXI4:高性能内存映射需求(如读写DDR、使用BRAM控制器读写BRAM等),为了区别,有时候也叫这个为 AXI4-Full;

AXI4-Lite:用于简单、低吞吐量的内存映射通信(例如,与控制寄存器和状态寄存器之间的通信);

AXI4-Stream :高速流数据(视频、图像等流式数据);

AXI4 、AXI4-Lite和AXI4-Stream均使用Ready、Valid握手机制进行通信 。

**信息传输的发起者使用****Valid ** 信号指示数据何时有效,接收端产生 Ready 信号来表明已经准备好接收数据 , 当两者均为高时,启动传输 。

** AXI4 总线和 AXI4-Lite 总线都有 5 个通道(** **AXI4-Stream ** 取消了通道) ,**AXI4 和 AXI4-Lite **通道的相同部分:

(1) 写地址通道(AW) ,包含AWVALID,AWADDR,AWREADY信号;

(2) 写数据通道 (W)**** ,包含WVALID,WDATA,WSTRB,WREADY信号;

(3) 写应答通道 (B)**** ,包含BVALID,BRESP,BREADY信号;

(4) 读地址通道 (AR)**** ,包含ARVALID,ARADDR,ARREADY信号;

(5) 读数据通道 (R)**** ,包含RVALID,RDATA,RREADY,RRESP信号;

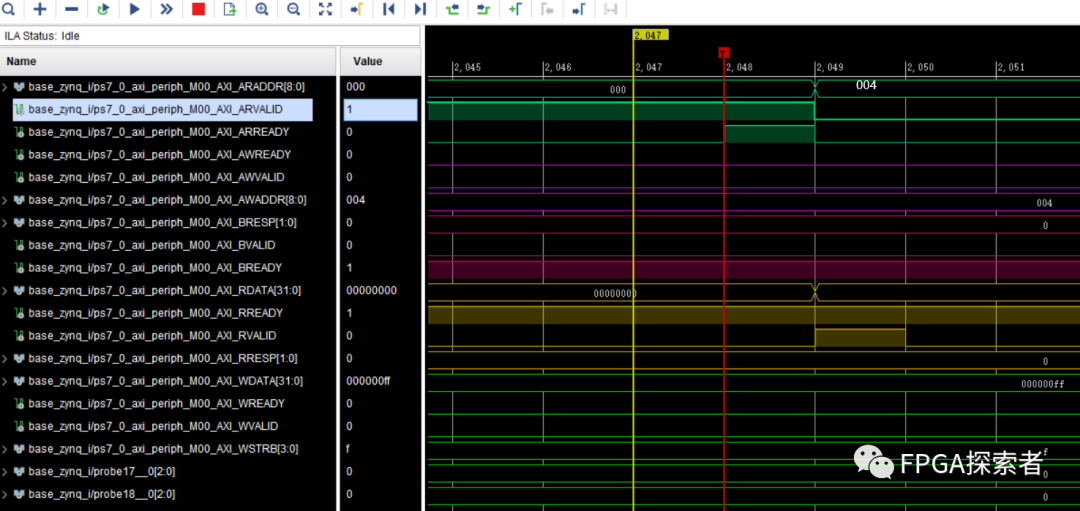

以 AXI-Lite 总线为例 ,Xilinx ZYNQ 通过 AXI4-Lite 总线控制 8 个 GPIO 的输出,先写入 0x0F 测试写入操作,再写入 0xFF 后读取写入的值,测试读操作。

本操作是 ZYNQ 作为主机 Master,AXI-Lite GPIO 作为从机 Slave, 使用 ** Xilinx ****的 ****AXI Interconnect ** 总线互联结构互联 。

**AXI4-Lite **是 AXI4 的删减版,适合轻量级的应用,也是包含 5 个通道,不同的是每个通道都进行了简化, 去掉了对突发传输的支持(Burst) 。

写事务握手实例

使用写地址通道、写数据通道和写响应通道 。

(1) 在写数据通道上 ,主机给出要写的数据 0x0F,并在一个时钟周期后将数据有效信号 WVALID 拉高,等待从机的 WREADY 写准备好信号拉高;

(2) 在写地址通道上 ,主机给出写地址 0x00(GPIO 通道 1 的输出数据的控制寄存器),并将地址有效信号 AWVALID 拉高,等待从机的 AWREADY 写准备好信号拉高;

(3)当 WVALID 和 WREADY 信号同时拉高后,数据成功写入 GPIO 从机;当 AWVALID 和 AWREADY 信号同时拉高后,地址成功写入 GPIO 从机;

(4)一个时钟周期后, 在写响应通道上 ,给出响应(BRESP 为 0),从机告诉主机已经成功写入;

此外,对于写响应信道,BREADY 由主机主动给出,一直保持在准备好接收响应的状态,当从机发来一个 BVALID 信号指示一个有效的响应后,BREADY 拉低一段时间后处理该响应信息,处理完成后又恢复到准备好接收响应状态。

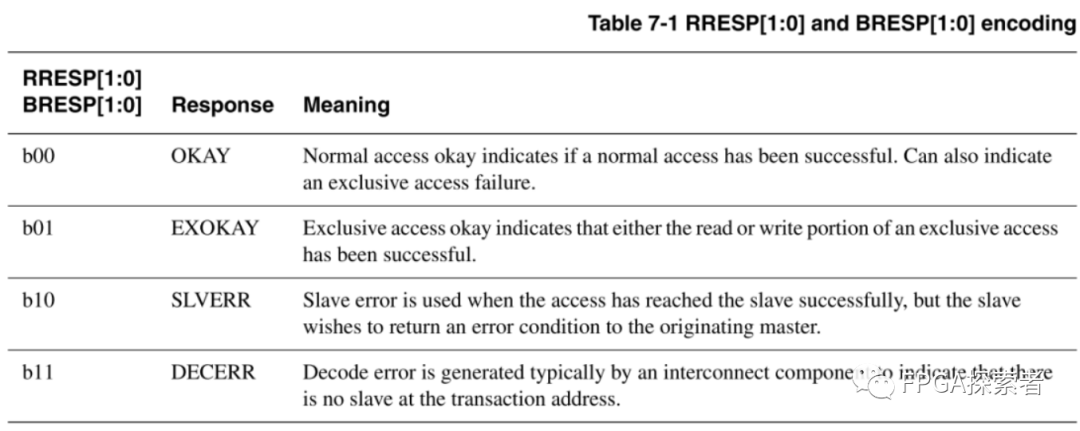

RRESP/BRESP 读/写响应信号的含义,2-bit 信号,分别代表读写成功、独占式读写、从设备错误、译码错误。

读事务握手实例

**先向地址 ****0x00 ** 写入数据 0xFF,再读出,使用读地址通道、读数据通道 。

(1) 在读地址通道上 ,主机给出要读取的地址 0x00(GPIO 通道1 的输出数据的控制寄存器),并将地址有效信号 AWVALID 拉高,等待从机的 AWREADY 写准备好信号拉高后,成功将要读取的地址写入从机;

(2) 在读数据通道上 ,从机给出读出的数据 0xFF,并将数据有效信号 WVALID 拉高,此阶段主机的 WREADY 写准备好信号一直拉高,数据在两个信号同时为高时传输,将 0xFF 写入主机,此时读响应 RRESP[1:0] 为 0,代表写入成功;

(3)当 ARVALID 和 ARREADY 信号同时拉高后,地址成功写入 GPIO 从机;

当 RVALID 和 RREADY 信号同时拉高后,数据成功返回给 ZYNQ 主机;

AXI4 总线握手机制

AXI4 、AXI4-Lite和AXI4-Stream均使用Ready、Valid握手机制进行通信 。

**信息传输的发起者使用****Valid ** 信号指示数据何时有效,接收端产生 Ready 信号来表明已经准备好接收数据 , 当两者均为高时,启动传输 。

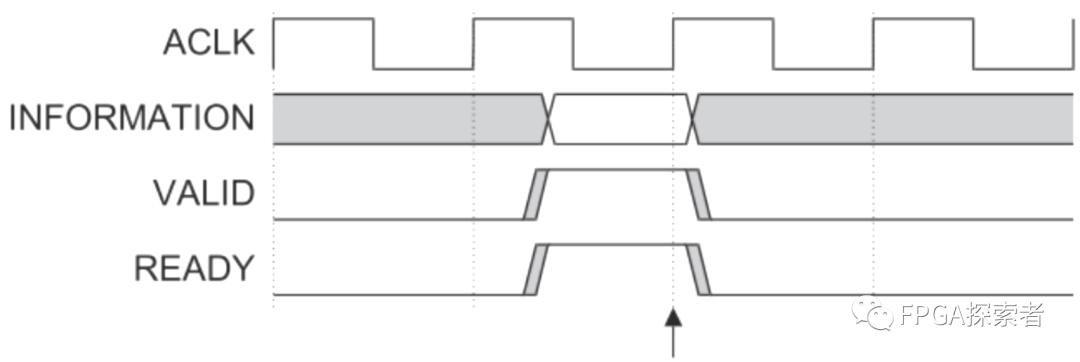

上面的实例给出了两种 Valid 和 Ready 出现的情况,一种是 Valid 先为高,另一种是 Ready 先为高,实际上,Valid 和 Ready 一共有三种可能情况:

(1)Valid 先为高 Ready 后为高

如前文实例中写地址和写数据通道所示,时序图如下,传输发生在箭头所指处(在时钟 ACLK 的上升沿检测到同时为高):

Master 主机发送端首先发出数据或者控制信息,并将自己的 Valid 有效信号拉高,指示信息(information)有效;

发送端的信息(information)和 Valid 信号保持稳定,直到 Slave 从机接收端的 Ready 信号拉高,指示接收端已经接收到 information。

(2)Ready 先为高 Valid 后为高

如写响应通道所示,时序图如下,传输发生在箭头所指处(在时钟 ACLK 的上升沿检测到同时为高):

Slave 从机接收端首先表明自己准备好接收数据或者控制信息,将自己的 Ready 准备好信号拉高;

Master 发送端的信息(information)一旦有效,传输立刻开始。

(3)Ready 和 Valid 同时为高

时序图如下,传输发生在箭头所指处(在时钟 ACLK 的上升沿检测到同时为高):

AXI4 总线通道依赖

(1)读事务(读地址通道、读数据通道)

• 主机先发送 ARADDR 和 ARVALID 给从机;

• 从机回发 ARREADY,通知主机该地址有效;

• 当 ARVALID 和 ARREADY 均为高电平时,主设备拉高 RREADY,表示主设备准备好接收读数据和读响应信号;

• 从设备发送 RVALID、RDATA 以及 RRESP,当 RVALID 和 RREADY 均为高电平时,数据成功写入主设备。

图中的单箭头表示:箭头两端的信号没有依赖关系,谁先拉高都行;

图中的双箭头表示:箭头起始信号拉高之后,箭头指向的信号才可以拉高。

下图可以看出,读地址的 Valid 和 Ready 两者谁先拉高都可以,读数据的 Valid 和 Ready 两者谁先拉高也没关系,但是读数据必须在读地址完成后才可以拉高。

(2)写事务(写地址通道、写数据通道、写响应通道)

在写操作过程中,主机向从从机发生AWADDR、AWVALID、WVALID和WDATA,当 WVALID 和 WREADY 都为高电平时数据写入从机。

**主设备发送的 AWVALID ** 和 WVALID 要有重叠区 。

-

芯片设计之握手协议2025-05-14 1359

-

【芯片设计】握手协议的介绍与时序说明2023-12-11 5775

-

关于AXI Lite无法正常握手的问题2025-07-16 5487

-

ZYNQ & AXI总线 & PS与PL内部通信(用户自定义IP)2018-01-08 14607

-

有没有一种标准的方式到达PL AXI-Lite总线?2019-04-12 2601

-

AXI总线的相关资料下载2022-02-09 817

-

AXI接口协议详解2022-04-08 6012

-

什么是握手信号? 什么是握手协议?2008-10-14 5916

-

AXI总线学习(AXI3&4)2021-12-05 977

-

AXI3与AXI4写响应的依赖区别2023-03-30 2061

-

AXI4协议五个不同通道的握手机制2023-05-08 2265

-

在握手协议中的Valid及data打拍技巧2023-06-27 2990

-

简述TCP协议的三次握手机制2024-08-16 3721

-

TCP三次握手安全性分析2025-01-03 2016

-

AXI握手时序优化—pipeline缓冲器2025-03-08 1501

全部0条评论

快来发表一下你的评论吧 !