数字IC前端设计流程及工具

EDA/IC设计

描述

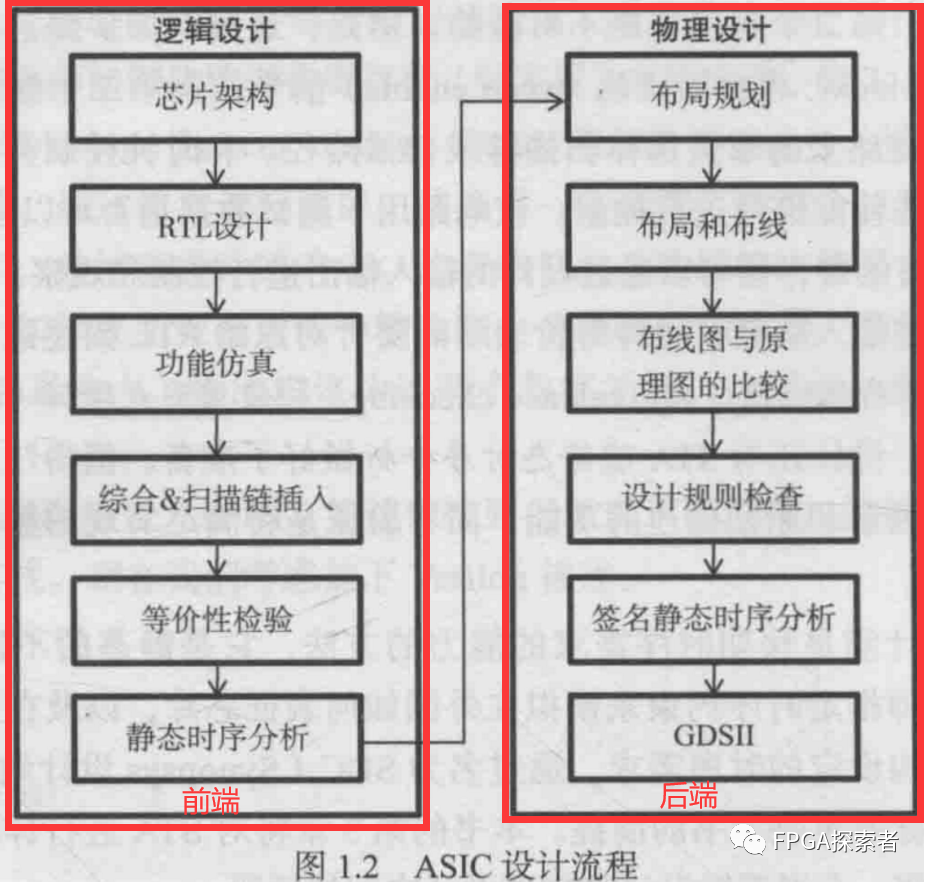

以门级网表(Netlist)生成为分界线,之前称为前端,之后称为后端。

布局布线之前可以认为是前端,布局布线到流片是后端。

** 前端:逻辑设计,RTL ——》 Netlist 门级网表;

**

** 后端:物理设计,Netlist 门级网表 ——》 物理版图;**

Synthesis:综合,主要任务是将 RTL 代码 转成 门级网表;

典型的网表文件由单元(Cell)、引脚(Pin)、端口(Port)、网络(Net)组成。

Synthesis 输入:RTL 代码,工艺库,约束

Synthesis 输出:Netlist 门级网表(用于布局布线),标准延迟文件(用于时序仿真);综合后的报告;

功能仿真

验证 RTL 代码设计的功能正确性,没有加入延时信息,又叫前仿真,工具有 Mentor 的 Modelsim ,Synopsys 的 VCS,Candence 的 NC-Verilog。 在综合、布局布线以后,有加入延时的后仿真(时序仿真)。

Synthesis 综合

逻辑综合的结果(目的)是把 HDL 代码翻译成门级网表 netlist ,工具有 Synopsys 的 Design Compiler(简称 DC) ,门级网表拿去布局布线。

DFT 可测性设计

DFT(Design for Test)可测性设计 ,为了测试而加入的设计,常见技术 :

(1) Scan Chain(扫描链) ,针对时序电路,测试寄存器(Flip-Flop)和组合逻辑;

(2) MBIST (Memory Bulit-in Self Test,内建自测试),测试芯片中存储资源, rom 和 ram,在设计中插入内建自测试逻辑;

(3) Boundary Scan(边界扫描) ,测试封装与 IO、芯片间互联,主要逻辑有 TAP Controller 和 Boundary Scanchain)、JTAG(JTAG 是boundary scan design中用到的一个基本结构)。

ATPG(Automatic Test Pattern Generation,自动测试向量生成,基于扫描链,根据算法推算出应该加载到扫描链上的激励序列和期望序列,这样的序列称为测试向量);

DFT 构建硬件结构,ATPG 生成测试向量。

形式验证

形式验证,属于验证范畴 ,从 **功能上 **对综合后的网表进行验证,常用的是 等价性检验 ,以功能验证后的 HDL 设计为参考,对比综合后的网表功能,检验是否在功能上存在等价性, 保证综合后没有改变原先 HDL 描述的功能 。

形式验证工具有 Synopsys 的 Formality。

STA 静态时序分析

STA 静态时序分析(Static Timing Analyse),属于验证范畴,从时序上对综合后的网表进行验证,检查电路是否存在建立时间、保持时间等违例。

注意 STA 和 形式验证的不同,STA 从时序上验证,形式验证从功能上验证 。

STA 工具有 Synosys 的 Prime Time。

-

【「数字IC设计入门」阅读体验】+ 数字IC设计流程2024-09-25 1162

-

IC数字前端设计实战案例系列pdf2011-12-14 11132

-

IC设计流程2012-01-11 10581

-

IC设计流程介绍2018-08-16 5088

-

数字IC前端和后端有何区别2021-07-28 5741

-

数字IC的设计流程有哪些2021-10-20 2547

-

IC前端设计是指什么2021-11-10 1515

-

数字后端流程与工具2011-10-28 1288

-

数字IC设计流程及工具介绍2018-03-23 35420

-

IC设计前后端流程与EDA工具介绍2018-04-19 12577

-

数字IC设计流程2020-12-09 7995

-

数字IC前端后端的区别,数字IC设计流程与设计工具2021-11-06 2352

-

数字IC与数字IC前端设计2022-09-21 4106

-

ic设计前端到后端的流程 ic设计的前端和后端的区别2023-08-15 6497

-

ic设计是芯片设计吗 数字ic设计流程及工具介绍2023-08-30 6927

全部0条评论

快来发表一下你的评论吧 !