DDR内存终端电源

描述

本设计笔记显示了用于工作站和服务器的高速内存系统的双倍数据速率 (DDR) 同步 DRAM (SDRAM)。使用MAX1864 xDSL/电缆调制解调器电源,电路产生等于并跟踪VREF的终止电压(VTT)。

双倍数据速率 (DDR) 同步 DRAM (SDRAM) 用于工作站和服务器的高速内存系统。这些存储器IC使用2.5V或1.8V电源电压。它们需要等于电源电压一半的基准电压 (VREF = VDD/2)。其逻辑输出通过电阻端接至终止电压 (VTT),该电阻等于并跟踪 VREF。VTT 必须在保持 VTT = VREF ±0.04V 的同时提供或吸收电流。

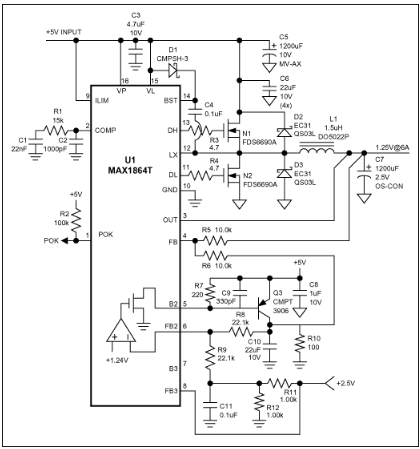

图1所示电路为2.5V和1.8V存储器系统提供终止电压,并提供高达6A的电流。U1 包括一个降压控制器和两个线性稳压控制器,工作在 4.5V 至 28V 的输入电压范围内。其固定的 200kHz PWM 控制器通过拉电流和灌电流来维持输出电压。最大灌电流等于最大源电流,但灌电流没有电流限制。当灌电流时,器件将一些电流返回到输入电源。

图1.该电路产生DDR同步DRAM的终止电压。

为了实现跟踪功能,U1的一个额外的线性稳压器控制器被配置为反相放大器。该放大器将VDD/2(由R11和R12创建)与U1的VREF进行比较,并产生一个误差信号,该信号通过R6施加到U1的FB引脚,从而迫使VOUT跟踪VDD/2。需要10mA负载(R10)来偏置反相放大器以实现精确跟踪。VOUT 可以跟踪 VDD/2 的 VDD/2,范围为 1V 至 4V。

审核编辑:郭婷

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

探索MAX1809:3A、1MHz DDR内存终端电源的卓越之选2026-03-17 156

-

MAX17000A:DDR2和DDR3内存电源管理的理想之选2026-03-12 223

-

德州仪器PTHxx060Y模块:DDR/QDR内存总线终端的理想之选2026-03-05 322

-

DDR5内存与DDR4内存性能差异2024-11-29 6639

-

如何选择DDR内存条 DDR3与DDR4内存区别2024-11-20 13155

-

完整的DDR、DDR2和DDR3内存电源解决方案同步降压控制器数据表2024-03-13 559

-

DDR4和DDR3内存都有哪些区别?2023-10-30 14904

-

DDR 内存终端电源2022-11-18 265

-

用于 DDR 电源及终端的高效率、双通道、±3A同步降压型稳压器符合 DDR / DDR2 / DDR3 标准2021-03-19 1079

-

新唐科技DDR 总线终端稳压系列介绍2020-02-04 2458

-

关于DDR内存电源的特点及应用介绍2018-08-08 6848

-

电源设计小贴士:DDR内存电源2011-12-16 4196

-

DDR2和DDR3内存的创新电源方案2011-07-11 6599

全部0条评论

快来发表一下你的评论吧 !