深度剖析索尼首颗双层图像传感器

MEMS/传感技术

描述

在 IEDM 2021 上,我们首次听说了索尼的这颗双层图像传感器,在2022 年 IEEE VLSI 技术和电路会议上,索尼提供了更多详细信息,现在它已经上市。

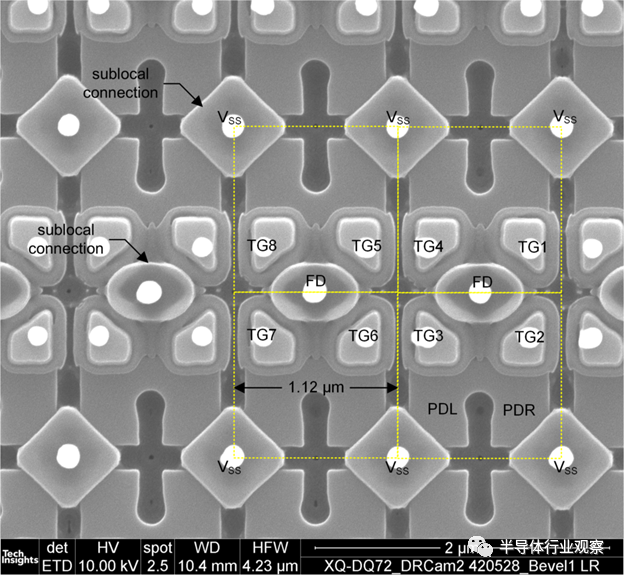

TechInsights 已经让我们第一次看到了“世界上第一个”双层图像传感器,我们在这里展示了我们的初步结果。该设备是在具有 48 MP、1.12 µm 像素间距的索尼 Xperia 1V 智能手机主摄像头中发现的,我们可以确认它具有双光电二极管(每个像素中都有一个左右光电二极管,用于全阵列 PDAF)。die尺寸为 11.37 x 7.69 mm 边到边。

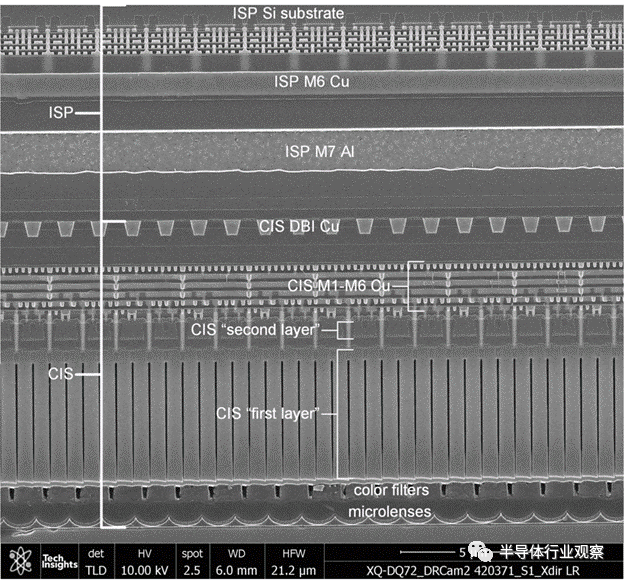

事实上,该传感器实际上具有三层活性硅(active silicon),图像信号处理器 (ISP) 使用直接键合接口 (DBI:Direct Bond Interface) 以传统方式堆叠到“第二层”(我们将尽可能使用索尼的命名法) CMOS 图像传感器 (CIS)。

图 1:传感器的 SEM 横截面表示三个有源硅层。

图 1 显示了阵列的 SEM 横截面。光线通过微透镜和滤色器从图像底部进入。每个像素由孔栅(aperture grid:with compound layers)分隔,以提高量子效率。每个光电二极管之间使用了前深沟槽隔离(Front Deep Trench Isolation),索尼似乎在深沟槽中使用二氧化硅来提高全阱容量(Full Well Capacity)和量子效率(这将通过进一步分析得到证实)。该层还具有平面传输门(planar Transfer Gate),用于将光电荷从二极管传输到浮动扩散区。

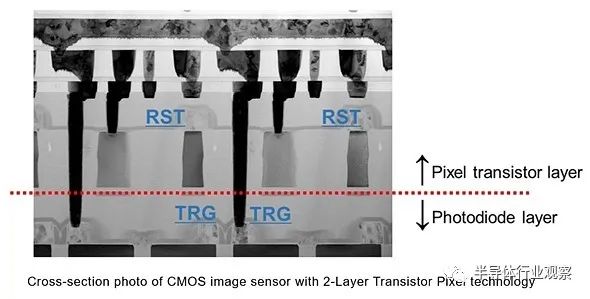

第一层之上是硅的“第二层”,每个像素包含三个晶体管;复位、放大器(Source-Follower)和选择晶体管。这些晶体管位于第二层硅上方,并使用“深度接触”实现与第一层的连接,该接触穿过第二层,基本上形成硅通孔 (TSV)。

最后,ISP 位于第二层的金属化之上,使用混合(Direct)键合进行连接。用于连接 CIS DBI Cu 的 ISP 的铜线在此图像中不可见。

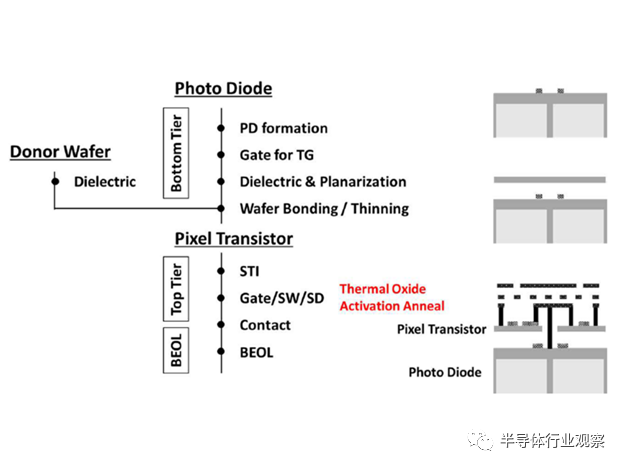

这种结构的关键是一个工艺流程,它可以承受创建热氧化物和激活第二层上的注入所需的热循环。

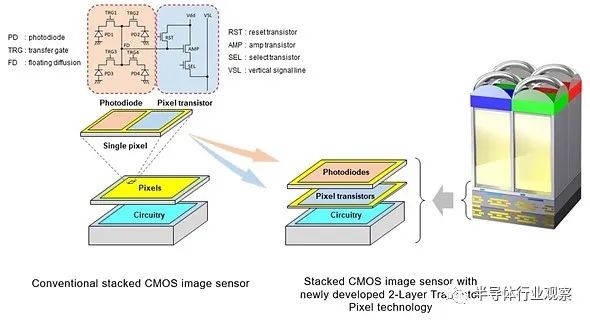

图2是来自本文的图像,显示了流程。形成第一层光电二极管和传输门,第二层进行晶圆键合和减薄。只有这样才能形成第二层栅极氧化物并激活注入。最后,形成深接触,蚀刻穿过第二层,并接触第一层器件。

图 2:“CMOS 图像传感器的 3D 顺序工艺集成”中描述的双层 CIS 工艺流程

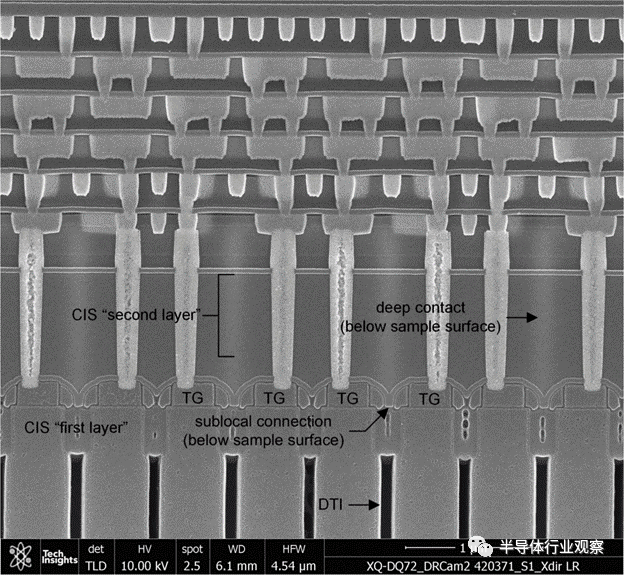

图 3 更详细地显示了第一层和第二层之间的界面。传输门(图中的 TG)连接到第二层的第一金属层。稍长的深接触位于样品表面下方,在图像中部分可见。它们连接第一层和第二层之间的浮动扩散节点。亚局部连接(在样品表面下方)用于将第一层上方的四个光电二极管互连到复位 FET 的源极和 AMP(源极跟随器)FET 的栅极。

图 3:第一层和第二层界面的 SEM 横截面细节。

图 4 详细探讨了亚局域连接。这是衬底层第一层的平面 SEM 图像。黄色框勾勒出像素轮廓,PDL 和 PDR 表示左右光电二极管。一个微透镜覆盖每个像素。指示了亚局部连接,用于互连两个像素的浮动扩散和四个像素的接地。近本地连接似乎是多晶硅;目前正在通过进一步分析证实这一点。

图 4:衬底级像素第一层的 SEM 平面图。

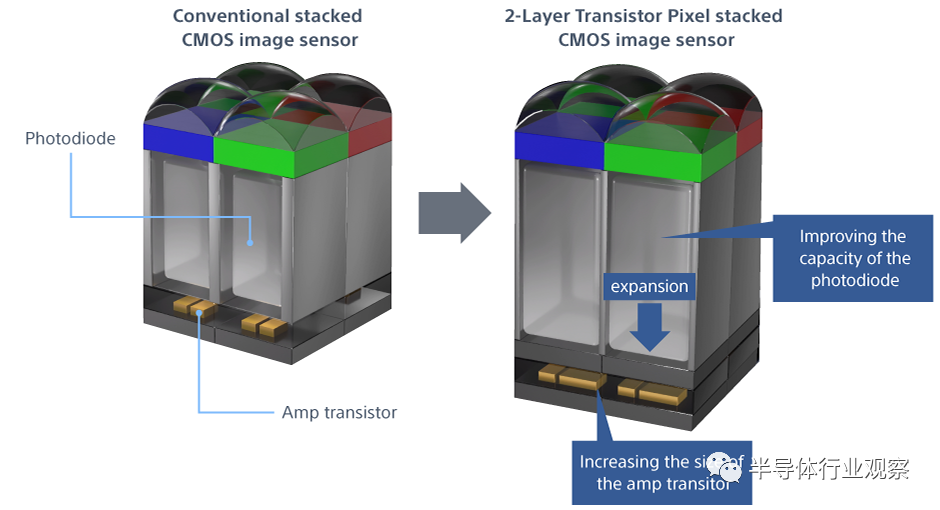

双层结构的动机是多方面的。即使像素间距减小,也可以保持光电二极管的满阱容量。亚局部接触的使用减少了浮动扩散的电容,增加了像素的转换增益。第二层上增加的可用面积允许增加 AMP(源极跟随器)晶体管面积,从而减少该设备通道中产生的噪声(闪烁和电报)。

值得花点时间来欣赏索尼在这里取得的成就。新的工艺流程和深接触技术允许两层有源器件以令人印象深刻的 0.46 μm(中心到中心)的深接触(或硅通孔)间距互连。即使是与 ISP 的混合键合也只有 1.12 μm;

TechInsights 迄今为止看到的最小pitch。在最近的国际图像传感器研讨会上,索尼描述了下一代,它将使用嵌入第一层的“埋入式”亚局部连接和第二层的像素 FinFets(即将发布)。也许我们正在看到真正三维电路的第一阶段,多层硅上的有源器件相互连接。

世界上第一个堆叠 CMOS 图像传感器技术

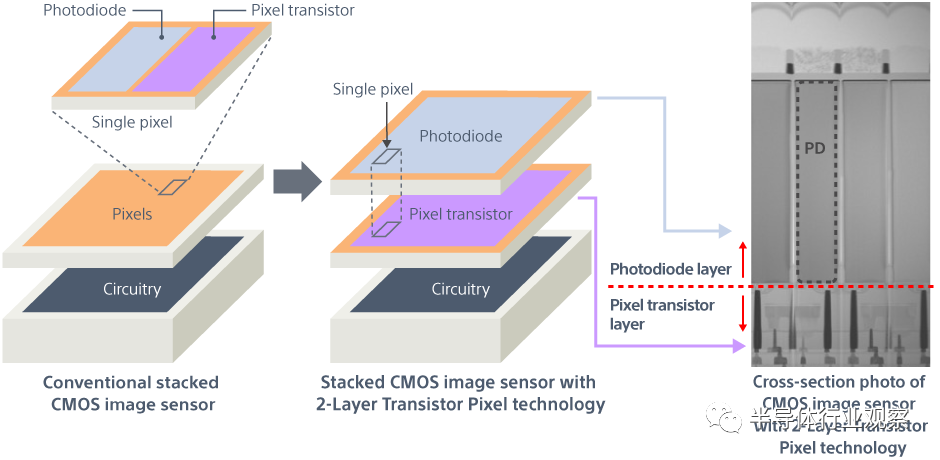

据索尼介绍,其2 层晶体管像素是世界上第一个堆叠 CMOS 图像传感器技术,其像素结构将光电二极管和像素晶体管分隔在不同的基板层上,而不是将两者置于同一基板上的传统样式。这种新结构大约使饱和信号电平相对于传统图像传感器翻倍,拓宽了动态范围并降低了噪声。这种像素结构将使像素即使在较小的像素尺寸下也能显着改善其成像特性。

2层晶体管像素技术是堆叠式 CMOS 图像传感器的进步,它由一个像素芯片组成,该像素芯片由堆叠在形成信号处理电路的逻辑芯片之上的背照式像素组成。在传统的堆叠式 CMOS 图像传感器中,光电二极管和像素晶体管并排放置在同一基板上。SSS 使用其专有的堆叠技术创建了一种结构,其中用于将光信号转换为电信号的光电二极管和位于单独基板上的像素晶体管用于控制一个位于另一个之上的信号。

新结构提高了光电二极管的容量,同时通过将光电二极管和像素晶体管堆叠在单独的基板层上,使饱和信号电平相对于传统图像传感器大约翻了一番。反过来,这将扩大动态范围——相机可以捕捉到的从暗到亮的色调范围。

此外,用于像素晶体管的无光电二极管基板可以为传输门(TRG)以外的像素晶体管提供额外空间,例如复位晶体管(RST)、选择晶体管(SEL)和放大晶体管(AMP)。这为放大晶体管创造了更大的可用区域,从而成功地显着降低了夜间和其他暗处图像容易产生的噪声。

索尼表示,传统 CMOS 图像传感器的光电二极管和像素晶体管占据同一衬底层,而公司的新设计则将光电二极管和像素晶体管分离到两个不同的衬底层中。通过拆分层,光电二极管可以更大,从而产生更高的信号饱和水平(也称为全阱容量),而更大的晶体管会产生更少的噪声。这一结果具有双重优势,既可以增加动态范围,又可以降低噪声。

从工程和制造的角度来看,2 层晶体管像素设计需要纳米级的精度来布置光电二极管和像素晶体管。索尼采用了 3D 顺序集成工艺,而不是传统的完整晶圆键合工艺。光电二极管形成后,将两层粘合在一起,然后光电二极管用于排列第二层晶体管的创建。正如索尼所说,对准精度取决于光刻而不是键合。

该工艺包括其自身的挑战,包括堆叠晶圆后生产过程中的热量。传统的 CMOS 传感器生产需要大约 400°C 的耐热性,而新设计需要更高的耐热性,超过 1,000°C。为了解决这个问题,索尼开发了新的键合技术并制造了晶体管来适应。

通过为每个 photosite 分离光电二极管和晶体管像素,索尼的工程师能够分别优化组件,从而提高噪声性能和动态范围。除了图像质量之外,新设计还承诺研发团队正在努力进行其他改进。

来源:半导体行业观察

审核编辑:汤梓红

-

索尼图像传感器出货量突破200亿2024-12-19 1181

-

索尼图像传感器芯片有哪些2024-10-12 2894

-

国产1.8亿像素CMOS图像传感器破局,挑战索尼垄断2024-08-21 2123

-

打破索尼垄断!业内首颗,国产1.8亿像素全画幅CIS芯片成功试产!2024-08-20 1952

-

索尼推出业内首颗最高像素车载CMOS图像传感器2023-10-12 1455

-

OPPO与索尼共同推出双层晶体管像素技术的LYTIA图像传感器2023-09-13 1517

-

苹果iPhone 15 Pro将搭载索尼新一代图像传感器2022-12-13 1043

-

数码相机图像传感器,仍是索尼的天下2022-10-26 6439

-

日月光已进入索尼汽车CMOS图像传感器后端供应链2020-11-17 2925

-

安森美坐上汽车CMOS图像传感器头把交椅2020-05-06 3249

-

索尼图像传感器桥接的解决方案2020-04-30 2425

-

索尼试图提高图像传感器产量2019-10-30 3339

-

索尼首席执行官表示不会拆分图像传感器业务2019-09-18 3370

-

索尼在东京发布最新图像CMOS传感器,IMX4182018-10-23 6373

全部0条评论

快来发表一下你的评论吧 !