锗、硅、SiNx薄膜的各向同性等离子体蚀刻

电子说

描述

引言

CMOS和MEMS制造技术,允许相对于其他薄膜选择性地去除薄膜,在器件集成中一直具有很高的实用性。这种化学性质非常有用,但是当存在其他材料并且也已知在HF中蚀刻时,这就成了问题。由于器件的静摩擦、缓慢的蚀刻速率以及横向或分层膜的蚀刻速率降低,湿法化学也会有问题。

通过具有各向同性气相蚀刻化学的附加优点,可以实现硅层的高蚀刻率。这种技术要求在氟中可蚀刻的材料不使用高选择性薄膜,如二氧化硅,或光刻胶,或植入不可蚀刻的掺杂剂。

英思特通过使用NF3和NO的更简单的蚀刻化学来研究CDE中Ge和Si之间的蚀刻选择性,目的是将Ge用作光学或MEMS器件的释放层。通过利用上游等离子体中的NF3和Ar,可以产生大量的氟自由基,从而用于ge和Si蚀刻,而不会增加碳化学的复杂性。

实验与讨论

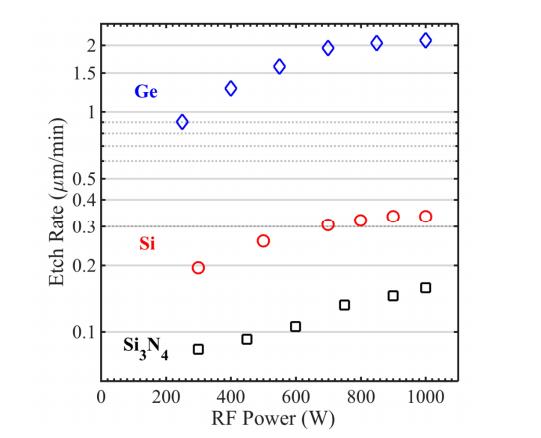

英思特通过改变RF等离子体功率来进行CDE蚀刻的初始表征。在CDE中用400sccm的Ar、75sccm的NF3、70Pa的压力在不同的RF功率下进行各向同性蚀刻;硅晶片和硅晶片上的氮化硅被蚀刻30秒,硅晶片上的锗被蚀刻8秒(图1)。接近1000W时,氟自由基出现饱和状态,锗、硅和氮化物的蚀刻速率分别达到2.1µm/min、320纳米/分钟和158纳米/分钟。

图1:随着射频电源功率的变化的蚀刻率

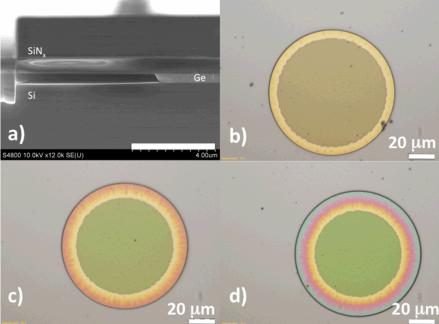

在覆盖蚀刻速率测量之后,我们利用结构ICP RIE刻蚀到硅中的晶圆来研究CDE中Ge的横向蚀刻特性。其结构由SiNx(400nm)/Ge(400nm)/Si的薄膜堆制成,并蚀刻1.7µm,总柱高度为2.5µm。然后在CDE中横向蚀刻15、30和45秒,在直径100m的柱上光学测量后蚀刻Ge(图2)。

图2:夹在SiNx和晶体硅衬底之间的横向蚀刻的光学测量

结论

干法蚀刻释放层是集成光子学和MEMS应用的基本工具,这项工作详细说明了在硅和氮化硅存在下锗薄膜的各向同性干法刻蚀。英思特通过使用三氟化氮和Ar的化学方法,将Ge、Si、SiNx和晶体硅的覆盖层以及图案CVD层进行各向同性蚀刻。

随着等离子体功率的增加,蚀刻速率增加;使用O2降低,氧化暴露的Ge和Si受到抑制,但不阻止GeF4和四氟化硅的形成。这项工作不是将N2和O2注入等离子体,而是通过将NO直接注入处理室,来产生基本的N和O自由基。

英思特研究发现,Si和SiNx的蚀刻速率增加,但由于氧-氮化物或氮化物锗的形成,导致蚀刻发生延迟。在纯氟蚀刻化学存在的情况下,我们几乎没有观察到α-Si、Si衬底或氮化硅的蚀刻,并且Ge蚀刻显著高于覆盖Ge薄膜蚀刻速率。对于暴露的硅和氮化硅,除了轻微延迟蚀刻前部和轻微增加蚀刻速率外,添加NO在蚀刻方面没有任何优势。

江苏英思特半导体科技有限公司主要从事湿法制程设备,晶圆清洁设备,RCA清洗机,KOH腐殖清洗机等设备的设计、生产和维护。

审核编辑:汤梓红

-

金属蚀刻残留物对对等离子体成分和均匀性的影响2022-05-05 1502

-

等离子体蚀刻和沉积问题的解决方案2022-05-19 2523

-

雷尼绍测头为什么具有各向同性2024-06-01 15251

-

PCB电路板等离子体切割机蚀孔工艺技术2017-12-18 3074

-

PCB板制作工艺中的等离子体加工技术2018-09-21 2890

-

微波标量反射计可测量大范围的等离子体密度2019-06-10 1501

-

低温等离子体废气处理系统2022-04-21 12362

-

TDK|低温等离子体技术的应用2022-05-17 2988

-

等离子体应用2022-05-18 3703

-

各向同性和各向异性工艺如何用于改善硅湿蚀刻2022-03-09 3459

-

常见的各向同性湿法刻蚀的实际应用2022-10-08 7439

-

真空等离子清洗机的制造商正在引入氧和氢等离子体来蚀刻石墨烯2022-06-21 1465

-

铝等离子体蚀刻率的限制2023-06-27 1277

-

锗化硅(SiGe)和硅(Si)之间的各向同性和选择性蚀刻机制2024-02-21 3967

-

什么是电感耦合等离子体,电感耦合等离子体的发明历史2024-09-14 3127

全部0条评论

快来发表一下你的评论吧 !