IIC总线调试故障具体原因的定位过程及解决方法

接口/总线/驱动

1164人已加入

描述

一、问题的提出

在某项目研发过程,软件与FPGA联合调试xx芯片IIC总线过程中,遇到故障现象:软件发起一次IIC操作后,未收到ACK应答响应。通过查询FPGA内部寄存器,可获知以下信息:软件当前发起的IIC写操作发送字节数为4,FPGA已发送的字节数为1,因此FPGA未向软件上报ACK应答响应;但通过读取数据寄存器确认软件已将4个字节数据正确下发给FPGA。经过以上分析,当前IIC总线通信失败的基本原因已定位到FPGA仅成功发送了一个字节,其余三个字节未发送。下面主要描述一下具体原因的定位过程及解决方法。

二、解决思路及实践情况

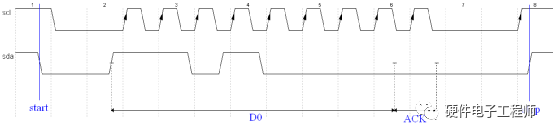

FPGA与xx芯片IIC总线接口管脚为SCL以及SDA。通过示波器观测SCL与SDA信号,时序波形如图1所示,IIC总线状态从开始(START)状态跳转到发送延迟状态,再跳转到发送状态,经过8个SCL时钟周期将第一个字节数据(D0)发送完成,第9个时钟周期收到从设备(xx芯片)反馈回的ACK应答响应,之后跳转到结束延迟状态,最后跳转到结束状态。因此,当前故障现象为:FPGA成功发送了第一个字节,并且总线上也得到了从设备的ACK应答响应,但是FPGA并没有继续发送后续字节。

图1

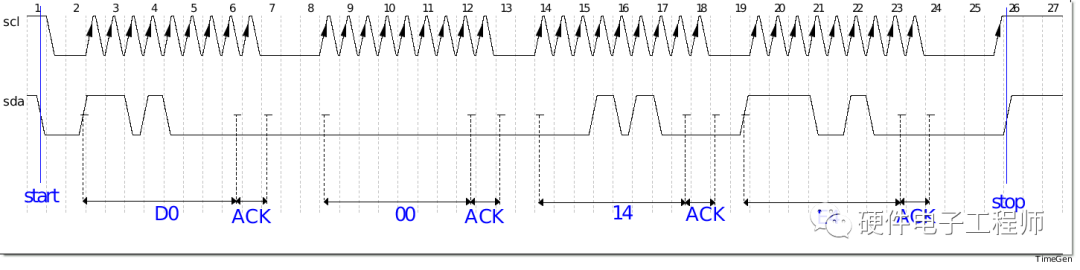

首先分析到的原因是FPGA是否检测到从设备反馈回的ACK应答响应。通过走查代码,发现代码编写过程中对SDA管脚做了如下处理:assign PPC_SDA_7 = sda[6]。问题出于此,SDA管脚应该为双向管脚,上述处理导致FPGA仅发送数据给xx芯片,但不接收xx芯片发送的数据,因此xx芯片反馈回的ACK信号FPGA并未检测到,因此不再发送后续3个字节。经过修改代码,重新测试IIC总线,验证通过,正确的IIC总线时序如图2所示。

图2

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

电机常见故障分析及解决方法2025-04-25 6490

-

iic协议常见故障及解决方法2025-02-05 5685

-

无功补偿故障原因及解决方法2025-01-29 3660

-

can总线的故障波形有哪些2024-06-16 4116

-

网卡硬件故障及解决方法2023-12-27 10486

-

LED灯闪烁的原因 LED灯闪烁故障解决方法2023-12-11 56092

-

变频器过热的故障原因和解决方法2023-10-24 10710

-

螺丝供料器不送螺丝的故障原因及解决方法2021-09-24 7195

-

常用的电路故障分析与定位方法2020-10-30 2256

-

电路故障分析与定位的几个常用方法2020-10-12 3032

-

加湿器不喷雾的原因及解决方法2020-04-04 32841

-

传感器的故障原因和解决方法2018-11-09 2237

-

一文解读IIC总线的FPGA实现原理及过程2018-05-31 7328

-

电动机噪声大或声音异常故障原因及解决方法2007-10-13 2384

全部0条评论

快来发表一下你的评论吧 !