请用Verilog分别实现1位半加器和1位全加器

电子说

描述

1.原理

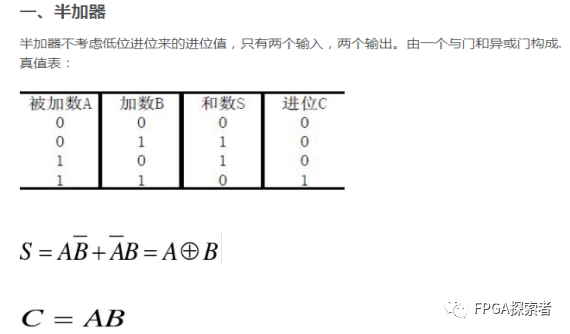

半加器

全加器

当多位数相加时,半加器可用于最低位求和,并给出进位数。第二位的相加有两个待加数和,还有一个来自前面低位送来的进位数。这三个数相加,得出本位和数(全加和数)和进位数。这种就是“全加"真值表:

2.编程思路

(1)根据真值表编写

按照半加器和全加器的真值表写出输出端的逻辑表达式,对半加器,输出的进位端是量输入的“与”,输出的计算结果是量输入的异或;对全加器,也按照逻辑表达式做。

//半加器模块

module adder_half(

inputa,

inputb,

output regsum,

output regcout

);

//这里的always @(*)搭配里面的“=”阻塞赋值符号

//实现的效果和 assign sum = a ^ b; assign cout = a & b;是一样的

always @(*)

begin

sum = a ^ b;

cout = a & b;

end

endmodule

全加器:

module all_adder(cout,sum,a,b,cin);

input a,b,cin;

output sum,cout;

wire sum,cout;

assign sum=a^b^cin;

assign cout=(a&b)|(a&cin)|(b&cin);

endmodule

3.问题汇总

(1)`timescale 1 ns/1 ps

timescale是verilog中的一种时间尺度预编译指令,用来定义仿真时的时间单位和时间精度,左边是时间单位,右边是时间精度,时间单位是用于编写激励文件,时间精度是显示时的刻度,比如#100也就是100ns。时间精度不能大于时间单位,比如timescale 1 ns/1 ps是正确的,而timescale 1 ps/1 ns是错误的。

(2)#({$random}%100)

首先,#代表延时,这个语句表示延时随机的一个时间,结合`timescale 1 ns/1 ns是延时随机的ns。

$random 是 verilog 中产生随机数的系统函数,在调用时返回一个 32 位的随机数,是带符号的整形数。有几种用法:

random 和random()意义一样,都是产生随机数;

$random%100 在-99 到 99 之间产生随机数;

{$random}%100 采用位拼接符,在 0 到 100 之间产生随机数;

如 seed =10, $random(seed) 根据 seed 值产生随机数,而后 seed 值也会更新。

(3)add t0(.cin(cin), .a(a), .b(b), .sum(sum), .count(count));

例化的格式,先建立一个叫add的模块(module),有5个引脚,分别是cin/a/b/sum/count,例化的模块叫做t0,比较简单的例化方式就是如上所示的,括号外的引脚与括号内的引脚名称完全一致,无需区分。

实际上,括号外的引脚名称代表的是模块定义时的引脚,括号内的引脚是目前实际使用的引脚名称,如可以将@大神袁的测试文件改为:

`timescale 1 ns/1 ns

module top_tb();

reg a1;

reg b1;

wire sum1;

wire count1;

initial

begin

a1 = 0;

b1 = 0;

forever

begin

#({$random}%100)

a1 = ~a1;

#({$random}%100)

b1 = ~b1;

end

end

top t0(.a(a1), .b(b1), .sum(sum1), .count(count1));

endmodule

(4)对于延时,可以采用直接赋值的延时,如#5,使用随机延时目前暂时不常用。

当仿真到想结束时,可以在initial块的最后加$finish(此处可参考@大神李),即调用系统函数结束仿真,否则,仿真在ModelSim中会一直进行下去,不方便观察(在Vivado中设置的第一次仿真结束时间停止,默认1ns)。

此外,这里建议使用stop来代替finish,即停止仿真,在ModelSim中是暂停了仿真,而$finishi则可能会退出,看不到仿真波形。

-

半加器和全加器的功能特点2024-10-18 6825

-

什么是8位全加器和8为带超前进位的全加器?2022-02-09 1628

-

基于Quartus II软件完成一个1位全加器的设计2021-12-17 2267

-

Verilog数字系统设计——复杂组合逻辑实验2(8位全加器和8为带超前进位的全加器)2021-12-05 754

-

怎样去设计一种基于FPGA的1位全加器2021-09-17 1773

-

FPGA入门——1位全加器设计 精选资料分享2021-07-26 1637

-

请问Quartus2中的用一位全加器来实现四位全加器2019-03-06 6345

-

全加器是什么?全加器和半加器的区别?2018-07-25 77237

-

什么是一位全加器,其原理是什么?2010-03-08 78543

全部0条评论

快来发表一下你的评论吧 !