典型3D NAND闪存结构技术分析

存储技术

描述

几十年来,NAND 闪存一直是低成本和大密度数据存储应用的主要技术。这种非易失性存储器存在于所有主要的电子终端使用市场,例如智能手机、服务器、个人电脑、平板电脑和 USB 驱动器。在传统的计算机内存层次结构中,NAND 闪存距离中央处理器 (CPU) 最远,与静态随机存取存储器 (SRAM) 和动态 RAM (DRAM) 相比,众所周知,它相对便宜、速度慢且密度大。

这种存储技术的成功与其不断扩展密度和成本的能力有关——这是 NAND 闪存技术发展的主要驱动力。大约每两年,NAND 闪存行业就会显着提高位存储密度,以增加的 Gbit/mm²表示。

在这个发展过程中还引入了几项技术创新以维持这一趋势线。向三维的过渡可以说是最令人印象深刻的创新。在 3D NAND 闪存中,存储单元堆叠形成垂直串,单元由水平字线寻址。其他值得注意的创新包括增加每个单元的位数(最多四个)以及从浮栅晶体管过渡到用于存储操作的电荷陷阱单元。

图 1 – 典型 3D NAND 闪存结构的表示(BL=位线;WP=字板;BSP=底部选择板;SP=源板;TSL=顶部选择线)

最先进的:环绕式垂直沟道;多达 300 个字线层

尽管并非所有存储器制造商都在追求,但电荷陷阱单元是当今大多数 3D NAND 结构的基础. 该存储单元类似于 MOSFET 晶体管,在晶体管的栅极氧化物(氧化物-氮化物-氧化物 (ONO) 堆栈)中插入了一小层氮化硅 (SiN)。SiN 层包含许多可以保持静电荷的电荷捕获位点。当多晶硅栅极正偏置时,来自沟道区的电子隧道穿过氧化层并被困在SinN层中。这提高了晶体管的阈值电压。Cell的状态可以通过跨源/漏节点传递电压来测量。如果电流流动,则电池处于“无俘获电子”状态(对应1)。如果未测量到电流,则cell处于“俘获电子(或 0)状态。

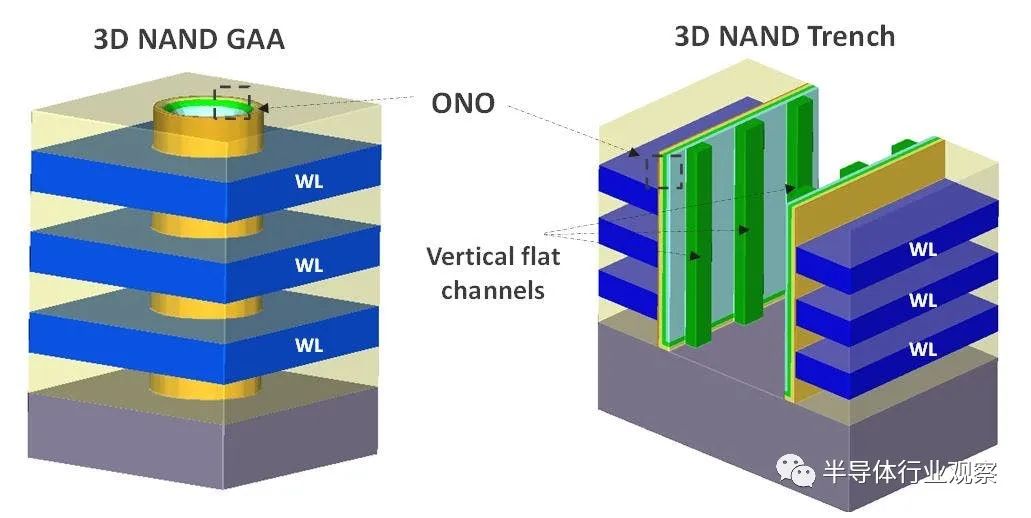

由于存储窗口不足,电荷陷阱单元未能在早期的 2D NAND 平面配置中引入,存储窗口通过编程和擦除之间的阈值电压差异来衡量。但在 3D NAND 结构中,这种存储单元充分发挥了潜力,这要归功于环栅 (GAA) 垂直通道实现方法。在此 GAA 配置中,栅极堆叠完全环绕通道。这种圆柱形几何形状在隧道氧化物中产生增强的场效应。这导致更大的载流子注入到捕获层,增强了编程/擦除窗口。

GAA 制造通常从生长氧化物/字线层堆栈开始。接下来,使用先进的干法蚀刻工具通过堆叠向下钻孔来形成圆柱形孔。然后沿着孔的侧壁沉积隧道 (O) 和捕获 (SiN) 层以及多晶硅沟道。 最近,一些主要厂商宣布推出基于 3D-NAND 的产品,这些产品最多可堆叠 300 个字线层,预计这种增加层数的趋势将在未来几年继续下去。

进一步增加位存储密度的方法

在当前十年中,内存制造商将把传统的 GAA NAND 路线图推向极限。根据最乐观的预测,到本世纪末,层数将增加到 1,000,占 100Gbit/mm 2位存储密度。然而,相对于历史密度缩放路线图,这是几年的放缓。 增加层数会带来更高的处理复杂性和成本,挑战沉积和蚀刻工艺,并导致应力在层内积聚。为了克服这些挑战,业界正在引入一些互补的工艺“技巧”以最终获得1,000 层。这些包括将层数拆分为两个(或更多)堆叠层,进一步增加每个单元的位数,提高阵列效率,并减少 GAA 单元的 xy 间距。还有一种趋势是优化不同晶圆上的外围电路,并使用晶圆对晶圆键合技术将其连接到存储器阵列。然而,这些创新不足以控制不断增长的加工成本,因此,额外的追求z 间距缩放。Z 间距缩放涉及降低层堆叠中涉及的所有材料的高度,包括字线金属和氧化物。

2030 年:引入 3D 沟槽单元架构

到 2030 年,在 GAA NAND 闪存微缩已经饱和之后,imec 预计将引入一种新的架构来连接电荷陷阱单元:沟槽单元架构(trench cell architecture)。通过这种架构,3D NAND 摆脱了圆形 GAA 存储单元几何结构。相反,这些单元是在沟槽的侧壁上实现的——类似于在其侧面倾斜的平面配置——在沟槽的相对壁上有两个晶体管。这种下一代 NAND 闪存单元架构不仅将提供所需的位存储密度飞跃;它也被认为可以降低成本。然而,就像在 2D 平面配置中一样,栅极不再完全包裹在沟道周围。因此,存储器制造商担心编程/擦除窗口不足。

图 2 –(左)3D NAND GAA 和(右)沟槽器件(在 2023 IMW 上展示)的 3D 示意图。

沟槽与 GAA 单元架构的编程和擦除行为

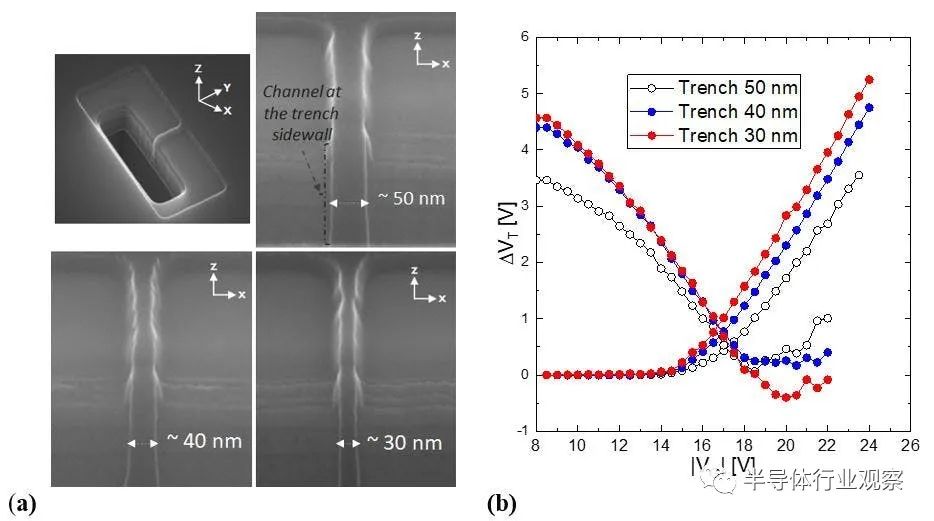

在 2023 年 IEEE 国际存储器研讨会 (2023 IMW) 上,imec 展示了沟槽单元与GAA 存储器单元存储器操作的实验比较。两种 NAND 闪存变体都在同一晶圆上处理,即内部开发的具有多晶硅栅极和三个字线层的 3D NAND 测试载体。代替圆柱形孔,沟槽特征(300nm 宽和 1μm长)被蚀刻到沟槽结构的字平面堆栈中。沿着沟槽的侧壁形成三个垂直平坦的多晶硅沟道(沟道宽度为 50nm - 200nm),并制造源/漏结。 如果不进行优化,沟槽cell的性能将不如 GAA cell。它们具有非理想的编程和擦除效率,这分别反映在增量步进脉冲编程 (ISPP) 和擦除 (ISPE) 曲线的斜率和起点上。这转化为更小的编程/擦除窗口。在擦除方面,ISPE 曲线还显示了擦除饱和度水平的下降。

迈向 5V 内存窗口

存储窗口不佳可以解释为缺乏曲率引起的场效应,在 GAA 的情况下,这会增加载流子注入到俘获层中。针对这一缺点,imec团队想出了一个创新的解决方案,即缩小沟槽器件的沟道宽度。沟道宽度缩放有望扩大通道边缘周围形成的弯曲高注入区域的影响。换句话说,在沟道宽度大大减小的情况下,从几何角度来看,沟槽单元开始类似于 GAA 单元。 另一方面,擦除饱和水平的降低主要由来自栅极的寄生电子注入决定。这可以通过精心设计栅极堆叠和集成金属栅极来抑制。 Imec 通过实验表明,对于具有缩放沟道宽度(低至 30nm)的沟槽器件,结合替代的Hing k 衬里(linear)材料(例如 ZrO2 或 HfO2 而不是Al2 O3 ),可以实现更好的存储操作,一个工程隧道氧化物和金属栅极的集成。对于大多数研究条件,展示了高达 5V 的记忆窗口,2V 的改进——不影响保留和循环行为。该团队目前正致力于进一步改进编程和擦除操作。

图 3 – (a) 不同沟道宽度的沟槽;(b) 编程和擦除特性,在更小的沟道宽度下表现出改进(如 2023 IMW 所示)。

超高位存储密度

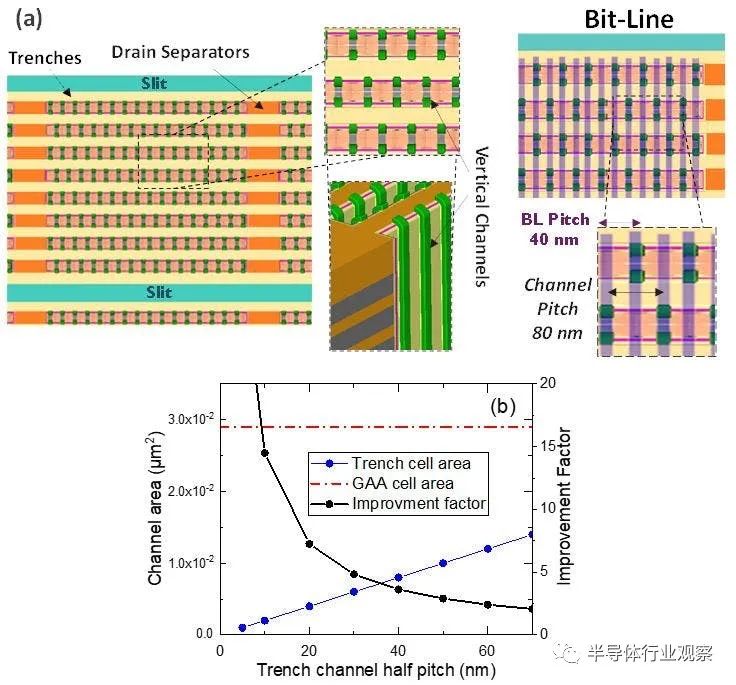

在展示了具有良好存储特性的沟槽存储单元后,下一步是研究潜在的与行业相关的集成方案,以堆叠更多层。预计这样的工艺流程类似于 GAA 工艺流程,增加了一个额外的模块:蚀刻沟槽侧面的垂直平坦通道条纹。如果可以为这个具有挑战性的蚀刻步骤找到工艺解决方案,imec 提出了3D 沟槽工艺流程的仿真,具有 220nm 间距的沟槽,每个沟槽宽 100nm,长约 1μm。为了确保高位密度,该流程通过蚀刻 25 纳米宽的沟道条纹和 80 纳米间距来完成。

图 4 – (a) 沟槽最终设计结构的顶视图,以及 (b) 沟槽架构的单元密度改进系数(如 2023 IMW 所示)。 从最终的设计结构来看,沟槽架构的单元密度估计是GAA 参考的三倍。预计这将随着通道间距缩放而进一步改善。基于这些结果,3D 沟槽架构可被视为未来 3D NAND 闪存的潜在突破,其位存储密度将远超 100Gb/mm²。

编辑:黄飞

-

什么是3D NAND闪存?2023-03-30 4704

-

不要过于关注3D NAND闪存层数2020-12-09 3921

-

未来的3D NAND将如何发展?2020-11-20 3506

-

3D NAND闪存技术未来发展趋势分析2020-11-19 3949

-

美光发布176层3D NAND闪存2020-11-12 4031

-

美光宣布了其第五代3D NAND闪存技术2020-11-11 3288

-

芯片的3D化历程2020-03-19 2235

-

3D NAND技术资料分享2019-09-12 2945

-

半导体行业3D NAND Flash2018-10-08 873

-

在3D NAND新产品技术进入市场之际加快发展步伐2018-06-20 5310

-

3D NAND 将会在今年大放异彩2017-05-03 1664

-

三星48层3D V-NAND闪存技术揭秘2016-07-13 7733

-

3D垂直NAND闪存 轻松提升SSD容量2013-08-29 2954

-

SanDisk:3D NAND闪存开始出击2013-07-25 1673

全部0条评论

快来发表一下你的评论吧 !