如何对SAR ADC电源进行排序

描述

介绍

有时我们知道,为集成电路上电只是将所需的电压或电流参数施加到电路上,我们就可以开始了。我们很少使用高精度或高性能系统。它在电路中有许多不同的部分,这些部分是正确级联的,并且需要一系列向电路的不同部分施加功率。否则,它将无法实现其优化性能。最坏的情况是它会损坏IC或ADC。

电源排序可以防止损坏并延长电源以及设计中任何敏感IC和FPGA的使用寿命。除了控制启动时序以控制电流消耗外,电源轨还需要保持在FPGA的耐压要求范围内。随着新工艺技术的出现,这些容差变得更加严格,以至于可能需要3%的总内核电压容差。可以通过多种方式对系统中的电源进行排序:

使用复位IC进行排序

模拟上/下音序器

同步测序

任何设计都必须包括电源排序,特别是对于需要多个电源轨的复杂系统。

逐次逼近寄存器(SAR)ADC的谜团之一,或者至少是造成相当混乱的原因之一是在系统级计算其确切的功率要求。数据表可能会对此规范造成混淆。SAR ADC提供了一种低功耗方法来测量输入信号。功耗通常与采样率成比例,因此测量系统非常高效。

模拟和数字电源

数字控制还可以简化校准参数,这些参数可以编程,而不是调整模拟电源中的电位器。不利的一面是,电源的数字控制涉及许多操作参数,并且可能非常复杂。它需要带有复杂软件的DSP(数字信号处理器),这可能很难排除故障。

另一方面,模拟控制已经使用了50 +年,是一种久经考验的方法。模拟电源稳定且不易出现毛刺,尽管它们的灵活性有限。参数在设计阶段定义,以后无法更改。

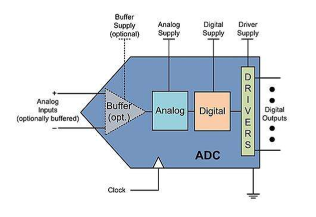

SAR ADC 电源输入

SAR ADC需要数字电源(DVDD)、模拟电源(AVDD)和数字输入/输出电源(OVDD)。(AVDD) 和 (AVSS) 是电路模拟部分的电源和接地。基准电压(Vref)是一种模拟基准电压,允许用户配置ADC的上限。(Vref)代替AVDD来提供ADC基准电压源。ADC 范围介于 AGND 和 (Vref) 之间,即使输入信号的峰值幅度小于电源电压,您也可以使用 ADC 的全动态范围。

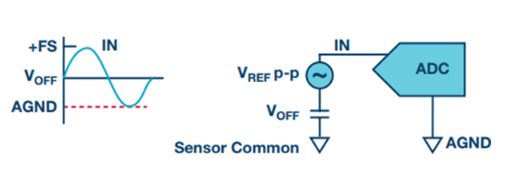

单极性和双极性SAR ADC

单极SAR

最简单的模拟输入类型是单端输入。在这种情况下,只需一根导线即可将信号从源端传输到ADC。将有一个输入引脚,没有直接返回或检测路径返回到信号源。转换结果将相对于ADC的接地引脚生成。在这种情况下,您的电源只会从 0v 或 GND 摆动到 AVDD。

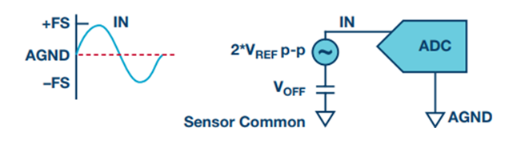

双极SAR

如果SAR ADC是双极性单端配置,则相对于地,允许的信号摆幅介于正满量程和负满量程之间。同样,满量程通常由ADC基准输入设置。在这种情况下,您的供应将从 AVSS 转向 AVDD。

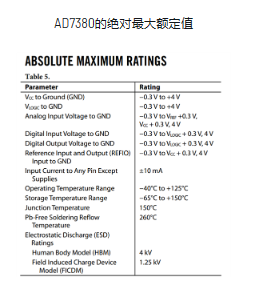

绝对最大额定值

ADI公司的所有数据手册中均提供绝对最大额定值部分。它说明了可以应用于器件引脚或外壳的最大电压、电流或温度,以避免造成损坏。从这里,绝对最大额定值也可以确定SAR ADC的功率时序

AD7380的绝对最大额定值

如何确定SAR ADC的时序的步骤:

结论

示例部件:AD7381-4

为了比较包含电源时序规则的其他SAR ADC,我们在此提供了一个示例SAR ADC,它是AD7381-4数据手册,其中包括向ADC施加电源的规则。

审核编辑:郭婷

-

SAR ADC的工作原理是什么?SAR ADC的优点和缺点有哪些?2023-09-08 20979

-

SAR ADC是什么 SAR ADC应用优势2023-02-22 7467

-

SAR ADC的隔离2023-01-24 1878

-

解释SAR ADC电源规格2023-01-03 1555

-

SAR ADC输入注意事项2022-11-21 782

-

SAR ADC的原理以及SAR ADC驱动电路设计要点2022-04-28 21589

-

这个SAR ADC怎么样?2021-06-24 1937

-

通用SAR ADC2021-04-30 945

-

SAR ADC驱动程序2021-04-23 1023

-

SAR ADC输入类型2021-04-22 949

-

SAR型ADC应用2019-08-06 4225

-

PSoC 5LP ADC SAR序列,速率为1MHz怎么实现2019-02-21 1820

-

SAR与ADC不同输入类型2018-09-11 3132

-

序列 SAR ADC 使您能够在 PSoC 4 上配置和使用不同操作模式的 SAR ADC2017-10-10 877

全部0条评论

快来发表一下你的评论吧 !