跨时钟域信号该如何处理呢?

电子说

描述

1

跨时钟域是如何产生的呢?现在的芯片(比如SOC,片上系统)集成度和复杂度越来越高,通常一颗芯片上会有许多不同的信号工作在不同的时钟频率下。比如SOC芯片中的CPU通常会工作在一个频率上,总线信号(比如DRAM BUS)会工作在另一个时钟频率下,而普通的信号又会工作在另外的时钟频率下。这3个不同时钟频率下工作的信号往往需要相互沟通和传递信号。

不同时钟域下的信号传递就涉及到跨时钟域信号处理,因为相互之间的频率、相位不一样,如果不做处理或者处理不当,如下图所示的时钟域CLK_A的数据信号A可能无法满足时钟域CLK_B的setup/hold时间,可能导致:

1.数据丢失,无法采到预期中的信号;

**2.**亚稳态的产生。

从而导致某个电路模块或者整颗IC无法工作。

2

那么,常见的跨时钟域信号处理方法都有哪些呢?有如下的三种:

- 两级DFF同步器

- 握手协议

- 异步FIFO

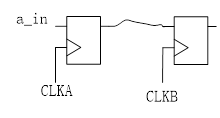

最简单的单比特信号处理通常采用两级DFF串联进行同步,如下图所示:

从时钟域A(CLKA)传过来的信号a_in, 直接用时钟域B CLKB采用很容易产生亚稳态,用两级DFF 敲过后再使用就可以把亚稳态概率降到一个合理的值。

很多人可能会问,为什么是两级DFF呢?一级或者三级DFF行不行呢?这里有一个平均失效间隔时间MTBF(Mean Time Between Failure)的考虑。MTBF时间越长,出现亚稳态的概率就越小,但是也不能完全避免亚稳态。注意采样时钟频率越高,MTBF可能会迅速减小。

有文献给出的数据:对于一个采样频率为200Mhz的系统,如果不做同步MTBF是2.5us,一级DFF同步的MTBF大概是23年,两级DFF同步的大约MTBF大概是640年,MTBF越长出错的概率越小。所以一级看上去不太稳,二级差不多够用了,至于三级可能会影响到系统的性能,而且增加面积,所以看上去没什么必要。

两级DFF同步器听起来够简单的吧?这个方法虽然很简单,但是很多人用起来还是常常会犯错。

3

错误1 :时钟域A的组合逻辑信号直接敲两级DFF同步到时钟域B

如下图(1)所示虽然时钟域A的逻辑信号c0 传输到时钟域B的时候,也用了两级DFF 同步器,但我们知道组合逻辑电路各个输入信号的不一致性以及组合逻辑内部路径的延时时间不一样,运算后的信号存在毛刺如图(2),而我们又无法预先知道CLKB 的上升沿何时会到来,CLKB 采样到的信号就无法预知,这显然不是我们想要的结果。

因此,要想CLKB 能采到稳定的信号,时钟域A的信号必须是经过CLKA 敲过,在一个时钟周期内是稳定的信号,如图(3)所示:

4

错误2 : Clock-gating enable 信号没有经过异步处理

在下图中a_in 信号经过CLKA的DFF敲过,再送到两级DFF 同步器处理,完全没毛病。但是F2的使能信号EN是从时钟域A来的,当EN信号变化的时候,由于时钟域不一样,无法保证使能之后的CLKB信号采样数据时满足setup/hold time 要求,这时F2输出信号也就变得无法预测了。

两级同步器处理单比特信号虽然比较简单,但还是要注意它的使用方法,不要犯上面的错误哦。

-

如何处理跨时钟域这些基础问题2024-01-08 1521

-

FPGA跨时钟域处理方法(二)2023-05-25 1893

-

揭秘FPGA跨时钟域处理的三大方法2022-12-05 2680

-

关于跨时钟域信号的处理方法2022-10-09 8588

-

如何处理好跨时钟域间的数据呢2021-11-01 1735

-

介绍3种方法跨时钟域处理方法2021-09-18 23611

-

如何处理好FPGA设计中跨时钟域间的数据2021-07-29 1727

-

三种跨时钟域处理的方法2021-01-08 2348

-

如何处理好FPGA设计中跨时钟域问题?2020-09-22 2401

-

跨时钟域信号如何处理?2019-02-04 11896

-

如何处理跨时钟域信号?2018-09-25 8511

-

跨时钟域信号的几种同步方法研究2012-05-09 1353

-

FPGA设计中有多个时钟域时如何处理?2012-02-24 3627

全部0条评论

快来发表一下你的评论吧 !