Net Delay在整个路径延时的占比是什么情况呢?

电子说

描述

绕线延时(Net Delay)是怎么计算出来的呢?Net Delay在整个路径延时(Path Delay)的占比又是什么情况呢?针对关键路径,工具会如何降低Net Delay呢?下面我们就来逐步阐述。

Net Delay占比多高?

Path Delay = Cell Delay + Net Delay

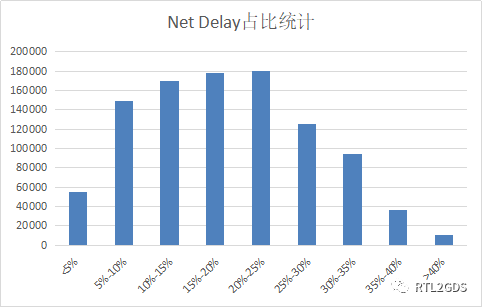

你可能好奇Net Delay所占的比重如何?这个跟工艺和设计是相关的,但是总体上的趋势是,随着工艺尺寸缩小,Net Delay占比越来越高。下面是Net Delay占比的分布图,统计对象是基于12nm工艺的一个SoC设计中的100万条路径。可以看出,很大一部分的Path中的Net Delay占比超过20%。

Net Delay 计算公式

为了计算Net Delay,我们需要先提取出电容和电阻,如果已经有真实的绕线(route)或者预估的绕线(global route),那么只需要根据route在不同层(layer)的分布就可以提取出相对准确的寄生参数值,下图是在log中显示每一层的layer的单位电阻和电容值的实例,这些值的源头是Foundary提供 TLUPlus /ITF文件(本文以ICC为例,其他EDA工具会有较大差异,具体在PnR教程中会讲解):

但是,问题来了,在综合(Synthesis)阶段,如果没有绕线的长度信息,也没有stdcell的位置信息,是怎么得到电阻电容值的呢?这就是Wire Load Model在起作用了。

Wire Load Model

下图是标准单元库.lib中定义的一种Wire Load Model,名字是“ZeroWireload”,它是根据net的扇出(fanout)来预估长度(length),然后再根据所定义的单位长度的电阻(0.00001),以及单位长度电容(1)来计算net的寄生RC参数。不过图中的例子比较理想化,都是设成了0,完全不考虑net delay。在实际项目中,必要时,可以自己定义Wire Load Model,尽量在综合阶段将Net Delay的影响考虑进去。

Elmore Delay 模型

既然已经有了寄生的RC信息,那怎么计算Net Delay呢?

对于单输入单输出的net,假设不考虑net之间的耦合电容(即不考虑噪声的影响),并且也不存在电阻性的反馈回路的情况,可以用Elmore Delay模型来计算Net Delay,如下图:

根据Elmore Delay公式,各节点的delay可以表示为:

如果把绕线用分布式RC模型来表示,如下图:

那么,Net Delay可以进一步化简为:

原因是Cwire只能往前看到Rwire/2的电阻,Cload往前能看到Rwire的电阻。

AWE模型和Arnoldi模型

AWE(Asymptotic Waveform Evaluation)和Arnoldi都是是更高级的对RLC网络延时进行瞬态响应匹配近似的方法。当然,AWE本身也有一阶模型,结果与Elmore类似,但是误差也较大(与SPICE模型相比),可能达到74%,二阶AWE模型的误差可以减少到22%,四阶AWE的近似结果和SPICE模型的结果误差已经很小了。AWE模型的优点是容易实现,缺点是数值不稳定,而Arnoldi模型会更加稳健,在目前EDA工具Postroute阶段应用比较多。

Net Delay的优化

前面讲到Net Delay占整个Path的比重很大一部分已经超过20%了,如何去优化这一部分Net Delay呢?

根据Net Delay的计算公式,减少R*C的值就能优化Net Delay。由于高层金属通常会比底层金属的单位长度RC更小,所以把路径上的net更多地绕在高层金属上,可以把关键路径优化得更好。具体到PnR工具的实现上,通常会有一个“Layer Promotion”的功能。

另外,对于高速的net,尤其是clock net,一般会特殊对待,给它们设置NDR(Non-Default-Rule),让它们用更大的宽度(width)和间距(space),甚至加上shielding隔离它们,以保证这些高速的net不会被其它的net影响。当然设置NDR是有代价的,它们会占用更多的绕线资源,并不是越严格越好,常见的设置是,对clock net设置2倍宽度2倍间距(2w2s)的NDR。其实高速的net用更宽的rule还有一个DFM的原因,就是这些net的电子迁移(Electro-Migration,EM)导致的绕线缺陷机率比普通net要高。在PnR教程中会详细介绍EM,以及如何避免、修复EM的违例的问题。

总结

对于Net Delay,需要了解它在整个Path Delay占的份量,熟悉Wire Load Model,Elmore Delay,AWE,Arnoldi等概念。有些在后端的面试中也经常被问到。

-

这个是什么情况呢2015-09-11 2308

-

请问如何使用sigmastudio的delay延时??2018-08-10 3398

-

STM32在中断里使用SysTick_delay延时引起了哪些问题呢2021-11-16 2836

-

通用串行总线控制器出现叹号是什么情况?怎么解决?2017-11-13 66573

-

Atmel MCU 延时delay快速上手指南详解2018-06-18 6202

-

volte语音通话有什么用,什么情况下可以开/关volte2019-10-21 18700

-

【STM32单片机-库函数】SysTick延时—delay2021-11-24 1012

-

MSP432(Keil5)——3.delay延时驱动2021-12-14 928

-

STM32上进行Delay延时的方法2021-12-24 934

-

什么情况下芯片容易坏呢2022-01-02 8202

-

C语言 | 延时函数(Delay)2022-01-13 2339

-

Systick定时器延时原理与HAL_Delay()延时函数的使用2022-04-26 18243

-

在HAL库中用定时器实现自定义延时函数delay_us()2022-09-21 13841

-

什么情况下选用工业主板2023-02-14 1556

-

IGBT模块损坏时,什么情况导致短路?什么情况导致开路?2023-10-19 7099

全部0条评论

快来发表一下你的评论吧 !