讲讲Latch的功能?Timing Path如何分析?

电子说

描述

Latch功能

Latch的电路结构如下图:

Latch电路结构

当 E = 1 时,latch直传(transparent),D端信号的变化会即时反应在Q端;

当 E = 0 时,latch关断(closed),Q端保持关断瞬间D端的值。

设计中使用Latch的好处是,相比寄存器的面积更小,功耗更低,可以从后级电路进行time borrowing,更容易满足setup time,然而坏处是STA分析不会那么直接,下面我们就看看引入了Latch的Timing Path如何分析。

Time Borrowing

在数字设计中,经常会碰到如下图所示的Path,两个寄存器(UFF0和UFF1)之间存在一个锁存器(ULAT1),这种情况工具会怎么分析path呢?不同STA工具的行为会有稍微的区别,我们先以PT传统的分析方法来解释。

加入Latch后的电路图

Time Borrowing示意图

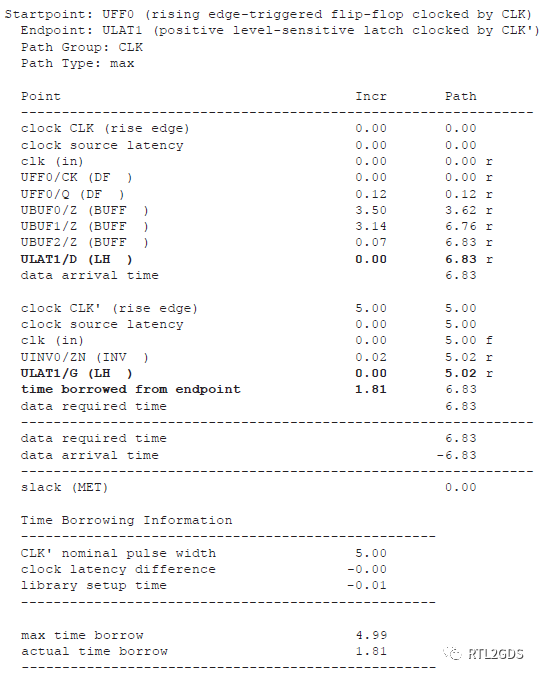

根据Latch的特点,在CLKN为高电平时,ULAT1是transparent,ULAT1/D端的数据能即时地反映在ULAT1/Q端。上图中的情况是,UFF0->ULAT1/D的Path Delay使得ULAT1/D数据在CLKN的上升沿之后才到达,需要从后一级ULAT1->UFF1中借了1.81ns,使得原本违例的path满足了要求,而ULAT1->UFF1的timing path即使借出去1.81ns,也能够满足要求,具体的timing report如下:

UFF0->ULAT1的Timing Path

ULAT1->UFF1的Timing Path

这里需要指出的一点是,在计算setup timing的时候,在UFF0->ULAT1中,ULAT1的clock path是按照early/min模式计算的,而在ULAT1->UFF1中,ULAT1的clock path是按照late/max模式计算的,有一部分公共路径的CRPR是不会被排除掉的,所以现在的PT引入了一种新的latch timing分析的模式,它把latch当成一个组合逻辑,在分析UFF0->UFF1的path时可以穿过ULAT1,这里只提示一下可以通过下面这个选型来打开,从而可以减少悲观度:

set_app_var timing_enable_through_paths true

这种模式下,Latch的D Pin只能作为Endpoint,不能作为Startpoint,所以在report_timing的时候也要注意是用-to还是-through的区别:

report_timing -to $latch_d_pin

report_timing -through $latch_d_pin

需要注意的是,这种through模式只是针对setup,对hold分析还是保持不变。下面接着看一个用latch来解决跨时钟域hold timing问题的应用。

Lockup Latch in Scan Chain

为了芯片测试的需要,我们会用Scan Chain的方式将绝大部分的寄存器串链起来,在不影响功能的情况下,以简单的方式测试电路中寄存器的良率。但是存在一种情况,前后相邻的两级寄存器如果时钟不一样(跨时钟域),如下图所示:

加入Lockup latch之前的电路图

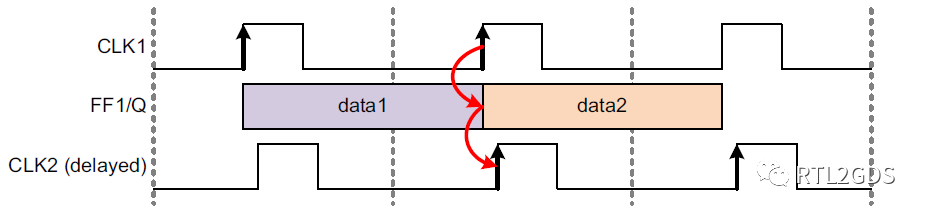

由于CLK1和CLK2为不同的时钟域,很难保证他们同步,假如CLK2相比CLK1有一段不确定的延迟Tskew,可大可小,那么很有可能FF1/CLK1->FF1/Q->FF2/SI这段延时Tdata会比Tskew小,造成hold timing违例。

加入Lockup latch之前的hold timing时序图

上一节提到Latch有time borrowing的功效,假如在两级寄存器之间加入一个latch,结构如下图所示:

加入Lockup latch之后的电路图

CLK1低电平的时候,Lockup Latch是transparent,CLK1高电平的时候Lockup Latch一直保持上一拍的数据,这样即使CLK2有延迟,只要不超过CLK1高电平持续时间,就能保证hold timing没有问题。

加入Lockup latch之后的hold timing时序图

在DC中可以很方便的实现这一功能,具体会在RTL2GDS微信公众号的综合/DFT教程中详细介绍。

Clock Gating Check

Latch的另一个应用是作为门控时钟单元(Clock Gating Cell),通过避免部分寄存器不必要的时钟翻转,可以极大地节省电路的动态功耗。实际应用中,为了避免出现毛刺,会在Latch后面添加一个与门组成一个ICG(Integrated Clock Gating)。

ICG电路结构

由于ICG是用在clock path上,STA工具默认会要求做CLKI到EN端的clock gating check,目的是保证时钟使能的时序满足要求,所以会存在REG2ICG的path。因为ICG的clock会比REG的clock delay要短,所以天然存在一个skew对setup不利,特别是假如有多级的ICG级联,更加加重了这种情况。在设计上,需要保证REG2ICG的数据路径不能太复杂,否则物理实现会存在困难。

在CTS之前,由于clock tree是ideal的,考虑不到这种skew的不利影响,所以往往需要通过SDC命令"set_clock_gating_check"人为地设置,让综合或者布局工具提前认识到这一点并提前优化。

需要注意的是,不仅仅ICG需要clock gating check,如果clock path上存在与门、或门等逻辑也需要进行clock gating check。

-

ncp1234的latch脚怎么用2023-12-07 1599

-

时序分析基本概念介绍<Critical Path>2023-07-07 2475

-

时序分析基本概念介绍—Timing Arc2023-07-06 5951

-

什么是时序路径timing path呢?2023-07-05 3412

-

介绍的时序分析基本概念PBA分析模式2023-07-03 5019

-

Verilog基本功--flipflop和latch以及register的区别2019-08-27 5349

-

静态时序分析基础与应用2018-04-03 794

-

详细介绍时序基本概念Timing arc2018-01-02 26091

-

基于FALSE PATH的设置2017-09-19 624

-

Latch UP2011-12-16 3456

-

逻辑分析仪中Timing-State存储方式的应用2011-09-22 720

-

Timing Groups and OFFSET Const2010-01-11 708

全部0条评论

快来发表一下你的评论吧 !