总结一下pipeline流水线设计的关键点

EDA/IC设计

描述

pipeline流水线设计是一种典型的面积换性能的设计。一方面通过对长功能路径的合理划分,在同一时间内同时并行多个该功能请求,大大提高了某个功能的吞吐率;另一方面由于长功能路径被切割成短路径,可以达到更高的工作频率,如果不需要提高工作频率,多出来的提频空间可以用于降压降功耗,进可攻退可守。

1

流水线的时间并行

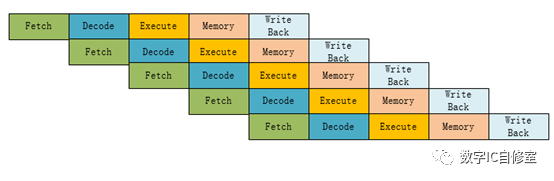

流水线设计是完美的时间并行。因为流水线上每一级的处理都是一个时钟周期的延时,并且一动则全动,每一级的延时可以完美的掩盖起来,最高实现与流水级数相同数量的请求并行度。

如上图所示,在现代经典的cpu处理中,流水线级数被广泛应用,cpu的各个处理环节可以看作流水线上的一个stage。在单发射单处理单元的最简单处理器中,同一时间内最高同时可以支持5条指令的执行。如果没有指令冲突,资源冲突等可能导致断流的场景,基本可以认为每一个时钟周期都可以完成一条指令的处理。

当然,除了CPU,只要是一个周期无法完成的功能,在性能优先的设计中,为了提高吞吐率,都可以采用流水线技术来对功能路径进行切分,比如乘法器等。

2

流水线的stage划分

我们知道,流水线的分割线是一组寄存器,这条分割线放在哪个位置完全由设计者决定。一般来说,划分流水线的时候主要有以下三点考虑:

- 如果流水线切割的子功能抽象层次较高,最好按完整的功能来进行流水线划分,比如CPU的各个执行环节。

- 流水线最好划分在数据通路上位宽较小的地方,以节省寄存器数量和面积。在流水线上可以有许多的数据路径,数据路径会有中间结果和最终结果。那么这个时候就可以选择性地进行切割。比如一个1024bit 2选1的数据选择器,如果将流水线划分划在选择器的输入端,那么将占用2x1024=2048bit的寄存器以及1个1bit的选择信号。而如果将流水线划分在选择器的输出端,那么只需要1024bit的寄存器,显然面积的收益十分巨大。

- 流水线每一级的关键路径延时最好接近,这样利于获得最大的timing margin,频率可以跑到最高。这点很好理解,假设一条关键路径在切割流水线之前延时为a,时钟周期近似为a,将其切割成2级流水线。假设切割之后的新关键路径仍然在该关键路径上,那么新的时钟周期将取决于切割后的关键路径延时。很明显,a/2是最小的,如果不是均分,那么总有一级大于a/2,那么时钟周期将大于a/2。当然,也有可能切割流水线之前的关键路径被切割之后不再是关键路径。假设一条非关键路径b,在切割之后变成1/3b和2/3b。并且2/3b >1/2a,那么2/3b将会成为新的关键路径,新的时钟周期将接近2/3b。这种情况下,如果对于路径b的这种切割不是必要的(比如出于功能完整性和面积考虑),那么完全可以将b切成1/2b和1/2b,1/2b<1/2a<2/3b,时钟频率依然可以以1/2a为准。

3

流水线设计的简单例子

那么怎么设计一个流水线呢?其实从结构上来讲,流水线很简单,无非是一个原本完整的功能,中间插了几级寄存器,每级寄存器的输出做不一样的功能,每一拍都进行一次更新,把上一级的结果打到下一级。比如一个最简单的例子,假设一个周期只能完成一个1bit加法,那么要实现3个操作数加法s=a+b+c,并且保证每个周期都有一个结果寄存器输出,可以使用3级流水实现:

上面这个例子可以保证如果每一拍都有新的a_in, b_in, c_in输入,那么在经过了2拍的延时后每一拍都可以输出一个s_out。

但是实际场景中流水线的最终结果输出并不一定是每一拍都需要的。假设s_out的下游有反压信号,如果流水线还是每拍都流水,那么s_out的结果将会每拍都刷新一次,在下游存在反压的情况下会有有效数据被流水冲刷掉,那么将会导致结果的错误。因此对于这种下游有反压的场景,不能简单地每拍都进行一次流水。而要考虑进下游的反压。

在上面的例子中,假设下游的反压信号是rdy_in,因为流水线反压一级则前级均被反压,因此每一级都需要一个反压信号,而流水线最后一级的反压信号将参与到前面每一级流水的反压信号生成中。代码中控制逻辑增加反压:

4

流水线的逐级反压串扰

从上面的例子可以看到,最后一级的流水输出vld_out需要与下游的反压信号rdy_in完成握手之后,上一级s2才可以更新到out。只有s2更新到out,s1才能更新到s2。只有s1更新到s2,in才能更新到s1,这样一来,我们注意到ena_s1,也就是第一级流水的更新使能信号,其实可以拆解到rdy_in这个最后一级的反压信号。由此可见rdy_in串扰到了最前面一级,形成了逐级反压串扰。这只是一种最简单的场景,如果rdy_in信号的生成逻辑较复杂,并且流水线级数较多,每一级的rdy信号除了下一级的握手成功,还有别的条件,比如资源冲突,数据冲突等,那么这条从最后一级反压信号开始的组合逻辑路径将会很长,成为流水线中的关键路径,必要时需要一些特殊的手段进行处理。

解决这个问题的办法就是切割这种逐级握手机制。有以下2种做法,这里就不一一展开:

使用旁路缓存。这种方法比较常见。即在流水线的某一级加入一个buffer,该级的rdy信号直接使用buffer的非满信号,这样就能切割该级与后面流水线的握手联系,通过buffer非满信号来决定是否可以流水到这一级。当流水流到这一级之后,再根据下游是否握手成功决定是要写入旁路缓存还是直接bypass缓存。

5

流水线的其他反压场景

除了来自最后一级流水的逐级反压,每一级流水都有可能单独被反压的可能。这取决于具体的设计。比如经典流水线CPU设计中的RAW, WAW问题,运算单元资源冲突问题,总线带宽资源限制问题等等。而无论是哪一级被反压,都要逐级反压前面的流水。

-

流水线基本结构2025-11-21 215

-

FPGA中的流水线设计2020-10-26 3265

-

ARM流水线有什么作用2021-07-16 2184

-

什么是流水线技术2010-02-04 4408

-

流水线ADC的行为级仿真2012-04-05 1016

-

电镀流水线的PLC控制2016-02-17 1324

-

Verilog基本功之:流水线设计Pipeline Design2018-09-25 7815

-

FPGA之为什么要进行流水线的设计2019-11-28 4416

-

各种流水线特点及常见流水线设计方式2021-07-05 10097

-

滚筒输流水线故障排除方法2021-07-08 2372

-

如何选择合适的LED生产流水线输送方式2021-08-06 1488

-

嵌入式_流水线2021-10-20 1268

-

CPU流水线的问题2022-09-22 3159

-

什么是流水线 Jenkins的流水线详解2023-05-17 1781

-

行云流水线 满足你对工作流编排的一切幻想~skr2024-08-05 1048

全部0条评论

快来发表一下你的评论吧 !