低功耗设计基础:Clock Gating

电子说

描述

大多数低功耗设计手法在严格意义上说并不是由后端控制的,Clock Gating也不例外。在一颗芯片中,绝大多数的Clock Gating都是前端设计者或者EDA综合工具自动加上去的,后端只有在极端例外的情况下才会动到它们。

尽管如此,Clock Gating的影响与后端息息相关,甚至会引起后端的一些问题,因此我们有必要从头理解一下它的原理。

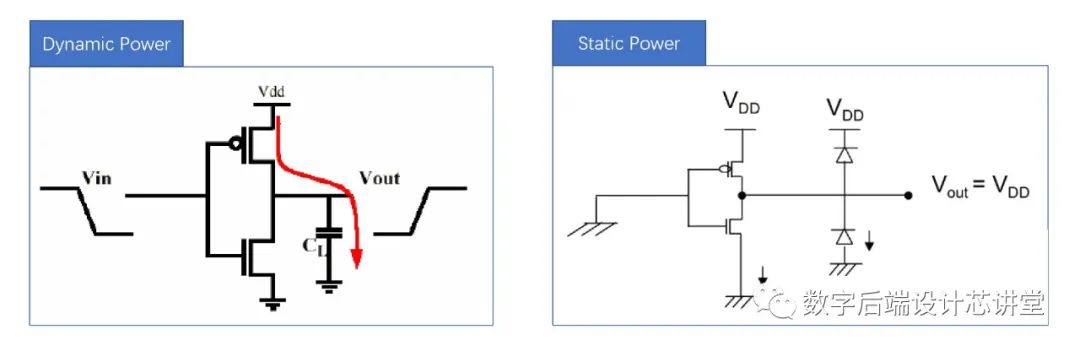

芯片功耗从原理上区分主要有两大类:静态功耗(Static Power)和动态功耗(Dynamic Power)。二者的形成原因如下:

所谓动态功耗,主要是由于信号的翻转从而导致器件内部的寄生RC充放电引起的,而静态功耗则是由器件在通电状态下的泄漏电流(Leakage Current)引起的。对此,为了节约动态功耗,最初有个十分简单的想法:在芯片实际工作过程中,有些信号或者功能并不需要一直处于活动状态,那么就可以在它们不用的时候将其时钟信号关闭。这样一来时钟信号不再翻转,从而能够有效减少动态功耗,而控制时钟信号开关的就是Clock Gating。

那么Clock Gating是如何被加入到design中的呢?它主要有两种来源:设计者从RTL阶段加入或者由综合工具自动加入。

下面的例子介绍了在RTL阶段加入Clock Gating的方法:

可以看到在加入Clock Gating之后,DFF的clock信号前多了一个使能端EN,从而可以控制该时钟信号的打开与关闭。

除此之外,在综合阶段,EDA工具同样支持自动插入Clock Gating。以Synopsys公司的Design Compiler工具为例,简单的插入Clock Gating的方法如下:

Clock Gating在后端会引起一些问题,尤其在Setup Timing以及时钟树综合阶段,有时候会需要做一些特殊的处理。关于为何Clock Gating容易引起setup timing 的问题,请参考历史文章:

为了尽量避免ICG的setup timing,解决办法之一是将ICG放在距离register(sink)尽量近的地方:

当然,EDA工具也提供了一些优化方法以便在早期发现和解决ICG的问题,这些技巧希望大家在实践中多多尝试和挖掘。

编辑根据作者在DC中做了一下实验,带ICG的DFF如下所示:

ICG的结构如下所示:

需要注意的是,只有当寄存器的位宽达到一定大小时,DC才会自动将其使能端综合为ICG单元(经过测试,3个及3个以上的位宽会综合为ICG单元)。

事实上,由于ICG单元本身带来了 面积占用 ,只有当寄存器位宽达到一定的大小时,使用ICG才能达到即降低面积又降低功耗的效果,这是在我们今后的使用中需要注意的地方。

-

门控时钟(Clock-gating)介绍2026-01-16 99

-

SOC设计中Clock Gating的基本原理与应用讲解2024-04-28 4372

-

什么是Clock Gating技术?Clock Gating在SoC设计中的重要性2023-10-07 5032

-

浅析clock gating模块电路结构2023-09-11 4239

-

clock-gating的综合实现2023-09-04 3473

-

ASIC的clock gating在FPGA里面实现是什么结果呢?2023-08-25 1610

-

Clock Gating的特点、原理和初步实现2023-07-17 6930

-

RTL实例化的clock gating cell浅见2023-07-14 3618

-

AND GATE的clock gating check简析2023-06-29 5434

-

一文搞懂BL开发板系列MCU低功耗性能2022-07-07 5581

-

主要演示BL702/704/706系列mcu低功耗性能2022-06-28 9200

-

什么是门控时钟 门控时钟降低功耗的原理2021-09-23 15868

-

降低电路漏电功耗的低功耗设计方法2020-09-16 13206

全部0条评论

快来发表一下你的评论吧 !