DDS与PLL的区别解析

电子说

描述

频率的产生有两种方法:DDS和PLL,但是为什么射频工程师一般用PLL多,很少用DDS呢?

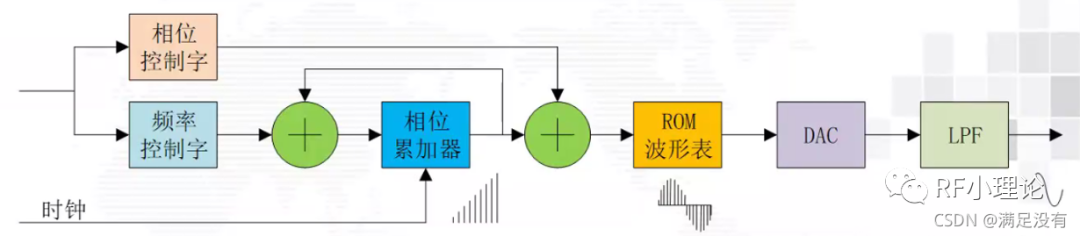

DDS:直接数字式频率合成器DDS(Direct Digital Synthesizer)。

实际上是一种分频器:通过编程频率控制字来分频系统时钟(SYSTEM CLOCK)以产生所需要的频率。

DDS 有两个突出的特点一方面,DDS工作在数字域,一旦更新频率控制字,输出的频率就相应改变,其跳频速率高,另一方面,由于频率控制字的宽度宽(48bit 或者更高),频率分辨率高。

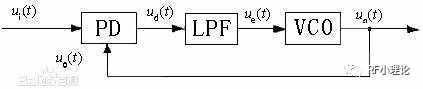

PLL(Phase Locked Loop):为锁相回路或锁相环,用来统一整合时钟信号,使高频器件正常工作,如内存的存取资料等。PLL用于振荡器中的反馈技术。

许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步。一般的晶振由于工艺与成本原因,做不到很高的频率,而在需要高频应用时,由相应的器件VCO,实现转成高频,但并不稳定,故利用锁相环路就可以实现稳定且高频的时钟信号。

从两个频率合成器的介绍中我们可以得出:

1.DDS输出频率上限取决于参考时钟,并且由于ADC变换的原因最多只能达到参考的一半。

PLL输出频率的上限取决于VCO的上限。

2.DDS频率切换在数字域实现,时间非常快,可以达到ns级;

PLL锁定时间取决的硬件时间,时间为us级;

3.DDS的实现不要额外的模拟器件,所以功耗低。

锁相环由于频率的实现全部在模拟器件实现,相对而言功耗较高。

上面讲了DDS的优点,下面讲一下DDS的缺点,为什么射频工程师很少用的原因。

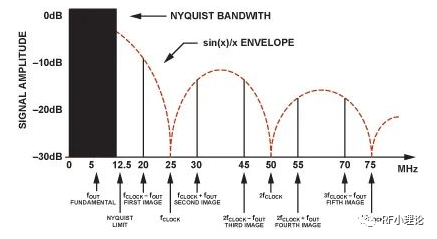

DDS的输出是DAC输出,DAC我们都知道,输出的并不是连续的正玄波,而是带有正弦时间包络的一系列脉冲。对应的频谱是一系列图像和混叠信号。图像沿sin(x)/x 包络分布。有必要进行滤波,以抑制目标频带之外的频率,但是不能抑制通带中出现的高阶混叠

因此,DDS的输出相位噪声存在较多的小数杂散,并且很难滤除。对于设计高要求的接收机与发射机,杂散的控制是一个很严的指标,基于杂散的可控制性,DDS对射频工程师来说并不是一个很好的选择。

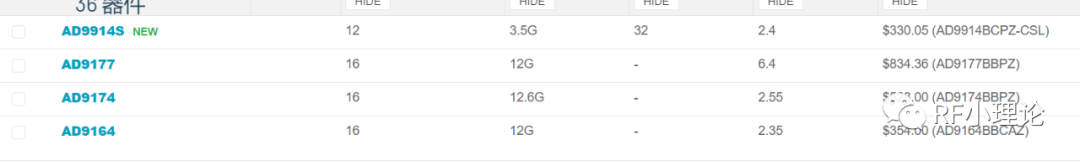

同时由于DDS的输出频率最多只到达DAC的一半,目前DAC速率最高也就在12G左右,射频输出频率最高不到6G,对于很多设计来说这个频率上限可能不满足设计。同样的频率相对功耗而言,虽然没有很多的模拟器件,但是为了满足高速采样,DDS的接口功耗非常高。

综上所述,在跳频速率满足的情况下,基于杂散,整体功耗等考虑,PLL指标与性能更能满足射频工程师的需求。

审核编辑:刘清

-

直接数字频率合成技术(DDS+PLL)2021-06-07 1171

-

改进型DDS驱动PLL的原理及测试结果2020-12-03 2294

-

DDS还是PLL?2019-02-13 3259

-

PLL相比于DDS所拥有的典型优势分享2018-10-31 2866

-

DDS与PLL的细微差别2018-10-11 1972

-

关于DDS+PLL雷达发射源芯片选型问题请教2018-10-09 1388

-

DDS芯片选型,请问DDS专用芯片与基于FPGA的DDS的区别是什么?2018-08-06 8460

-

基于DDS驱动PLL结构的宽带频率合成器的设计与实现2017-10-27 1270

-

DDS-PLL组合跳频频率合成器2016-07-20 1152

-

基于DDS+PLL在电台设计中的应用2011-07-18 8879

-

以DDS为参考的PLL在电台设计中的应用2011-07-16 2975

-

基于FPGA 的新的DDS+PLL时钟发生器2009-12-14 565

-

DDS PLL短波频率合成器设计2009-09-07 647

全部0条评论

快来发表一下你的评论吧 !