详解静态时序分析的方法和流程

电子说

描述

1涉及的数字电路基础知识

1.1模拟信号与数字信号,高电平与低电平

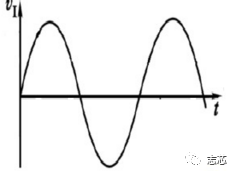

模拟信号:在时间和幅值上是连续变化的电信号。

图1

数字信号:在时间和幅值上是离散的电信号。

图2

数字电路的基本工作信号是二进制的数字信号,而二进制数只有“0”和“1”两个基本数字,对应在电路上只需要两种不同的工作状态,即高电平和低电平。0和1表示两种对立的工作状态,并不表示数量的大小在数字电路中,通常用电位的高低去控制门电路,规定用1表示高电平,用0表示低电平,为正逻辑,若用0表示高电平,用1表示低电平,为负逻辑。

1.2数字电路的表示方法

1.2.1逻辑函数表达式

用逻辑函数表示输入信号与输出信号的关系。逻辑表达式中的运算一般为布尔运算,与普通代数不同,布尔代数中的变量是二元值的逻辑变量。

图3

1.2.2真值表

用表格表示门电路输入信号与输出信号对应的逻辑关系。

图4

1.2.3逻辑电路图

图5

1.2.4波形图

以波的形式表示门电路输入与输出的逻辑关系。

图6

其他表达方法还有:卡诺图法(一种几何图形,可以用来表示和简化逻辑函数表达式);点阵图法(是早期可编程逻辑器件中直观描述逻辑函数的一种方法);硬件设计语言法(是采用计算机高级语言来描述逻辑函数并进行逻辑设计的一种方法,它应用于可编程逻辑器件中,目前采用最广泛的硬件设计语言有HDL、VHHDL等)。

1.3数字电路中的逻辑关系

数字电路中往往用输入信号表示“条件”,用输出信号表示“结果”,条件与结果之间的因果关系称为逻辑关系。基本的逻辑关系:与逻辑、或逻辑、非逻辑。能实现某种逻辑关系的电路称为逻辑门电路。基本逻辑门电路:与门、或门、非门。

1.3.1与门电路

与逻辑关系:只有决定某事件的全部条件同时具备时,该事件才发生,逻辑与,或称逻辑乘。表达式:Y=A·B或Y=AB。逻辑功能:有 0 出 0 ,全 1 出 1 。说明与门定义的电路(图7)、逻辑符号(图8)、真值表(图9)。

图7

图8

图9

1.3.2或门电路

或逻辑关系:决定某事件的几个条件中,至少有一个条件具备,该事件都会发生,或称逻辑加。表达式:Y=A+B。逻辑功能:有 1 出 1,全 0 出 0 。说明或门定义的电路(图10)、逻辑符号(图11)、真值表(图12)。

图10

图11

图12

1.3.3非门电路

非逻辑关系:当条件具备时,该事件不发生;而当条件不具备时,该事件反而发生,条件和结果总是呈相反状态。称为逻辑非,也称为逻辑反。表达式: 。逻辑功能:入 0 出 1 ,入 1 出 0 。说明非门定义的电路(图13)、逻辑符号(图14)、真值表(图15)。

图13

图14

图15

1.4脉冲波形和脉冲波形的一些特性参数

获得脉冲的方法:(1)自激振荡电路直接产生矩形脉冲。由多谐振荡器来实现。(2)将已有波形(正弦波、锯齿波等)整形为矩形脉冲。由施密特触发器和单稳态触发器来实现555 定时器是构成多谐振荡器、施密特触发器和单稳态触发器的既经济又简单实用的器件。

图16

矩形脉冲的一些特性参数:

脉冲周期T:周期性重复的脉冲序列中,两个相邻脉冲之间的时间间隔。有时也使用频率(f=1/T)表示单位时间内脉冲重复的次数。

脉冲幅度Vm :脉冲电压的最大变化幅度。

脉冲宽度tW:从脉冲前沿到达0.5Vm起,到脉冲后沿到达0.5Vm为止的一段时间。

上升时间tr:脉冲上升沿从0.1Vm上升到0.9Vm所需要的时间。

下降时间tf:脉冲下降时间从0.9Vm下降到0.1Vm所需要的时间。

占空比q:脉冲宽度与脉冲周期的比值,亦即q=tW/T。

此外,在将脉冲波形或者产生电路用于具体的数字系统时,有时还可能有一些特殊的要求,例如脉冲周期和幅度的稳定性等。这时还需要增加一些相应的性能参数来说明。

1.5半导体存储电路基础

各种门电路虽然都有两种不同的输出状态(高、低电平,亦即1、0),但是都不能自行保持。在各种复杂的数字电路中不但需要对二值信号进行数值运算和逻辑运算,还经常需要将运算结果保存下来。为此,需要使用具有记忆功能的基本逻辑单元。能够存储1位二值信号的基本单元电路统称为触发器。

锁存器和触发器:锁存器---不需要触发信号,由输入信号直接完成置0或置1操作。

触发器---需要一个触发信号(称为时钟信号clock),只有触发信号有效时,才按输入信号完成置0或置1操作。锁存器是静态电路,触发器是动态电路。

触发器具有如下特点:有两个稳定状态(简称稳态),用来表示逻辑 0 和 1。在输入信号作用下,触发器的两个稳定状态可相互转换(称为状态的翻转)。 输入信号消失后,新状态可长期保持下来,具有记忆功能。

触发器的分类如下。按触发方式分:电平触发、脉冲触发、边沿触发。按逻辑功能分:SR 触发器、D 触发器、JK 触发器、T 触发器。

下文大致介绍一下SR锁存器和SR触发器,其它有兴趣的内容可以自行去学习。

1.5.1SR锁存器

SR锁存器(两个Set-Reset Latch)是静态存储中当中最基本、也是电路结构最简单的一种。通常它由两个或非门或者与非门组成。下文以或非门组成的锁存器为例说明。

图17为SR锁存器电路结构。

图17

Q和Q′为互补输出端,正常工作时,它们的输出状态相反(规定,两个端口的输入状态一定相反)。通常用Q的状态表示触发器的状态,即: Q = 0,Q′ = 1时,称为触发器的“0”态;Q = 1,Q′ = 0时,称为触发器的“1”态。SR锁存器输出特性表如图18所示,图19是其逻辑符号。

图18

图19

1.5.2电平触发的SR触发器

在数字系统中,为协调各部分的动作,常常要求某些触发器在同一时刻动作(即改变状态,也称为翻转),这就要求有一个同步信号来控制,这个控制信号叫做时钟信号(Clock),简称时钟,用CLK表示。具有时钟脉冲控制的触发器统称为时钟触发器,又称钟控触发器。 电平触发器(也称同步触发器)是其中最简单最常见的一种。

图20是SR触发器的电路结构和工作原理,图21是其功能表,图22是其逻辑符号。

图20

图21

图22

1.6组合逻辑和时序逻辑

组合逻辑的特点是任意时刻的输出仅仅取决于该时刻的输入,与电路原本的状态无关,逻辑中不牵涉跳变沿信号的处理。

时序逻辑是其特点为任意时刻的输出不仅取决于该时刻的输入,而且还和电路原来的状态有关。电路里面有存储元件用于记忆信息,从电路行为上讲,不管输入如何变化,仅当时钟的沿(上升沿或下降沿)到达时,才有可能使输出发生变化。

2时序分析基础概念

2.1 STA(静态时序分析)

简介:静态时序分析是检查IC系统时序是否满足要求的主要手段。以往时序的验证依赖于仿真,采用仿真的方法,覆盖率跟所施加的激励有关,有些时序违例会被忽略。此外,仿真方法效率非常的低,会大大延长产品的开发周期。静态时序分析工具很好地解决了这两个问题。它不需要激励向量,可以报出芯片中所有的时序违例,并且速度很快。STA在设计中的位置如下(不止一个环节哦)。

图23

作用:通过静态时序分析,可以检查设计中的关键路径分布;检查电路中的路径延时是否会导致setup违例;检查电路中是否由于时钟偏移过大导致hold违例;检查时钟树的偏移和延时等情况。此外静态时序分析工具还可以与信号完整性工具结合在一起分析串扰问题。

常用的静态时序工具是SYNOPSYS公司的PrimeTime。

图24

2.2 Timing Arc(时序弧)

简介:如果两个pin之间在timing上存在因果关系,我们就把这种时序关系称为Timing arc,主要分为定义时序延迟,和定义时序检查两种。为什么叫它时序弧?因为时序图中经常用一条弧形线段来表示它。

如图25所示,图中弧线部分都可以表示为时序弧。

图25

2.2.1时序延迟的Timing Arc

Combinational Timing Arc:最基本的TimingArc。TimingArc 如果不特别指明的话,就是属于此类。定义了从特定输入到特定输出(A到Z)的延迟时间。

Edge Timing Arc:定义时序组件ClockActive Edge 到数据输出的延迟时间,依据Clock上升或下降分为2类。

Edge Timing Arc:定义时序组件ClockActive Edge 到数据输出的延迟时间,依据Clock上升或下降分为2类。

Preset and Clear Timing Arc:定义时序组件清除信号(Preset或Clear发生后,数据被清除的速度,依据清除信号上升或下降及是Preset或Clear分为4类。这个TimingArc 通常会被取消掉,因为它会造成信号路径产生回路,这对STA而言是不允许的。

Three State Enable & Disable Timing Arc:定义 Tri-State 组件致能信号(Enable)到输出的延迟时间,依据Enable或Disable分为2类。

2.2.2时序检查的Timing Arc

Setup Timing Arc:定义时序组件(Sequential Cell,如Flip-Flop、Latch 等)所需的Setup Time。

Hold Timing Arc:定义时序组件所需的 Hold Time,依据Clock 上升或下降分为2类。

Recovery Timing Arc:定义时序组件ClockActive Edge 之前,清除信号不准启动的时间,依据Clock上升或下降分为2类。

Removal Timing Arc:定义序向组件ClockActive Edge 之后,清除信号不准启动的时间,依据Clock上升或下降分为2类。

Width Timing Arc:定义信号需维持稳定的最短时间,依据信号维持在0或1的位准分为2类。

2.3 Timing Path(时序路径)

由startponit和endpoint组成。Startpoint:设计中数据被时钟沿载入的那个时间点,包括时序单元的input pin、design的input port。Endpoint:数据通过了组合逻辑被另一个时钟沿载入的时间点,时序元件的数据输入pin、设计的output port。

Timing Path大致分为以下几类:IO2REG、REG2REG、REG2IO、IO2IO(“2”表示“to”)。IO2REG:开始于一个input port 且结束于时序元件的数据输入端。REG2REG:开始于时序元件的时钟pin且结束于时序元件的数据输入端。REG2IO:开始于时序元件的时钟pin且结束在一个output port。IO2IO:开始于input port 且结束于 output port。

2.4 Slack

余量,就是signal的arrive time和require time的差值(或require time和arrive time的差值);每一个path都有专属的slack,slack值可以是正,0或者负。

2.5margin

裕量,当时序要求满足,slack为正时,这个值就是margin。

2.6Critical Path

某一个path拥有最坏的slack的话则称之为 critical path,若是所有的path都没有时序违规,则slack都是正数,此时最小的那个slack则是critical path。

2.7group path

路径可以被分组(group)来得到各自的时序分析,时序报告和优化。

2.8发送时钟

两级寄存器中触发第一级寄存器的时钟。

2.9捕获时钟

两级寄存器中触发第二级寄存器的时钟。

2.10clock skew(时钟偏移)

同一时钟源到达不同的寄存器的延时不同。

2.11clock jitter(时钟抖动)

时钟频率和相位会不断变化,脉冲宽度会发生变化。

2.112clock latency(时钟延时)

简介:时钟从时钟源(比如说晶振)出发到达触发器时钟端口的延时,称为时钟的延时,包含时钟源延迟(source latency)和时钟网络的延迟(network latency)。

分类。clock source latency(时钟源延迟):也称为插入延迟(insertion delay),是时钟信号从其实际时钟原点到设计中时钟定义点(时钟的输入引脚)的传输时间。clock network latency(时钟网络的延迟):是时钟信号从其定义的点(端口或引脚)到寄存器时钟引脚的传输,经过缓冲器和连线产生的延迟(latency) 。

2.13transition(时钟转换时间)

时钟的上升沿跳变到下降沿或者时钟下降沿跳变到上升沿的时间。时钟的转换时间与与单元的延时时间(也就是器件特性)还有电容负载有关。

2.14 capacitance

负载电容。

2.15fanout

时钟扇出。

2.16driving cell

驱动单元。

2.17最快路径和最慢路径

简介。最快路径:指在信号传播延时计算中调用最快工艺参数的路径;根据信号的分类可以分为最快时钟路径和最快数据路径。最慢路径:指在信号传播延附计算中调用最慢工艺参数的路径;分为最慢时钟路径和最慢数据路径。

为什么存在最快和最慢路径:在一个库中,尽管电路器件单元已经被综合映射,但是工具可以通过改变周围的环境来得到不同的单元延时,所以即使是同一个库,调用工艺参数不一样的情况下,:其单元延时是不同的,因此就有了最快路径和最慢路径。

2.18uncertainty

uncertainty,简称时钟不确定性。主要用来定义Clock信号到时序器件的Clock端可能早到或晚到的时间,降低了时钟抖动jitter对有效时钟周期的影响。值得注意的是,在setup check中,clock uncertainty是代表着降低了时钟的有效周期;而在hold check中,clock uncertainty是代表着hold check所需要满足的额外margin。

2.19SDC(Synopsys design constraints)

简介:即时序分析的设计约束文件,对电路的时序,面积,功耗进行约束,它是设计的命脉,决定了芯片是否满足设计要求的规范。

分类。描述芯片的工作速度,即时钟的频率:create_clock,create_generated_clock等。描述芯片的边界约束:set_input_delay, set_output_delay等。描述芯片的一些设计违反rule(DRV):set_max_fanout,set_max_capacitance, set_max_transition等。描述设计中一些特殊的路径:set_false_path,set_multicycle_path等。描述设计中一些需要禁止的timing arc:set_disable_timing等。

3时序分析的常用概念

3.1 launch edge

时序分析起点,第一级寄存器数据变化的时钟边沿,也是静态时序分析的起点。

3.2 latch edge

时序分析终点,数据锁存的时钟边沿,也是静态时序分析的终点。

3.3Setup Time (Tsu)

简介:建立时间,是指在时钟沿到来之前数据从不稳定到稳定所需的时间,假设建立的时间不满足要求那么数据将不能在这个时钟上升沿被稳定的打入触发器。

图26

3.4 Hold Time (Th)

保持时间,是指数据稳定后保持的时间。假设保持时间不满足要求那么数据相同也不能被稳定的打入触发器。

图27

3.5 Clock-to-Output Delay(Tco)

数据输出延时,这个时间指的是当时钟有效沿变化后,数据从输入端到输出端的最小时间间隔。

3.6 Clock skew

时钟偏斜,是指一个时钟源到达两个不同寄存器时钟端的时间偏移。计算公式:Tskew = Tclk2 - Tclk1。

图28

3.7Data Arrival Time

输入数据在有效时钟沿后到达所须要的时间。主要分为三部分:时钟到达寄存器时间(Tclk1),寄存器输出延时(Tco)和传输数据延时(Tdata)。计算公式:Data Arrival Time = Launch edge + Tclk1 +Tco + Tdata。

图29

3.8Clock Arrival Time

时钟到达时间,时钟从latch边沿到达锁存寄存器时钟输入端所消耗的时间为时钟到达时间。计算公式:Clock Arrival Time = Lacth edge + Tclk2。

图30

3.9 Data Required Time(setup/hold)

简介:数据需求时间,在时钟锁存的建立时间和保持时间之间数据必须稳定,从源时钟起点达到这样的稳定状态须要的时间即为数据需求时间。(建立时间)数据需求时间:Data Required Time = Clock Arrival Time – Tsu。(保持时间)数据需求时间:Data Required Time = Clock Arrival Time + Th。

图31

3.10Setup Slack和Hold Slack

建立时间余量,当数据需求时间大于数据到达时间时,就说时间有余量,Slack是表示设计是否满足时序的一个称谓。计算公式:Setup slack = Data Required Time - Data Arrival Time。由公式可知。正的slack表示数据需求时间大于数据到达时间,满足时序(时序的余量)。负的slack表示数据需求时间小于数据到达时间,不满足时序(时序的欠缺量)。

图32

Hold slack可根据定义类比。

3.11时钟最小周期

简介。系统时钟能执行的最高频率。最小时钟的要求:(1)当数据需求时间大于数据到达时间时,时钟具有余量。(2)当数据需求时间小于数据到达时间时,不满足时序要求,寄存器经历亚稳态或者不能正确获得数据。(3)当数据需求时间等于数据到达时间时。这是最小时钟执行频率。刚好满足时序。

计算过程。满足要求:Data Required Time = Data Arrival Time(满足建立时间要求)。即:Tmin + Latch edge + Tclk2 - Tsu = Launch edge + Tclk1 + Tco + Tdata。得到:Tmin = Tco + Tdata + Tsu – Tskew。

4时序分析的三种模式

4.1单一模式

简介:在该模式下,工具只会在指定的一种工作条件下检查建立时间和保持时间,该工作条件可能是最好的、典型的、最坏的中的一种,但只能是单一的一种。

建立时间分析。特征:捕获时钟选择最快路径,发射时钟选择最慢路径,数据路径选择最慢路径。公式:发送时钟最慢路径延时+最慢数据路径延时≤捕获时钟最快路径延时+时钟周期-终止点时序单元建立时间。如图33所示。

图33

保持时间分析。捕获时钟选择最慢路径,发射时钟选择最快路径,数据路径选择最快路径。计算公式:发射时钟最快路径延时 + 最快数据路径延时≥捕获时钟最慢路径延时 + 终止点时序单元保持时间。

4.2最好最坏模式

对于最好-最坏分析模式,静态时序分析工具会同时在PVT环境中的最好的和最坏的工作环境下检查建立时间和保持时间。也就是说,使用这个方式的时候,至少需要读入两个库(环境),一个用来设置最好的工作环境(或者说延时最小),一个用来设置最坏的工作环境(或者说延时最大)。

建立时间分析。最好-最坏分析模式中建立时间的基本计算公式与单一分析模式下建立时间的基本计算公式一致,不同点在于计算建立时间所使用的工作环境不同,在计算建立时间过程中静态时序分析工具调用逻辑单元的最大(max)延时时序库,并用来检查时序路径最大延时是否满足触发器建立时间。如图34.

图34

保持时间分析。同样,最好-最坏路径分析模式中保持时间的基本计算公式与单一分析模式下保持时间的基本计算公式一致。不同点在于计算保持时间所使用的工作环境不同。在计算保持时间过程中,静态时序分析工具调用逻辑单元的最小(min)延时时序库,并用来检查时序路径最小延时是否满足触发器保持时间的约束。 即进行保持时间检查时,始发点触发器的发射时钟延时、终止点触发器捕获时钟延时和从始发点到终止点的数据路径延时都是基于最好工作条件下所计算的路径延延时。如图35.

图35

4.3OCV模式

OCV(on-chip variation)即片上误差,在芯片变化相关工作模式下,与最好-最坏分析模式一样,静态时序分析工具也会同时在PVT境中的最好的和最坏的工作环境下检查建立时间和保持时间,也就是要读入两个库。

建立时间分析。OCV分析模式中建立时间的基本计算公式与其他分析模式下建立时间的基本计算公式一致,不同点在于计算最快路径和最慢路径所使用的工作环境不同,在计算建立时闻过程中静态时序分析工具调用时序单元的最大延时时序库来计算最慢路径的延时,同时调用逻辑单元的最小延时时序库来计算最快路径的延时,只检查时序路径的延时是否满足触发器建立时间的约束。进行建立时间检查时。始发点触发器的发射时钟采用的是最坏条件下最慢时钟路径,终止点触发器的捕获时钟采用的是最好条件下最快时钟路径,而从始发点到终止点的数据路径的延时则是在最坏条件下最慢数据路径延时。如图36所示。

图36

保持时间分析。选用的路径延迟的好坏与建立时间分析相反。

4.4考虑时序减免的OCV模式

考虑时序减免(timing derate)的OCV模式。时序减免(timing derate)的作用是很据减免(derating)系数,静态时序分析工具会在时序路径的每级逻辑门、连线和端口上都加上或减去一个原来延时值乘以减免系数值的延时作为最终的延时结果。设置时序减免值的目的是使时序分析结果更加符合实际情况。使用这种方式需要设置derating系数,系数值需要通过实际工程经验总结出来。

4.5考虑时钟路径悲观移除的OCV模式

考虑时钟路径悲观移除(CPPR)的OCV模式。可以分为不考虑时序减免和考虑时序减免情况。

4.6 PT guide中关于三种模式的描述

建立时间分析如图37所示。保持时间如图38所示。

图37

图38

4.7其他分析模式

其他先进的分析模式如AOVC、SOCV、POCV等,后面有空再给大家介绍。

5时序分析步骤

5.1准备工作

5.1.1时钟的非理想性

时钟对于时序电路至关重要。在进行RTL设计时,可以认为时钟是理想的,但在静态时序分析的时候,必须考虑到实际的时钟情形。时钟模型的精度直接影响了静态时序分析的精度。时钟的非理想性包括:时钟偏移(clock skew)、时钟抖动(clock jitter)。实际情况中,振荡器、互连、电源、负载都会影响到时钟,导致时钟出现偏移、抖动。

5.1.2对实际的时钟进行建模

这些定义都是加在SDC中,先以图39来为例说明。

图39

考虑图中的电路,电路中时钟源位于芯片外部。我们将时钟定义在芯片端口上,从时钟源到达端口需要经过3ns左右的延时(板级走线的延时),从时钟端口到寄存器要经过1ns左右的延时(时钟树的延时),对时钟树的延时进行建模可以采取下面的办法。

先在端口上定义时钟:create_clock per8.0 [get_ports clk]。

设置从时钟源到时钟端口的板级延时:set_clock_latency source 3 clk。

设置时钟树本身的延时。在布局布线之前可以采取下面的方法:set_clock_latency 1 clk。在布局布线之后,可以得到时钟树延时的确定值,采用如下的命令:set_propagated_clock clk。

知道时钟不确定性(例如0.2)时建模,如图40,此时可以:set_clock_latency 2.8 source early [get_ports clk];set_clock_latency 3.2 source late [get_ports clk]。

图40

分频时钟的建模。以图41为例(此例为2分频时钟)。在设计中,往往存在分频时钟,如果进行静态时序分析时,直接援用create_clock来设置,则PT会将分频后的时钟看做是一个与源时钟毫无关系的时钟。这样在分析源时钟域与分频时钟域之间的信号时,可能会出现问题。正确设置分频时钟方法:create_generated_clock -name divide -source [get -pins U4/clk] -divide-by 2 [get -pins U4/Q]。

图41

5.2主要流程

数据读入:静态时序分析工具读入门级网表、时序约束等信息。

将电路分解为时序路径:即将电路转换为时序路径的集合。时序路径是一个点到点的数据通路,数据沿着时序路径进行传递。它的起点是输入端口或者寄存器的时钟,终点是输出端口或者一个寄存器的输入引脚,每个路径最多只能穿过一个寄存器。这样时序路径就可以划分为:输入端口到寄存器、寄存器到寄存器、寄存器到输出端口、输入端口到输出端口。如下图所示,分析其时序路径。

计算每个路径上面的延时:在一个路径上,可能包含这几类延时:连线延时(布局布线前后的延时计算方法不一样)、组合逻辑的单位延时(影响因子有输入信号的转换时间,该值也决定输入晶体管的翻转速度、负载、单元本身的固有延时、制程、电压、温度等)、寄存器从clk端到Q端的延时。一个路径上的延时是该路径上所有连线的延时与单位延时的综合。延时一般定义为从输入跳变的50%时刻到输出跳变的50%之间的时间。

检查路径时序约束是否满足:路径约束主要指的是建立时间约束和保持时间约束。在寄存器的综合库描述中对寄存器的D端定义了建立时间和保持时间的约束。所谓建立时间约束是指在采样时钟到达之前,数据应该稳定的时间;保持时间是指在时钟到达之后,数据应该保持的时间,这样才能保证寄存器正确地锁存数据。对于纯组合逻辑,时序分析主要检查最大延时约束和最小延时路径。这种情况比较简单。

5.3构建时序分析脚本的过程、常用命令和脚本实例

5.3.1构建脚本

图42

如图42所示。大致过程为:(1)读入设计的相关信息(链接库、网表,如果是PR之后的静态时序分析还需要读入寄生参数信息);(2)设置驱动及负载。(3)定义时钟;(4)设置建立时间和保持时间;(5)设置约束(max_load、max_trsition、max_capacitance、max_latency等);(6)分析时序(用report_timing 等检查时序,用report_constraint 检查是否有违例)。

5.3.2常用命令

图43

5.3.3脚本实例

图44

6总结

本文是一个全面的STA入门文章,STA涉及到的大部分概念都涉及到,当然比较浅显,但是构建了一个系统的认识。后面笔者有空会陆续介绍:RC网络、PVT、RC corner、delay的计算模型、OCV、AOCV、SOCV、POVC、PT软件使用等知识。

-

静态时序分析的相关概念2023-07-04 2309

-

静态时序分析的基本概念和方法2023-06-28 2661

-

FPGA静态时序分析详解2022-09-27 4315

-

时序分析的静态分析基础教程2021-01-14 1197

-

华为FPGA硬件的静态时序分析与逻辑设计2020-12-21 1669

-

静态时序的分析原理及详细过程2020-11-25 11580

-

正点原子FPGA静态时序分析与时序约束教程2020-11-11 2899

-

静态时序分析:如何编写有效地时序约束(一)2019-11-22 4281

-

静态时序分析基础及应用2016-05-09 921

-

静态时序分析在IC设计中的应用2011-12-20 1307

-

手机数字基带处理芯片中的静态时序分析2010-08-02 638

-

静态时序分析与逻辑(华为内部培训资料)2010-07-09 1066

全部0条评论

快来发表一下你的评论吧 !