Zynq高速串行CMOS接口的设计与实现

接口/总线/驱动

描述

现在CMOS传感器的分辨率越来越大,对应的,对数据传输接口的要求也越来越高。根据熊猫君有限的实现和调试经验,基本上遇到了:

①多通道HiSPi接口:主要是Aptina(现已经被安森美收购),常用的有1080P60的AR0331(3.1M),3664×2748P15的MT9J003,3984×2712P80(开窗输出最高可达1200fps)的AR1011等;

②多通道LVDS接口:主要有索尼系列、安森美的Python系列、国产如长光辰芯和德国viimagic系列等,至少熊猫君用过的IMX172/IMX122/IMX185/

IMX236、安森美Python全系列和VII9222等都是LVDS输出;

③MIPI接口:多用于手机,一些监控用的CMOS如Sony IMX185、OV14810等也带;

④CCIR656:一般低分辨率的会带CCIR656接口,也有一些厂家的高分摄像头也带,比如OV14810;

⑤并行接口:较早设计的CMOS许多都是直接并口输出,比如Aptina的MT9M031、MT9J003都带有并口输出;

熊猫君在这里想讨论的是前三种接口的实现,它们是业界应用最广泛而且对FPGA资源有着共性要求。

无论是HiSPi、LVDS还是MIPI,其核心思想就是要实现将高速串行信号恢复成并行数据。这将会用到XilinxFPGA IOB上的一个重要的资源——ISERDES。

实现串行信号的并行化,光有ISERDES还不行,还需要用到IOBANK上的延时模块IDELAYCTRL和IOB上的IODELAYE以及相关的相位训练算法。

1 Xilinx的IO资源

本节对用到的IO资源作简要的介绍。

1.1 IDELAYCTRL资源

在电压、温度等因素变化时,可能会影响到系统的时序,此时IDELAYCTRL模块就可以连续补偿时钟域内所有个体的delay taps (IDELAY/ODELAY)。如果使用了IOB上的IDELAY或ODELAY资源,那么就必须使用IDELAYCTRL资源。请注意,整个IO BANK里面只有一个IDELAYCTRL。

IDELAYCTRL很重要的一个输入项就是参考时钟REFCLK,补偿时钟域内所有模块的时序参考,这个时钟必须由BUFG或BUFH驱动。REFCLK必须保证在FIDELAYCTRL_REF+IDELAYCTRL_REF_PRECISION(MHz)ppm才能保证IDELAY/ODELAY的延时分辨率:

(TIDELAYRESOLUTION=1/(32x 2 x FREF))

1.2 IDELAYE2逻辑

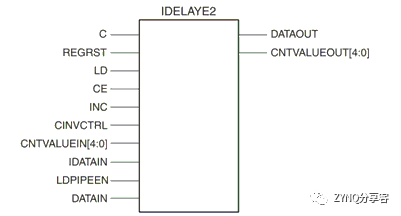

IDELAYE2逻辑是一个31抽头的循环延时补偿模块,对输入的信号进行指定分辨率的延时,FPGA可以直接访问。Tap延时分辨率由IDELAYCTRL的参考时钟提供持续补偿。图(1)是IDELAYE2接口示意图,表(1)是对这些接口的描述,表(2)是对逻辑参数的描述。

图(1 )IDELAYE2****接口示意图。

表(1 )IDELAYE2****接口描述

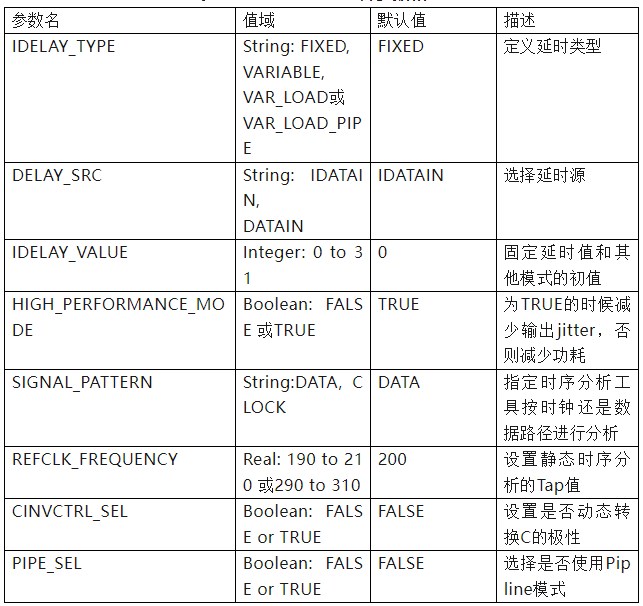

表(2 )IDELAYE2****逻辑参数描述

以下以VAR_LOAD模式为例说明延时的时序动作,如图(2)所示。

图(2 )延时时序动作模型

a)Clock Event 0:

在LD有效前,CNTVALUEOUT输出为未知值;

b)Clock Event 1:

在C的上升沿采样到LD有效,此时DATAOUT延时CNTVALUEIN指定的延时Taps,改变tap Setting到Tap2,CNTVALUEOUT更新到新的Tap值;

c)Clock Event 2:

INC和CE有效,此时指定了增量操作,Tap值加1,DATAOUT输出从Tap2更新到Tap3,CNTVALUEOUT更新到新的Tap值;

d)Clock Event 3

LD有效,DATAOUT输出延时更新到Tap10,CNTVALUEOUT更新到新的Tap值。

1.3 ISERDESE2逻辑

输入串转并逻辑可以看做是OSERDESE2的逆过程,在SDR模式下可支持2-、3-、4-、5-、6-和7-的串并转换,在DDR模式下可支持2-、4-、6-、8-的串并转换,级联DDR模式下还可扩展到10-和14-。每一个ISERDESE2包括:

a)专门的串并转换器;

b)Bitslip子模块用于源同步接口;

c)专用的可支持strobe-based的存储接口。

图(3)是ISERDESE2的结构示意图。表(3)是ISERDESE2接口描述,表(4)示ISERDESE2的参数描述。

图(3 )ISERDESE2****结构示意图

表(3 ) ISERDESE2

表(4)ISERDESE2的参数描述

(1) 时钟方案

CLK和CLK_DIV必须是严格对齐的时钟,虽然允许使用BUFIO/BUFR,但任然有可能存在相位问题。图(5)时采用BUFIO/BUFR的方案。

图(5 )采用BUFIO/BUFR****的时钟方案

一般的,根据接口类型的差异,时钟必须满足以下的约束:

①networking interface

a)CLK→BUFIO;CLKDIV→BUFR;

b)CLK→MMCM/PLL;CLKDIV→和CLK相同的MMCM/PLL的CLKOUT[0:6]的输出,使用MMCM时CLK和CLKDIV必须使用相同的驱动BUF;

c)CLK→BUFG;CLKDIV→BUFG。

②MEMORY Interface Type

a)CLK→BUFIO, OCLK→BUFIO,或CLKDIV→BUFR;

b)CLK→MMCM或PLL, OCLK→MMCM,或CLKDIV由同一个MMCM/PLL的CLKOUT[0:6]驱动;

c)CLK→BUFG,CLKDIV→不同的BUFG。

OCLK和CLKDIV的输入相位必须是严格对齐的,CLK和OCLK之间不要求相位关系。From CLK to OCLK的时钟域必须进行补偿。

其他接口类型的时钟方案参考文档UG471。

(2) BitSlip子模块

BitSlip用于调整并行寄存器输出串行数据的位置。在SDR模式下,每一个BitSlip脉冲让输出pattern的数据左移1bit;在DDR模式下,第一个BitSlip右移1bit,第二个BitSlip左移3bit,依次进行,移动规律如图(6)所示。BitSlip一定是和CLKDIV同步的一个脉冲。

图(6 )BitSlip****训练移位规律

在上面所介绍的资源中,IDELAYE2是动态相位对其训练的神器,ISERDESE2实现串并转换,其Bitslip功能是实现并行化数据对齐的关键。

2 LVDS高速接口实现实例

因为MIPI接口有其完整的物理层协议,因此不在这里讲具体实现,本文以Sony的IMX122 CMOS为例,聊一聊高速LVDS(HiSPi类似,只是电平标准有一点区别)接口在Xilinx 7系列FPGA和Zynq SoC上的实现。

2.1 需求分析

以Sony IMX122 CMOS为例,配置在1080P分辨率可输出30fps。CMOS在初始化完成后输出两通道稳定的LVDS数据,LVDS接收模块在收到配置完成信号后开始工作。因此,这个LVDS接收模块需要实现:

① CMOS工作在Slave模式下,向CMOS发出参考时钟(INCK)、行同步(XHS)、帧同步(XVS)信号;

② 接收LVDS数据并将它恢复成为指定的图像数据格式;

③ 提供测试信息接口。

2.2 IMX122 CMOS输出特性

本小节简介IMX122 CMOS的一些特性。

2.2.1 同步时序要求

在Slave模式下需要向CMOS提供周期稳定的XHS和XVS信号,两者的时序要求如图7所示。在产生同步时序时需要注意以下要点:

① XVS和XHS必须是稳定的周期性信号;

② XVS和XHS信号的低电平保持时间为4~100个INCK;

③ XHS可以和XVS同时拉低,也可延时一个时钟周期拉低。

图7Slave模式下同步时序

2.2.2 输出数据率

在串行SDR LVDS模式下以12bit模式输出,数据率为891Mbps,每个通道的数据率为445.5Mbps。

2.2.3 Sync Code格式

在串行输出模式下,CMOS通过输出固定的Sync Code来指示图像的有效帧、行信息,接收器需通过查找这些Sync Code来恢复图像。IMX122可提供两种模式的Sync Code,这里配置为SyncCode1,其具体定义如图8所示。

图8 IMX122 Sync Code定义

2.2.4 输出图像组织形式

IMX122在1080P读出模式下,输入参考时钟INCK是37.125MHz。一帧图像输出固定为1125行,每行1100 INCK(29.63μs),有效输出为1984×1105。图像输出的时序如图9所示,图10是输出数据编码规则。

图9 IMX122 LVDS模式输出时序

图10 IMX122 12-bit 2通道输出编码格式

2.3 设计思路和模块结构

Slave模式下工作的CMOS在XVS和XHS的同步下按照固定时序稳定输出LVDS图像数据。LVDS串行数据按照一定的方式进行编码,接收模块应先将串行数据解码恢复成为并行数据,再根据数据的排列方式格式化输出。因此,整个模块可以划分为时序同步、LVDS接收解码(串转并)和数据格式化输出三个部分。整个LVDS接收模块的结构如图11所示。

图11 LVDS接收模块顶层图

① CMOS输入参考时钟(INCK)为37.125MHz;

② CMOS输出LVDS数据为445.5MHz SDR型;

③ 时序发生器由74.25MHz发生30fps的XVS、XHS信号;

④ LVDS数据接收解码模块将数据恢复为8bit@55.6875MHz并行格式(DATA[7:0]);

⑤ 格式化输出模块通过搜索同步头的状态确定是否发出bit_slip,并根据CMOS的数据格式和同步信号格式化输出12bit@74.25MHz像素数据(PIX_DATA[11:0]);

⑥ IDELAYCTRL以Ref_clk为基准对整个IO BANK进行输入延时控制。

2.3.1 时序同步

同步时序由内部74.25MHz计数产生。按照图7所示时序即可。

2.3.2 LVDS接收解码

LVDS接收的主要工作是将串行的数据转为并行数据并进行自动相位调节,移位寄存器抽头调整(Bitslip)。Xilinx Artix7系列FPGA提供串转并模块ISERDES和IO延时模块IODELAYE2,ISERDES性能可在415Mb/s~1200Mb/s之间,IODELAYE2的延时参考时钟可以是200MHz(1tap≈78ps)或300MHz(1tap≈52ps)。

(1)Artix7 FPGA时钟特性

在Artix7系列器件里,MMCM可驱动BUFIO、BUFR、BUFH和BUFG,PLL只能驱动BUFH和BUFG。ZYNQ-7020采用Artix7 Speed-1器件,时钟网络的最高性能如下表5所示。

**表****5 Artix7 Speed-1 **器件时钟性能

(2)LVDS接收时钟选择

①LVDS解码串行参考时钟选择

从表1可以知道,采用BUFG最高时钟性能为464MHz。IMX122 1080P串行模式下两通道LVDS每通道的输出数据率为445.5Mbps(SDR),接近BUFG的极限值,因此这里作一个变通处理,使用222.75MHz时钟按照DDR****方式对串行数据进行采样。

②IODELAYE2 延时参考时钟选择

延时参考时钟选择的原则是在LVDS数据时钟周期内,可调节的Tap数尽量的多。IMX122输出的数据周期为2.245ns,调节一个周期采用200MHz参考时钟需要28taps,采用300MHz参考时钟需要43个Taps,而IODELAYE2的调节Tap数为0~31,故只能**选择****200MHz** 的参考时钟 。

(3)LVDS数据接收模块时钟

因CMOS IMX122不输出LVDS bit时钟,FPGA使用内部时钟来接收解码LVDS数据。如图12所示,与LVDS相关的时钟由同一个MMCM产生以保证其相位的一致性。其中:

① 37.125MHz,为CMOS工作参考时钟;

② 55.6875MHz,提供给IODELAYE2.C、ISERDES2.CLKDIV、补偿状态机及解码后的字节数据参考时钟;

③ 74.25MHz,产生30fps的CMOS同步参考时序和12bit像素参考时钟;

④ 222.75MHz,以DDR模式接收的DDR位参考时钟;

图12 LVDS数据接收模块结构

IMX122输出两路LVDS数据,每个通道的接收逻辑相同,对每一通道而言,数据流路径如下:

a)LVDS差分对通过IBUFDS_DIFF_OUT,得到位数据(记为Master)及与其反相的数据(记为Slave);

b)Master和Slave分别进入各自的IODELAYE2和ISERDES2得到各自的并行数据送到补偿算法状态机进行动态相位调整并反馈各自的延时值到IODELAYE2。根据IMX122的LVDS编码特点,ISERDES2按照1:8作串并转换最为合适;

c)数据格式化输出模块根据查找Sync Code的情况调整bitslip;

d)补偿模块根据数据调整的情况输出解码后的8-bit并行数据。

2.3.3 动态相位补偿

动态相位补偿原理如下:

① 初始化时,Master数据延时假定设为数据眼图的中间位置,Slave和Master的延时相隔半个数据周期。

② 在Master和Slave的数据不全为零或不全为壹时启动动态相位补偿算法。相位补偿的基本原理是:如果Master和Slave采样到的数据相同,则说明采样太靠后,延时减少一个Tap(如图13[a]);如果Master和Slave采样到的数据不同,则说明采样点太靠前,延时增加一个Tap(如图13[b])。

图13采样点延时示意图

③如果延时Tap值为最小或最大位置时,则交换Master和Slave的的参考关系,同时输出数据作相应调整;

2.3.4 数据格式化输出

该模块的工作是将收到的串转并数据的基础上搜索Sync Code、并组织成12-bit的像素数据按照给定时序格式化输出。

(1)Sync Code搜索

Sync Code搜索采用的策略是,逻辑在不停的查找在一帧数据里是否存在图3-2所示的的特定数据,如果这些同步码都能找到,则表示接收逻辑串转并的输出位顺序正常,不再需要bitslip;若没有找到全部的同步码,则在下一帧开始的时候(XVS上升沿)给出一个bitslip脉冲调整输出,直到找到完整的Sync Code。

两路LVDS通道分别单独进行Sync Code搜索,若32次bitslip 后任然没有找到Sync Code ,则报告CMOS 输出错误 。

(2)格式化输出

格式化输出模块完成将CMOS输出的数据解码成12-bit Pixel数据并按照视频格式时序输出,结构如图14所示。

图14 格式化输出逻辑结构

对格式化输出的详细实现过程这里不赘述。

2.3.5 接收模块顶层文件描述

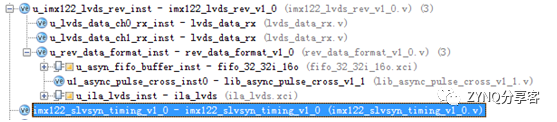

IMX122-LVDS接收模块由4个文件构成,分别是imx122_lvds_rev_v1_0、lvds_data_rx、rev_data_format_v1_0和imx122_slvsyn_timing_v1_0构成,它们的层析结构如图15所示。

图15 LVDS接收模块文件结构

注1:蓝色的imx122_slvsyn_timing_v1_0不属于LVDS接收内容,但CMOS在SLAVE模式下必须由它提供同步信号后才能正常输出。

-

RocketIO高速串行接口2014-03-01 3533

-

汽车类百万像素CMOS相机参考设计的高速串行视频接口2018-11-05 2348

-

轻松实现高速串行IO2020-01-28 3239

-

如何实现MAX121在高速串行接口电路的应用?2021-04-12 1113

-

怎么实现RocketIOTM GTP在串行高速接口中的位宽设计?2021-05-28 1493

-

BRDF测量系统中高速串行接口的设计2010-08-03 806

-

基于FPGA的高速串行传输接口研究与实现2010-09-22 635

-

高速串行接口设计的高效时钟解决方案2010-04-09 1400

-

高速DSP串行外设接口设计2010-04-12 931

-

高速串行接口链路层的电路设计与实现2017-01-19 760

-

Zynq高速串行CMOS接口的设计与实现2017-02-08 3396

-

UART逻辑实现高速异步串行通信2017-11-10 1294

-

如何设计实现Xilinx FPGA高速串行接口2020-08-24 1754

-

TIDA 00133高速串行视频接口参考设计2022-09-05 555

-

SPI串行外设接口设计实现2023-05-29 2343

全部0条评论

快来发表一下你的评论吧 !