SOC TOP的设计与仿真

电子说

描述

SOC芯片的基本构成

这是SOC的简介,我们知道SOC的概念是相对于传统的计算机基本架构来说的。传统计算机我们都知道有CPU核,有总线,有各种内存,还有硬盘,各种外设。SOC实际上就把这些概念、模块集成在一起,做在同一个芯片上面。大规模的SOC,像我们熟悉的手机上的SOC芯片,比如说华为的麒麟,高通的骁龙芯片,都是AP芯片,事实上它里边有多个CPU的核心,包括还有GPU,基带的处理,还有很大规模的缓存。这些芯片主要是处理数字信号为主要功能,所以通常使用Digital Top Down的设计方式。

模拟功能为主的小规模的SOC,同样也有CPU、存储器和外设这些模块,可以说是麻雀虽小五脏俱全,以这些小规模的SOC作为一个切入点能够去一窥SOC的一些设计方法,是一个很好的途径。这些小规模的SOC往往能用于某种专用模块的控制、协议的处理和信号的收集,由于需要内置多种模拟模块,数字电路实际上只占用其中的一部分,其中模拟信号与数字信号有大量的交互信号及信号处理,所以比较适合于这些Analog on Top的设计流程。

这张图是SOC芯片的基本构成,中间是数字的控制电路,通常有微处理器、总线、SRAM (缓存,或者叫内存)、有NVM(非易失性存储器),比如说像FLASH、EEPROM,或者OTP、MTP,还有外设的一些控制电路。

绿色的部分是模拟的模块,通常有OSC振荡器,有作为数字和外界的窗口ADC或者DAC,有逻辑控制的GPL作为通用的I/O接口,为了给数字电路供电有LDO,因为数字电路需要比较稳定的电源。

右边第一个是PHY,是协议物理层,通常它本身也是一个数模混合的模块,它既有数字电路也有模拟电路,把它放在这里就表示需要模拟工程师对它进行重点的关注。还有作为对微弱信号处理的放大器和AFE,AFE是模拟前端,将模拟信号经过放大处理,把它输入到ADC或者数字电路当中。PowerManagement是经常会用到的一个模块,包括BUCK,BOOST或LDO这些模块,另外就是传感器的控制电路。前面这几个模块每个芯片都不一样,有可能有,有可能没有。但是左边这一列,基本上每个SOC芯片都会有。

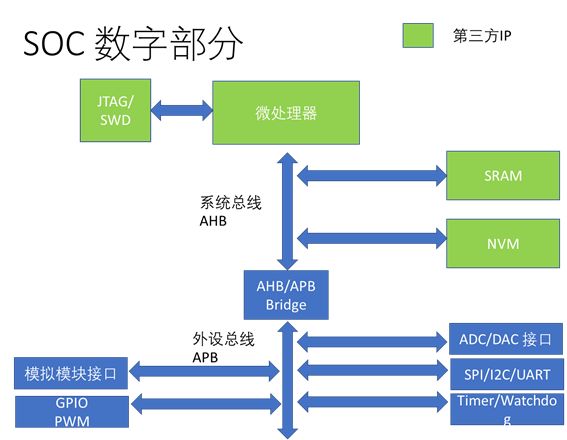

这里讲讲SOC的数字部分的结构,标成绿色方块的部分是第三方的IP,是需要向IP供应商去购买的,也有一些是自己设计。

微处理器是最核心的部分,比如向ARM购买的IP,有高端有低端的,低端如M0、M1这些32位的处理器,它往往需要一个DEBUG口,DEBUG口往往是JTAG或SWD。微处理器需要内存,以及用于存放程序的NVM,跟它通讯时使用系统总线叫AHB,ARM的话叫AMBA总线。

AMBA总线处理比较复杂,所以处理一些比较简单的外设的时候,是通过从AHB到APB的桥接。

ADC或者DAC的这些接口是通过AHB的总线来控制的,其中包括一些跟外界的接口,像SPI接口、I2C接口或者UART、Timer、Watchdog、GPIO、PWM控制,还有这里比较关心的是模拟模块的接口。

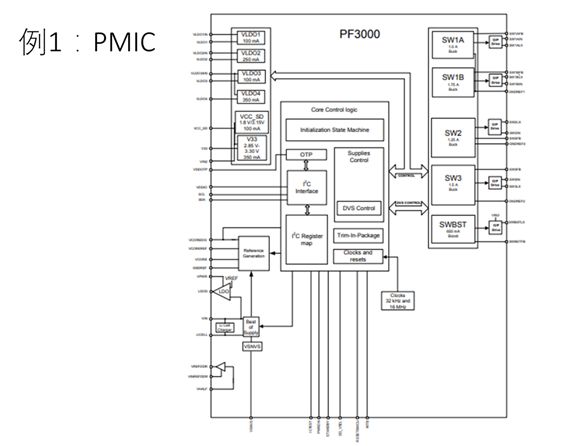

讲了这么多,先来看几个例子:这是一个PMIC,它是Freescale公司的给系统供电控制的PMIC,这个芯片是要根据外面系统上的主AP控制,针对主AP能够控制电源的每路输出,或者对输出上电时序进行控制。

这个芯片可能是一个State Machine,也就是说相当于把内部的Firmware给固化了。但是我们也同样可以看到它有相当多的数字控制逻辑,包括我们刚才讲的模拟部分的OSC、Reference、LDO,还有左下角的锂电池的充放电管理,上面几个大的是LDO、BUCK、BOOST 这些Power Management模块。

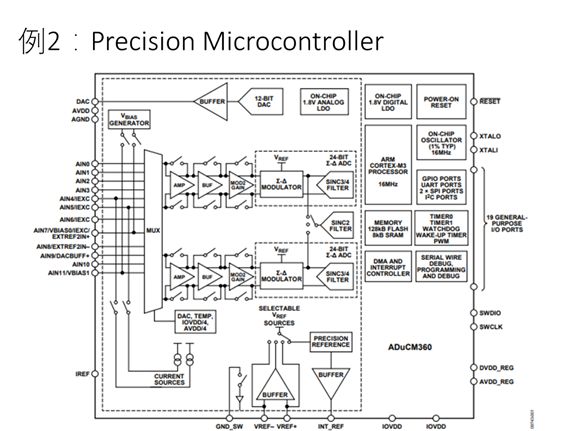

我们再来看看另外一个芯片,这个是Precision Microcontroller,这是ADI推出的一个对于微弱信号进行放大采集的一个SOC,可以看到右边内部有一个ARM的M3的处理器,为了给这个处理器提供时钟,有一个片上Oscillator,GPIO,UART,SPI、I2C接口都存在,还有很多个Timer、Watchdog、DEBUG接口,包括有一个128K的FLASH和8KB的SRAM。电源的供电是通过片上的1.8V LDO,左边的模拟部分有12位的DAC,有24位的ADC, ADC的前面有放大器,Buffer跟PGA。

通过前面这两个例子,我们能够看到一个小规模SOC的基本构成,加入了一个内核以后对于芯片的可重构特性会大大的凸显出来,能够适用于多种场合的不同应用。

SOC TOP的设计

现在讲讲SOC TOP的设计,后面的讲解以问答的形式。这里提出三个问题,第一个是SOC的Analog on Top的设计环境是什么,第二个是SOC TOP的设计与ASIC设计有什么不同,第三个是SOC TOP设计与模拟设计有什么不同的地方。

作为一个SOC设计,它的主要难点是需要同时去整合这两套设计流程,而且要在顶层将这两套设计出来的东西放在一起。

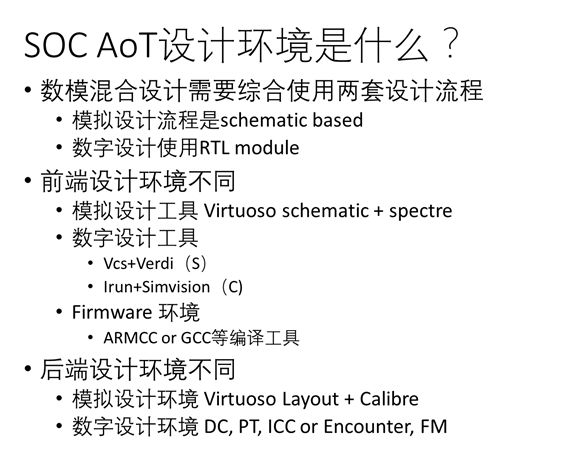

SOC的TOP设计环境是什么呢?我们知道数模混合设计环境是需要综合使用两套设计流程,模拟工程师比较熟悉的一个设计流程是Schematic Based,数字设计使用的是RTL module的形式。

对于一个模拟设计者来讲,熟悉的工具就是Virtuoso schematic + Spectre。数字设计工具Synopsys用的是VCS+Verdi,Cadence用的是Irun+Simvison。除了这两套工具之外,还需要搭建Firmware的设计环境,因为我们要验证SOC,没有程序是跑不动的,那要写程序或者要编译这个程序需要用到ARM CC或者像GCC之类的编译工具,环境需要搭建。

后端的设计环境也是有相当的不同;模拟设计往往用Virtuoso Layout,再加上Calibre,做LVS和DRC;数字设计环境的话,首先需要去DC综合,时序分析PT,自动布局布线往往使用ICC或者Encounter,后面FM是形式验证,还有包括测试Patten的自动生成这这类工具。

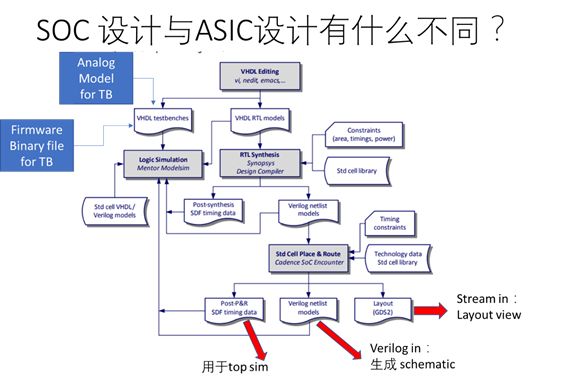

这个图是从网上下载下来的一个ASIC设计的一个流程图,我们可以看到一开始是用文档编辑工具去设计数字电路(硬件描述代码),把它制作成Testbench和Hierarchical的Modules,这些Modules首先用仿真工具去仿真,没有问题以后对他进行DC综合,综合完了以后生成Verilog的Netlists,再对Netlists进行PR。

PR完成以后会有三个文件:一个是GDS,第二个是Verilog的Netlists,还有一个是PR以后的Timing信息叫做SDF文件,这三个文件在后面的设计当中都会用到,但是在对于ASIC来讲,到这里可能就已经结束了。

有不一样的地方标出来了,就是在左边,在Testbench的设计阶段就需要一些Analog的Model,给到Testbench,对这个数字控制模拟或者模拟返回到数字的这些信号进行模拟。还有是Firmware的Binary file,就是固件的二进制码,也要给到这个Testbench,才能够对SOC进行仿真。

输出的文件处理,会把GDS导入到Analog设计Layout中,使用Virtuoso的Stream in导入;对于Netlist,会把它用Verilog in的方式生成Schematic;SDF文件也是必不可少的,在仿真的时候要用于TOP SIM的timing的仿真,如果没有这个文件的话,有可能Verilog Netlist in的文件由于时序不对没办法做正确的仿真。

SOC设计与模拟设计有什么不同呢?

在上面我们会先去设计Block level,然后把它组成一个Analog TOP的Schematic,这个是没有Digital模块的,但是它会有一个Digital的空的block。

TOP仿真的时候是使用Digital的RTL、IP的Model和Firmware组合在一起进行Analog Top的仿真,这时因为没有数字的Schematic,所以只能用AMS的方式进行仿真。

这步仿真通过以后,我们会对Digital进行PR,PR完了以后会由SchematicVerilog-in进来,组成最终的TOP的Schematic。对这个Top的Schematic进行PR后的仿真,这个仿真比较简单,不会像前面那个Analog TOP的仿真这么详细,后面只是简单的验证一下最后的电源轨和模块连接是不是准确。

从后端上来看,在Analog Block Level或TOP做完以后马上进行Analog layout,这时会等Digital PR完成,完成以后会Stream-in进来,两个组成在一起形成TOP的Layout,当然还有一些购买的IP,有些IP可能不会给底层的GDS,只会给Phantom View,Phantom View拿进来以后形成TOP的Layout,再对它进行LVS。

SOC TOP的验证

后面我们讲一下SOC TOP的验证,这里也采用问答形式,主要回答四个问题:第一个是怎么去仿真SOC TOP;第二个是我们重点要验证哪些项目;第三个是我们经常会遇到的仿真速度很慢,我们怎么办;最后一个是要不要做FPGA验证,这也是经常会遇到的一个问题。

怎么去仿真SOC 的TOP?一个最基本的验证方法是使用Virtuoso AMS仿真工具,我们先列一个TOP的Verification list,对它进行一个个的人工检查,这是一个最基本的验证方法。群主她们有一个更加高级的自动化的验证工具,我们没有这个条件,只能是比较原始的方式去人工检查。

对于很多初学者或者对于一些小规模的SOC来说,这种验证方法是足够的。首先需要一个Config的文件,这个文件是Analog用于定义Schematic Hierarchy的View的方式,可以指定寻找View的顺序,比如说优先寻找Schematic,再允许去寻找某一些模型。

这个时候针对Digital的Block,我们只需要指定顶层,指定顶层以后,因为Digital是需要有很多的Module组合在一起的,那么怎么去设置这个Module的寻找路径呢?需要在Virtuoso AMS的设置里面去设置一个Digital的文件列表;第三个,在TestBench上面加一个模块去设置仿真的初始条件。

先看看仿真器的设置,仿真器设置主要是Config file怎么去设置。在RTL仿真时,我们只需要去指定Digital Top的Cell View。举个简单例子,我们可以把Digital的Top,设置成functional,或者说是Schematic,都可以,那对functional只需要digitla 的top,它里边会引用到很多的其它的Module,这个时候Config是指定不了的,需要在Virtuoso的AMS Option里边去设定一个.f文件,这个.f文件里面设定了它的Module的全路径。

另外一种方法也可以只在Digital TOP上做一个空的Schematic,再加一个Stop Point,加了这个Stop Point以后不会再往下去生成网表,只是在Schematic这一层生成一个空的,这时候,它会去在.f文件当中找相应的Module。

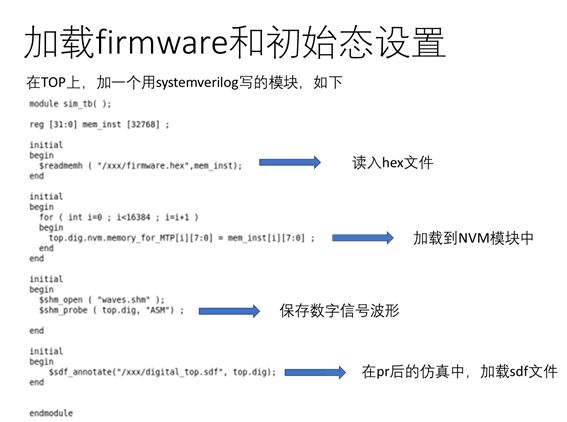

在TOP上我们还需要加载一个System verilog写的模块,这个模块用于加载Firmware和初始态的设置。这里是一个例子,我们把这个Module生成一个Symbol,把这个Symbol放到TOP上就可以了。我们可以看到一开始会去读入一个16进制HEX的Firmware文件,把它放到缓存当中,然后在初始化的时候把这个缓存一个个的写入到NVM当中。

第三是用两个语句去保存dig.top的数字波形,把它存放到Datebase当中。最后一个是在PR后的仿真中有用,在这里设置它的Timing信息sdf文件,因为只有设置文件后跑出来的数字时序才是正确的。

SOC TOP重点要验证哪些项目呢?这里以我自己的经验写了几项:第一个是上电使能的顺序是重点需要验证的,因为在数字模块当中事实上没办法去验证上电的时序,所以在这块需要重点验证;第二个是在多电源轨的设计当中电平转换是不是正确,初始态也就是在Level Shift掉电的时候,是不是能够输入正确的初始态,这需要去做验证,因为我们在数字仿真当中是没办法去做多电源轨的验证,所以需要重点确保没问题。

另外还有数字模块输出的初始态是不是正确,这点很多人可能往往会忽略掉,因为在模拟设计当中我们事实上不太清楚数字输出,或者说我们经常会默认为数字模块输出是一个零状态,事实上有可能不是,这个是需要去确认的。标红色的几项需要花大量精力去做,第一个是模拟模块与数字模块之间的连接是不是正确,这个是Mixed signal主要需要验证的地方,第二个是需要与数字模块交互的模拟模块,这个非常费时,因为如果一旦出现这种交互的话要等到数字内部初始化完成才能够仿真到需要的状态。

第三点也是比较麻烦的,是测试模式的仿真。这里主要是一些测试模式接口,像测试模式入口、在线仿真入口,还有测试Pattern入口,这些事实上都是在不正常工作的时候的一种工作状态。由于它不涉及到正常工作模式的状态可能有些人会会忽略掉,但是一旦忽略的话,往往有可能这些测试模式是不成功的。

最后一个是异常的一些处理,包括下电或者电源上毛刺的处理等。

仿真速度很慢怎么办?仿真速度慢首先我们要去检查慢的原因,数字信号变化是不会使仿真变慢的,模拟信号变化如果触碰到一个阈值会引发一次计算,我们知道模拟的计算是一个矩阵计算,如果是大规模的模拟模块的话,它的仿真速度是将会非常慢,第三点就是模拟信号的一些不连续,叫做硬转折,它会造成收敛性的问题,一旦碰到收敛性问题,会让速度变得很慢。

加快仿真的方法有下面的几点:第一点是我们可以用仿真器的Debug模式去检查仿真慢到底慢在哪里,它的原因是什么;第二点一个基本的方式是我们把那些验证项目不涉及到的模拟模块用模型去代替它,这样的话会避免不必要的模拟计算量;第三点是减少不必要的模拟信号的变化,这点后面会讲到;第四个是优化涉及时钟的模块。

检查仿真慢的原因,Debug模式是怎么做的呢?我们在Virtuoso里面Simulator option上添加一句diagnose=detailed,这样的话就能够打出很多的仿真过程当中的一些信息。观察log文件,去看哪个模块的信号将仿真的step变小了,或者在哪个点触发了一次新的计算,去看这次计算是不是你想要的,或者说是不是可以避免的。

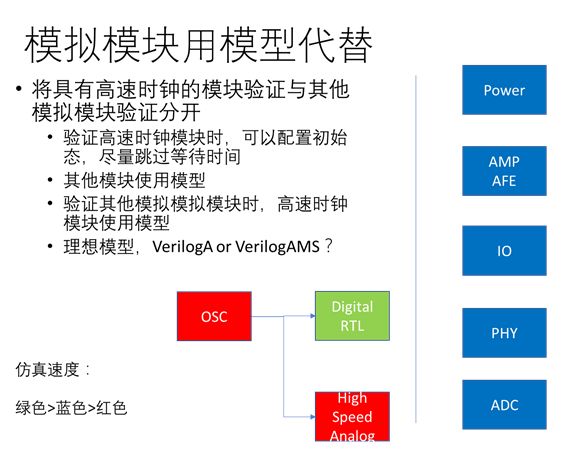

加快仿真速度的基本方法就是把模拟模块用模型去代替,这里我画了一个图,它的仿真速度绿色的最快,蓝色次之,红色仿真速度最慢。什么东西仿真速度是比较慢的?一个是Oscillator,然后用到这种高速时钟的高速模拟模块,比如说高速ADC。什么东西是仿真速度比较快的呢,其他的一些模拟模块,事实上只要它不涉及到动态波形、动态信号的话,它的仿真速度都还是挺快的。

为了加快仿真速度我们要把高速时钟模块的验证跟其他的模拟模块的验证分开来,验证高速时钟模块的时候可以配置一些初始态,尽量尽快地跳过等待的时间,让它尽快的能够验证到你想验证的一些信号。

这个时候其它的模块使用模型,验证其它模拟模块的时候高速时钟使用模型。这里有个问题就是,往往对模拟设计工程师来说不太熟悉Verilog-a或者Verilog-ams,就用理想的模型去搭了一个,那这种方式合不合适呢?

我们这里来看一个例子,以一个4M的时钟作为一个例子来看看Verilog-a和Verilog-ams写的模型的方法。对于Verilog-a来讲,这里写的是一个4M的时钟,所以每过125ns会翻转一次,osc_4M这个信号是个整形,要把这个整形变成一个输出,这个输出是一个模拟信号,所以要使用transition这个语句。这里需要注意,如果这个信号不用transition的话,有可能会遇到硬转折,也就是说有收敛性的问题。

加入了transition以后会添加一个上升时间、下降时间、一个Delay时间,把它从0-1变成VDD、VSS的信号输出去。如果用Verilog-ams就比较简单,可以直接用类似于Verilog写的语句,把它定义成一个逻辑信号,直接在125ns翻转一次就可以了。

但是事实上我们会发现,不管是Verilog-a还是理想模型都是一个模拟信号,一旦是模拟信号的话,那么它就会频繁的去触发模拟计算。举个例子,我们这里的transition语句,它每碰到125ns的时候就会去算,把它形成一个ramp波形,这个波形的计算可能有好几个点。

我们来看使用Verilog-a和Verilog-ams有什么不一样的地方,在上面这个图我们使用Verilog-a,使用了Verilog-a以后可以看到OSC的理想模型输出是模拟信号,然后输入到Digital的RTL是数字信号,数字信号还是很快的,模拟信号比较慢,但是因为它已经变成了一个非0即1的或者说计算量很小的模块,所以我们认为它计算量很小,然后把它输入到高速的RTL模块,这个模块也用Verilog-a去写。

我们可能会认为这样的写法会让仿真速度大大加快,事实上它是可以加快点,但是并没有很多,为什么呢?因为它存在模拟到数字的转换,它在每半个时钟都会去打断一次,就会做模拟的计算。虽然模块本身的模拟计算很小,但是他这个模拟计算会触发其他所有的模拟模块,所有模块加起来的计算是很慢的,因此它事实上速度不会快很多。

为了加快仿真速度,我们可以用下面这种方式去写,Oscillator用Verilog-ams,High speed analog也用Verilog-ams去写,这样的话在链路上面没有模拟通路,所以这个链路用绿色去表示,它是一个Logic的信号,而不是analog,它并不会触发模拟计算,所以会大大的加速模拟计算的速度,或者说是减少模拟计算工作量。我有一个例子,同样的一个仿真Case用上面这种模型去写仿真使用了大概几天的时间,改用了下面的方法以后一个小时就可以跑完了。

验证的最后的一个问题是经常会听到说要不要去做FPGA验证?对于FPGA验证来讲去验证数字模块是非常有用的,因为刚才看到我们买了几个IP是绿色的,但是蓝色还是很多,这个时候FPGA验证的应该是可以的,而且是比较有效的。事实上简单的数字模块的仿真验证是能够覆盖的,复杂的数字模块比如说有上位机的软件的互动,有这些东西的话呢,FPGA验证可以有效的减少仿真验证的工作量,另外对于需要提前开发软件,开发一些烧录工具或者自动测试是有帮助的。

但是坦白讲对于数模混合来讲FPGA验证环境是很难搭建的,因为对于模拟模块来讲,很难去找现成的比较接近的模块,要去验证它的话,需要搭建很复杂的接口,还有一些电源轨的转换,都非常复杂,所以我们目前AOT的TOP主要是以仿真验证为主。

经验分享

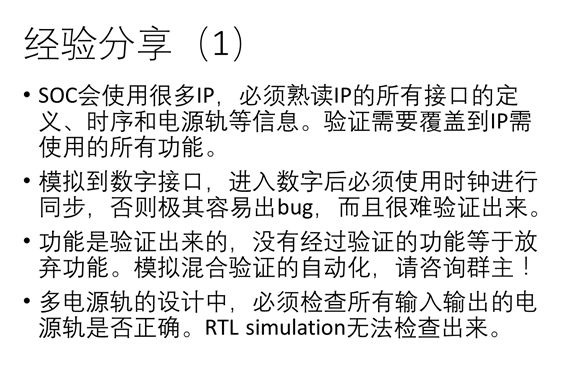

今天的分享最后讲讲几个经验:第一点是因为SOC会使用很多的IP,所以我们必须要去熟读IP的所有的接口定义,还有它的时序跟电源轨的信息,验证要覆盖到我们用到IP的全部功能。这里其实有很多教训,IP文档读的不够仔细或者使用错误出现的问题,虽然大部分问题是可以在仿真的时候能够验证出来,但有的时候比较偏的一些功能没有仿到,没有覆盖到,就会有问题或缺陷。

第二点是模拟到数字的接口进入数字后必须要使用时钟进行同步,否则非常容易出Bug,而且很难验证。因为这种Bug,只有在模拟信号正好在数字的时钟上升沿那一瞬间来的时候变化才会遇到问题,所以很难去验证到。

我们经常讲的一点就是功能事实上是验证出来的,某个功能没有经过验证,相当于说是你可以不关心或者放弃这个功能,这个时候模拟混合验证的自动化的优势就体现出来了,因为它能够在一开始,即设计阶段就能够去定义哪些功能需要验证,而不是在最后列个List一个个去检查,因为到了那个时候是时间是非常有限的,可能来不及。

还有很重要的一点就是在多电源轨的设计当中必须要检查所有的输入输出电源轨是不是正确,因为电源轨的问题RTL Simulation经常没有办法检查出来。只有在模拟的仿真中才知道,比如输出1.8V到了5V的电源轨,或者说5V的电源轨到了1.8V,那肯定器件就坏掉了。

第二再分享一个小工具,有些IP的供应商对于Standard Cell经常不提供Schematic view,这怎么办?事实上,我们可以通过IP供应商提供的Spice model,或者说CDL网表,能够自动的生成Schematic view。左边是我们经常看到的一个Standard Cell的与门,可以看到里边有网表,P管用PD来表示,N管用ND来表示,前面是它的连接,后面是W、L和multiple。在Spice in的时候,通过device map把这个MOS管PD对应成PMOS 5V的管子。可以把P管对应成PMOS 5V,然后是他的Pin order,Property需要注意一下,因为Property定义了W、L对应的是什么参数,W对应的W,L对应的L,但有的时候m要根据实际情况要去做修改,定义它的PDK里面的参数是什么。

使用了这个工具,最终导进去以后会发现虽然把W、L、m改对了,Model可能也改对了,但是其他的一些CDF参数没有刷新,这时候怎么办?因为如果我们光拿它来做LVS的话是不影响的,因为在LVS当中网表就是这个样子,它只用到了这几个参数,但是在其它电路仿真的时候如果用到Standard Cell,它的CDF参数没有刷新的话有问题。

说明一下,CDF是PDK里边经常看到的与器件相关的一些模拟参数,比如说Drain或者是Source的宽度,它的寄生,因为它要根据WL变化,所以它实际上是一个可变量,能把这个变量通过CDF传递到网表当中去。

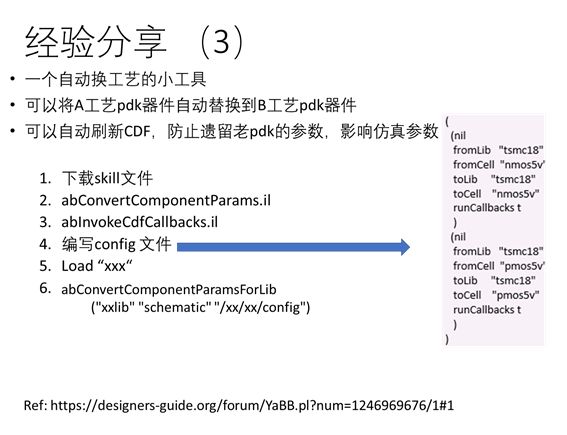

如果这个CDF没有刷新怎么办呢?这里有一个工具能够去刷新这些CDF的一些参数。事实上这个工具不仅仅可以去刷新参数,还可以自动去替换工艺,这事实上是一个自动换工艺的小工具,可以把A工艺的PDK器件自动转换到B工艺的PDK器件。

转换以后同样需要去刷新CDF,防止老PDK的参数影响到仿真参数。这个工具怎么用呢?可以去下载这两个Skill文件,用搜索引擎应该能够搜到,它的一些讨论也在下面这个reference的网址当中有讲到。这两个文件里边有说明文档,需要去编写这个config文件。就是A是什么工艺,把A工艺中的一个器件把它自动地换成B工艺当中的一个器件,然后再运行Callback。

我这个Config文件只是去刷新CDF的参数,所以它换成的工艺库还是原来的工艺。有了这几个文件,首先去Load前面两个Skill文件,然后使用下面对整个库进行替换的命令就可以了。

-

vivado跑tb_top,前仿可以通过后仿通不过,为什么?2025-11-07 2316

-

E203仿真编译filelist的使用2025-10-24 214

-

如何在Vivado上仿真蜂鸟SOC,仿真NucleiStudio编译好的程序2025-10-21 230

-

Analog On Top的SOC如何做Top设计?2023-11-07 2050

-

介绍一种ISE联合仿真转换为Moldelsim单独仿真的方法2023-01-29 2804

-

一文浅谈SoC功能验证中的软件仿真2023-01-12 1948

-

如何对基于STM32 Soc的STM32-P103进行QEMU仿真2021-11-03 4846

-

基于扩展卡尔曼滤波的SOC估算仿真2021-08-25 1496

-

求一种数模混合SoC设计协同仿真的验证方法2021-04-23 1549

-

如何缩短SoC的仿真时间?2019-11-11 3325

-

新思科技Synopsys收购SoC验证仿真公司EVE2012-10-09 1610

-

用SystemC进行SoC的系统级设计与仿真2009-05-18 721

-

一种数模混合SoC 设计协同仿真的验证方法2009-05-15 693

全部0条评论

快来发表一下你的评论吧 !