UART通信原理详解

通信网络

描述

UART的概念

通用异步收发传输器,通常称作UART,是一种异步收发传输器。是异步通信协议。特性:两根线,全双工,异步通信,速度较慢。也就是一根发送数据,一根接收数据,并且 电平逻辑是时间的函数。 发送和接收一个bit都有固定的宽度,也就是只有等于这个时间宽度时才认为是1bit。为了约定时间宽度,就诞生了比特率的概念: 表示1s信号可以传输N bit的数据 ,单位bps=bit per second。比如,9600bps = 1s发送或接收9600 bit数据,那么1bit数据时间宽度也就是1/9600 s。

常见比特率——9600bps 19200bps 38400bps 57600bps 115200bps

什么是RS232

RS232是物理层的电气接口要求。是一种接口标准。uart可以使用rs232物理层来通信。总的来说,对于一项通信任务,通信协议可以使用UART协议,而UART协议可以通过COM端口来实现硬件连线,此协议下的传输方式可以选用RS232或者RS485等。

UART协议格式

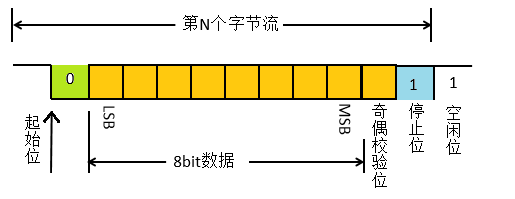

信号线上空闲的时候为高电平,当出现下跳到低电平的时候表示数据的起始位,接着是先发送低位(LSB)后发送高位(MSB)的数据流,尾部可加奇偶校验位,最后加停止位,停止位长度可以定义。本例实现无奇偶校验位,1bit停止位,波特率9600~115200可改变。

多帧发送结构如下:

代码实现解释

发送和接收准确的说就是用一个计数器作为状态机,计数器到每个特殊的计数值的时候发送1bit固定数据。代码注释都有,大家可以仔细看看。里面用到了状态机,边沿捕获技术这两个操作都是最基本的,大家仔细阅读代码的话会有收获的!

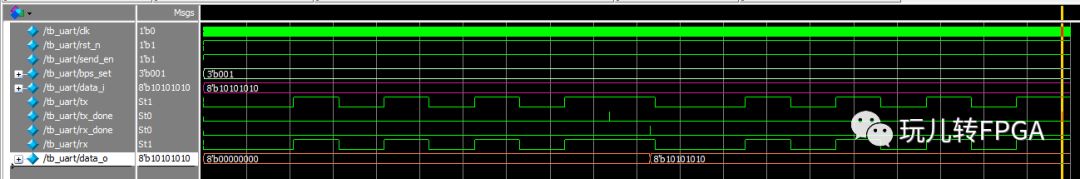

下面是我的仿真结果波形:

测试tb里面有对输出波形检测的代码,可以不用看波形知道结果是否正确,打印的测试结果如下:

强烈建议:

tb最好能能够输出一个信号让你能够一眼看出对与错不用看波形去判断,这样既节省精力,代码更改后也不用重复去看波形,可维护性也提高了。

verilog理解技巧

接下来给大家讲讲代码风格和常见的理解代码的方法。

正确性,他代表能够在某芯片上实现需要的功能

可测试性,要能让tb和上板的时候比较方便的看出模块运行结果对错

可读性,能够让人比较清晰的看明白模块实现的功能,多加注释就是技巧之一

可维护性,这一点里面包含了可读性,可读性不好,可维护性也就不好,除了可读性影响维护成本以外,参数化也是影响维护性的一个重要因素,改一个参数和改一片数字大家应该知道哪个头疼,尤其是你忘了这些数是干嘛的时候。

assign语句不要认为是连续赋值,要看做是从A连接了一根导线到B,A可以是寄存器也可以是wire,但是B只能是wire,因为assign只是连线,没法产生触发器,同时连线是单向的,因为FPGA内部布线路由就是“单行道”。

比如assign a = b;表示把a和b连上,并且信号只能从b传递到a。

always@()不要理解为括号里任何信号变化都会引起always内部语句的触发,要理解为产生一段组合逻辑电路,因为已经涵盖了所有信号,所以也不用担心漏掉。比如always@( )begin a = b & c ; a1 = a;end 表示产生了两个组合逻辑,第一个是a信号通过b和c与产生,第二个是a1通过a产生,不要把阻塞式赋值理解为先执行前面一句再执行后面一句,要理解为信号经过了a = b & c电路再到a1 = a电路,要看信号流的顺序不要看语句的先后。比如always@( )begin a1 = a; a = b & c ; end和上面产生的电路是一样的。阻塞语句原本就是为了描述组合逻辑的信号流顺序的,因为组合逻辑里面,输入信号必然一层层经过逻辑门传递,最终完成逻辑运算。电路如下:

同理always@(posedge clk)要理解为产生了一个时序电路。比如,always@(posedge clk)begin a<= b & c ; a1 <= a; end表示产生了两个时序电路,第一个电路是时钟上升沿到来,b与c立马赋值给寄存器a,第二个电路是上升沿到来a立马赋值给a1。电路图如下:

和组合逻辑的区别就是a是b&c上一次的计算结果,a1是a上一次的计算结果,都慢了一拍,因为中间加了一个寄存器。强烈推荐写verilog的时候组合逻辑全部用=,时序逻辑全部用<=,因为这样能够让你很明确的知道自己在设计什么,混用的话你根本不知道编译器会综合成什么样子,lattice的编译器对混用还会报错。所以要用机器的思维去理解代码,当你摸不准机器的思路的时候就不要想当然。

-

详解UART转CAN应用方案2018-12-05 36375

-

UART通信原理详解2023-09-21 3068

-

uart通信的详细讲解2023-09-22 4458

-

单片机SPI通信和UART通信原理详解2018-07-19 2634

-

niosii的UART串口通信2016-04-06 700

-

uart串口通信介绍2017-11-20 28906

-

基于51单片机的UART串口通信2017-11-21 64403

-

UART通信转CAN通信配置软件2021-03-01 1655

-

串口UART通信详解介绍(小白初学,浅显易懂,基本知识)2021-11-25 1120

-

基于STM32之UART串口通信协议(一)详解2021-11-30 1707

-

STM32-UART通信2021-12-20 1126

-

UART串行通信模式2022-01-14 783

-

UART串口通信协议详解2022-09-07 9378

-

UART通信简介,UART如何工作2022-09-09 2826

-

UART系统配置步骤详解2023-06-05 4566

全部0条评论

快来发表一下你的评论吧 !