testbench是什么? testbench测试的机制是什么?

电子说

描述

01

testbench是什么

废话不多说直接上干货,testbench就是对写的FPGA文件进行测试的文件,可以是verilog也可以是VHDL。

verilog和VHDL的国际标准里面有很多不能被综合实现的语句,比如initial,forever,repeat,延时语句#1等等,这些语句就是用来测试的时候使用的。运行环境一般是ise或者vivado自带的仿真工具,或者如modelsim一样的第三方仿真工具。

02

testbench测试的机制是什么

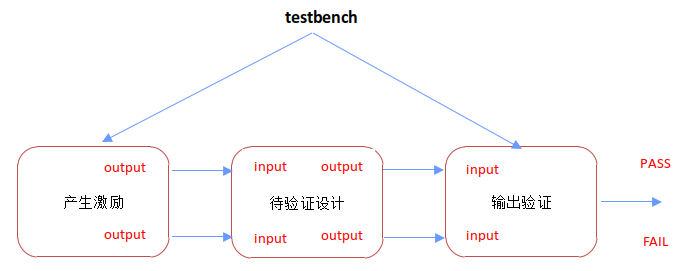

任何一个设计好的模块(比如第一讲的PWM产生模块),都有输入和输出,此模块是否满足要求就是看给定满足要求的输入,是否能够得到满足要求的输出。所以testbench的测试机制就是 :用各种verilog或者VHDL语法,产生满足条件的激励信号(也就是对被模块的输入),同时对模块的输出进行捕捉,测试输出是否满足要求 。如下图,产生激励输出验证模块两个模块都属于testbench,最好的输出验证模块最终只需要给一个pass和fail的答案出来就可以了。不管是用一个信号表示pass和fail还是用$display()函数打印,最终简单明了的给出过或者不过的信息就好了。请大家写仿真文件的时候尽量做到这点。

03

testbench运行顺序之谜

首先,跟大家解释一点,所有testbench本质上都是串行执行,因为在CPU环境下,没有可靠并行执行的能力。所有并行的语句,比如两个always模块,fork join语句块,都是软件模拟并行执行的。所以老一点的编译器,信号定义要在initial语句前面,initial的信号要先有初始值后面的语句才能从给定初值开始执行。所以大家写testbench的时候,要注意,最好先定义信号,再写initial语句,后面的语句交换顺序不影响,软件可以识别并按照IEEE标准的顺序去执行。

如果一个模块里面想用并行执行语句用fork join语句,顺序执行用begin end语句。initial语句可以写多个,都是并行执行的,当两个信号在initial冲突的时候,会先执行前面的initial的值。

04

常用testbench语句总结

时钟产生——always begin clk = 0; #1 clk = 1; #1; end 。注意这里的always后面没有@!没有@的时候always代表永远循环执行begin end之间的语句,如果有@,后面一定要加时钟,代表时钟边沿来到的时候顺序执行begin end里面的语句。没有@的always语句不可综合。

时间轴设置——'timescale 仿真时间单位/时间精度; 比如`timescale 1ns / 1ps;代表仿真的时间轴单位是1ns,仿真工具仿真的最大精度只到1ps内的逻辑变化。

延时语句——#n; 代表延时n个时间轴单位。比如之前定义了`timescale 1ns / 1ps;如果后面写 #3;就代表延时3ns而不是延时3ps。

初始化——initial begin a=0; #100; a=1; end。testbench在运行起来之后,第一个进入初始化语句,并且只执行一次停在最后一句,然后才是后面的语句。由于begin end里面的语句是串行执行的,所以这句话代表a低电平100ns后永远为高。复位信号常常这样产生。

系统函数——**stop;代表运行到这一句停止仿真,**dispaly("pass");代表在命令行显示pass这串字符。

等待语句——wait(条件表达式) 语句/语句块; 语句块可以是串行块(begin…end)或并行块(fork…join)。当逻辑表达式为“真”时,语句块立即得到执行;否则,暂停进程并等待,直到逻辑表达式变为“真”,再开始执行后面的语句。

关于verilog测试激励的语法请打开,里面有所有的仿真激励:

打开菜鸟教程——资料下载——选择“verilog最经典中文教程”

另外提一句:学verilog要知道verilog语句的执行顺序和机制,生成的对应时序,哪些语句可综合哪些不可综合。这是最基础的要求。

05

其实看了之前的链接大部分大家应该都能看明白了,现在只拣之前没讲的代码讲。

-

testbench 设计教程2013-09-12 9299

-

testbench设置的问题2017-05-21 3379

-

LFSR testbench V1.22009-05-14 1085

-

Writing Testbench2009-07-10 1334

-

编写高效率的testbench2016-05-11 768

-

testbench_book2016-12-13 772

-

testbench怎么写_testbench经典教程VHDL2017-12-01 58134

-

简单的Testbench设计2019-03-08 3065

-

使用Matlab和Verilog实现fibonacci序列包括源代码和testbench2021-09-16 917

-

Verilog testbench总结2022-07-07 5154

-

典型的UVM Testbench架构2023-05-22 3565

-

Verilog Testbench怎么写 Verilog Testbench文件的编写要点2023-08-01 6095

-

Testbench的基本组成和设计规则2023-09-01 2454

-

Testbench自动化验证方法介绍2023-09-04 2059

-

编写高效Testbench的指南和示例2024-10-29 3331

全部0条评论

快来发表一下你的评论吧 !