了解芯片贴装热性能

电子说

描述

内容摘要

电力电子元件可提高所有行业和应用中电机和马达的能源效率。这些电力电子元件越来越多地被更密集地封装在一起,靠近或放置在电机本身附近或上面,因此受到应用中的声振粗糙度和振动的影响。必须有效地消除这些组件的散热,以防止器件过早失效,或者在最严重的情况下,泄漏电流随着温度的升高而增加,导致热失控,进一步增加散热,直到半导体芯片实际熔化。

安森美半导体承诺向客户提供最高质量的产品,为此,必须了解如何以尽可能少的缺陷引入和生产宽带隙半导体等新技术,以便在部件经历温度波动时提高器件性能和可靠性。

这些温度波动会导致焊料芯片贴装开裂,或芯片贴装与芯片之间或芯片贴装与基板之间分层。这反过来又导致芯片温度升高,因为从芯片到环境的热流路径被破坏,进一步提高了温度波动的大小,从而进一步加快了损坏速度。器件寿命取决于许多因素,但根据芯片的工作温度,安森美半导体知道,在相同的负载率下,温度升高 10° C 大致相当于寿命减少两到三倍。

焊料芯片贴装中可能发生的孔洞具有使芯片贴装导热性降低的综合效应,并充当可能形成裂纹的部位,因此焊料芯片贴装孔洞是电力电子封装中的主要可靠性问题之一。芯片贴装孔洞的影响取决于焊料中孔洞的类型、图案和孔洞的位置,因此真正了解这些孔洞对芯片贴装热阻的影响至关重要。

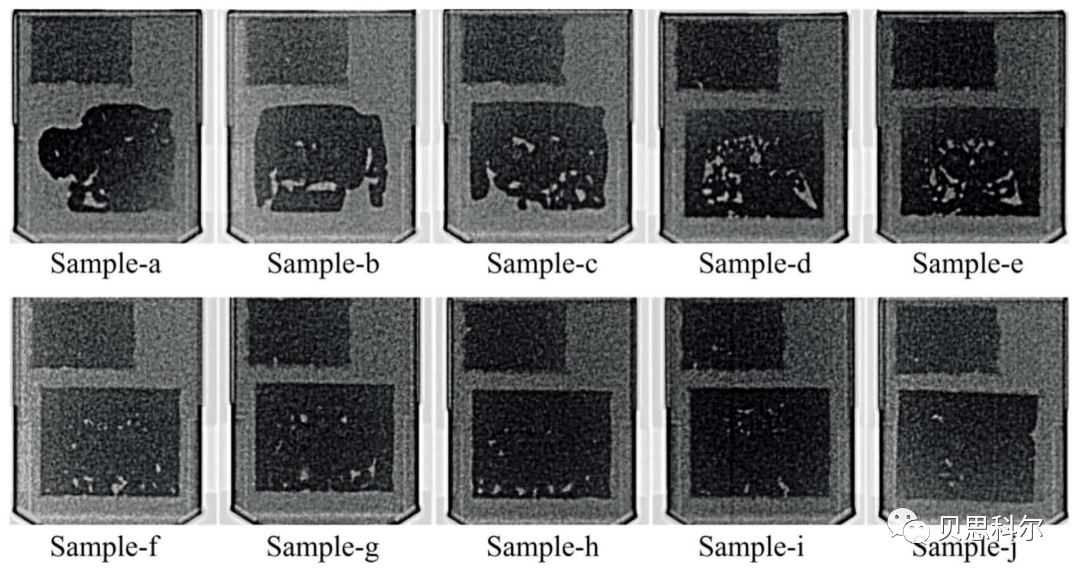

为了研究这一点,安森美半导体选择了一种绝缘栅双极晶体管(IGBT),该晶体管与 TO-247 封装中的二极管共同封装。选择十个样品,这些样品在芯片贴装中具有不同的孔洞量,使用 X 射线成像检测,如图 1 所示。

图 1:样品按 IBGT 芯片贴装孔洞的降序排列。

这些样品按孔洞总量(占芯片面积的百分比)和最大孔洞的大小(通常由芯片外围的孔洞聚结引起)分类。

测量孔洞对芯片贴装热阻的影响需要一个高度灵敏的测量系统,以及能够识别芯片贴装对所测量的整体热阻贡献的方法。这意味着遵循 JEDEC JESD51-14 标准,使用瞬态双界面测量(TDIM)方法测量结壳热阻 θJC。热阻Zth测量使用西门子Simcenter POWERTESTER ™1500A 进行,它提供了必要的测量保真度,并结合 Zth 曲线的内置结构函数分析,以识别由于芯片贴装引起的部分热阻。

结构函数是热流路径的一维表示,提供有关系统中热特性空间分布的信息,将此信息显示为热量从芯片表面上的源传递到 Simcenter POWERTESTER ™ 1500A中贴装零件的冷板时累积热阻与累积热电容的图表。该方法完全符合 JEDEC JESD51-14 标准,属于非侵入式方法,因为它使用 JEDEC JESD51-1 中描述的电气测试方法在测量过程中对芯片进行电加热和检测芯片温度。

“热结构函数分析提供了一种有效且非侵入式的方法来识别封装设备各个层的物理特性。该技术补充了其他非破坏性故障分析技术,例如 X 射线和 C-SAM,这些技术可以明确识别缺陷,但是,这些技术不提供任何有关这些缺陷对零件热行为的影响信息。”

——苏杰·辛格

安森美半导体

首席可靠性工程师

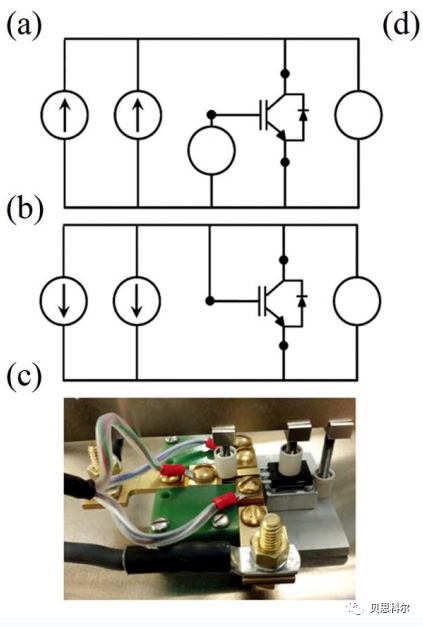

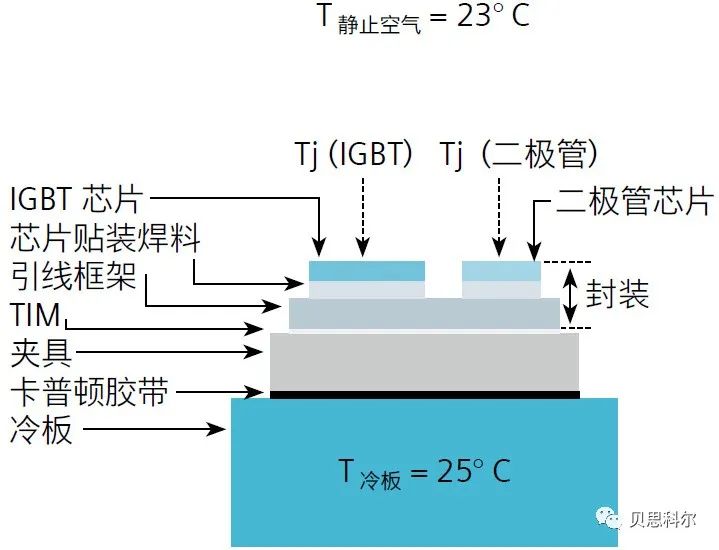

图 3:(a)和(b)分别为 θ JC(IGBT) 和 θ JC(二极管)测量电路图。(c)θ JC(IGBT)测量的实验装置。(d)显示不同层的横截面和边界条件的示意图。

图3(a)和(b)分别显示了 IGBT 和二极管结温的加热和传感电气原理图。IGBT 上的 Zth 测量是在饱和模式下完成的。图3(c)显示了 IGBT 测量的实验夹具。夹具通过 6 “/lb 的夹紧扭矩夹在冷板上,以确保良好的热传导。图3(d)显示了封装结构以及 IGBT 和二极管的物理隔离,它们都安装在引线框架上。虽然Simcenter POWERTESTER ™ 1500A 能够为单个封装提供高达 1500A 的电流,但用于测量的加热电流为 20A。所有测量均在 25° C 的冷板温度下进行,功率测试仪在测量过程中自动捕获数据。使用 Simcenter T3STER ™ Master 软件对数据进行分析。测量前几微秒内发生的电瞬变是由电源从 20A 加热电流调低到0.1A 测量电流引起的,通过内置的“平方根” 方法进行校正,该方法使用合适选定时间窗口内的拟合平方根外推的曲线代替初始/ 寄生瞬变。

使用 JESD51-14 测量 θ JC 包括进行两次测量,一次是将样品安装在冷板上,样品和冷板之间没有润滑脂,另一次是使用润滑脂。

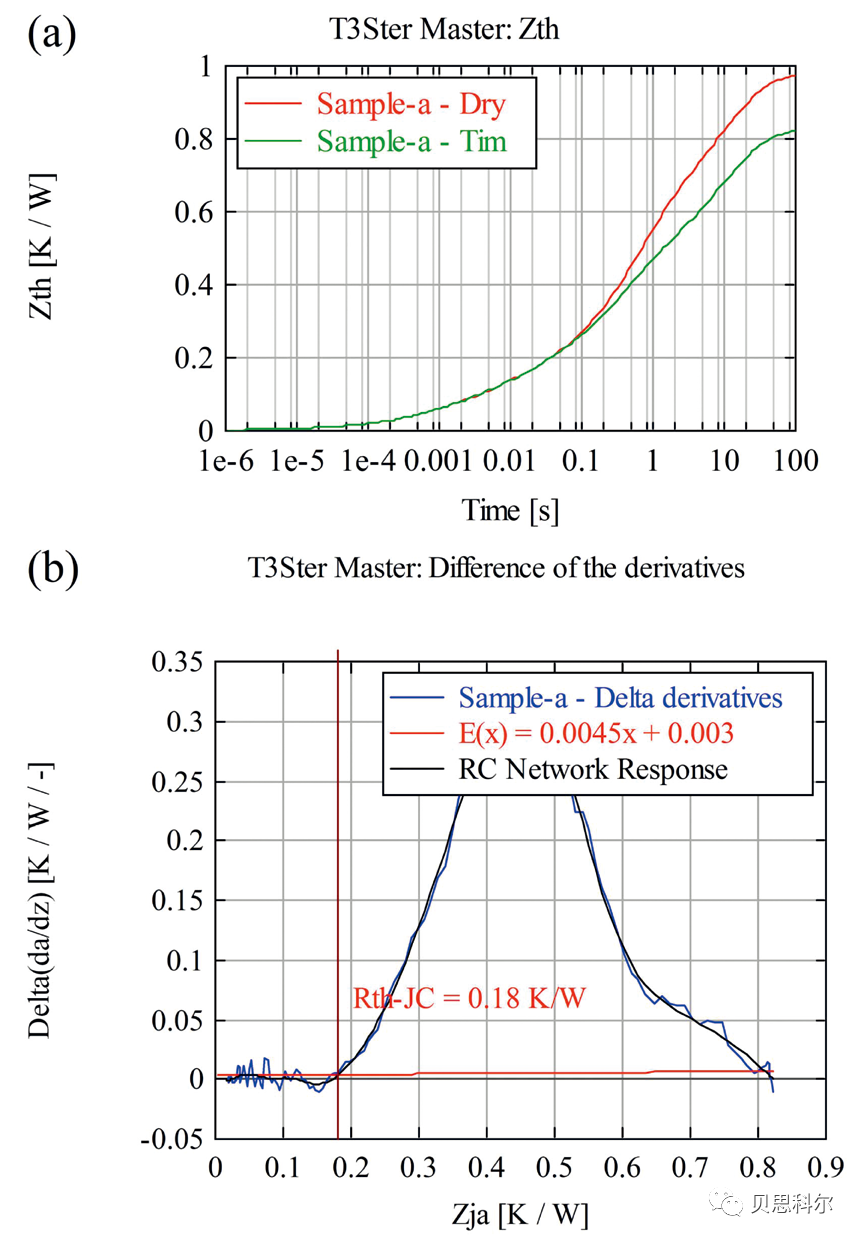

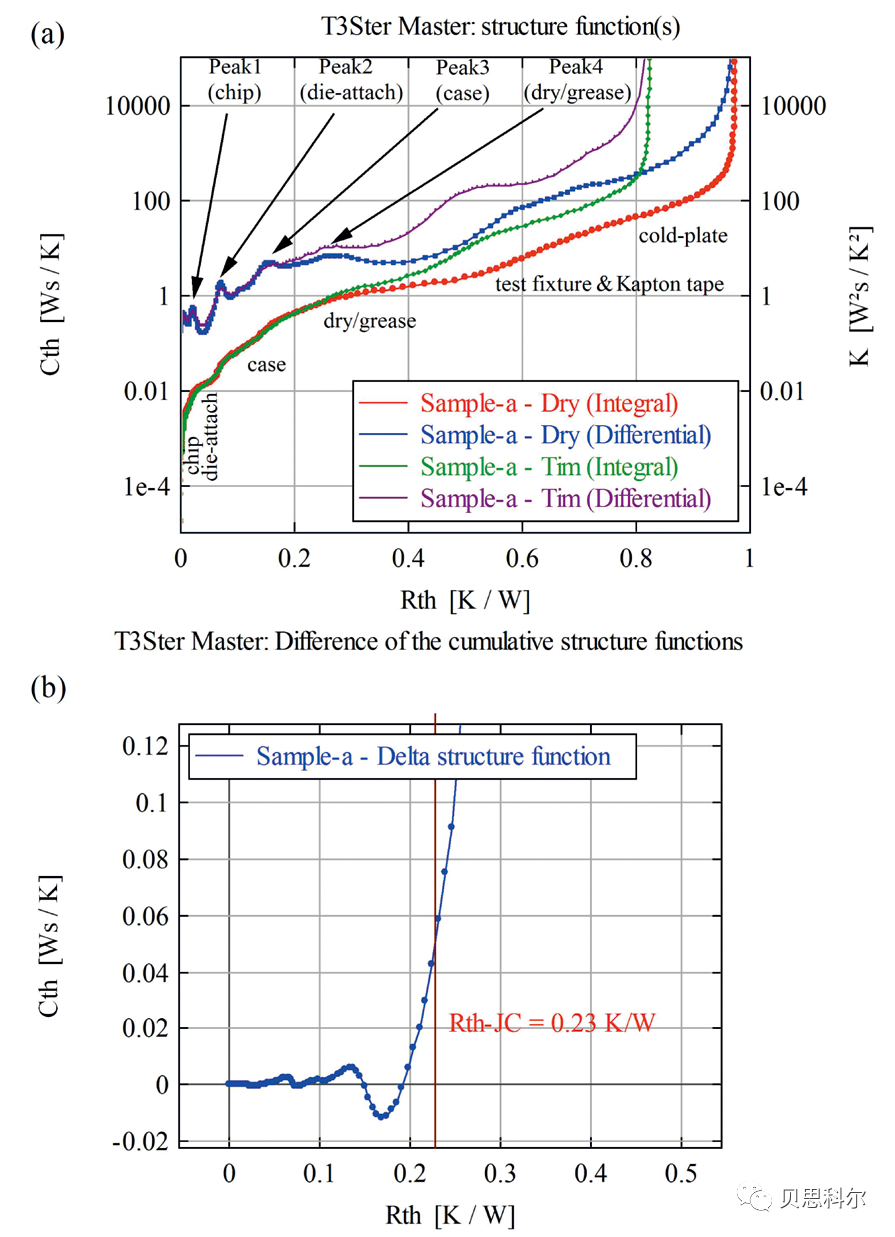

夹具和封装的微观粗糙度可抵抗干燥外壳的热流,而TIM/ 润滑脂可最大限度地减少表面粗糙度并降低界面热阻。因此,两条曲线分离是由于两次测量的热路径不同。一旦热通量到达封装- 夹具界面,即当通量离开封装外壳时,两条曲线就开始分离。两条曲线的分割点表示 θ JC。然而,两条曲线逐渐分开,而不是在一个明确的点上, 如图 4(a)所示。因此,有必要更精确地定义时间上的分离点。如果使用曲线的导数,则任务相对容易,如图 4(b)所示。图中的噪声是通过将电阻- 电容梯形图拟合到实验响应中,并通过该梯形图与瞬态开始和结束时拟合导数差值的趋势线相交的位置来解释。

图 4:(a)使用和不使用润滑脂测量的样品 a 的 Zth 曲线。(b)θ JC评估遵循样品 a 的导数增量方法。基于 RC 网络响应的拟合曲线与趋势线之间的交点的 x 值定义了 θ JC。

使用这种方法,对应于样品 a 的结壳热阻的分离点为0.18K/W。用于对样品的温度与时间响应进行后处理的Simcenter T3STER Master 软件提供了一种使用结构函数评估结壳热阻的替代方法。结构函数是总累积热电容的图形表示,作为从热源或驱动点(结点)测量的总累积热阻的函数,热量通过封装到达环境,在本例中为冷板。结构函数是通过测量的瞬态响应的数学变换来计算的,该变换涉及此处未描述的几个步骤。

图 5:(a) 样品 a 的热电容与热阻的关系,显示由于封装外壳之间界面的变化而导致的热路径差异。

对于一维热流路径,热结构函数提供有关封装器件内各层的热特性的信息。由于封装器件中的缺陷而导致的热流变化将改变结构函数。换句话说,累积热阻或累积热电容的变化对应于热流路径内热结构或材料特性的变化。例如,如果外壳和夹具之间的热界面从干接触更改为润滑脂,则这两个测量的结构函数将在相应点分离,分离点处的热阻指示结壳热阻的值,从而提供另一种测量方法。

无论使用哪种方法,清楚地确定曲线在哪一点上分离都具有挑战性。在结构函数方法的情况下,累积结构函数的差异也有一些噪声,因此同样没有曲线突然相互偏离的唯一点。虽然该方法在 JEDEC JESD51-14 标准中进行了标准化和记录,但它没有包含明确的指南来选择热电容差值以判断在该处曲线已分离。差值为曲线似乎分离时电容值的 5%。使用较低的值会导致结壳热阻变化较大。

根据 JESD51-14,低热阻封装通过结构函数差分法获得的结壳热阻常受到数值效应的阻碍;因此,在这种情况下,导数增量方法似乎更可靠,因为 TO-247 封装具有低热阻。

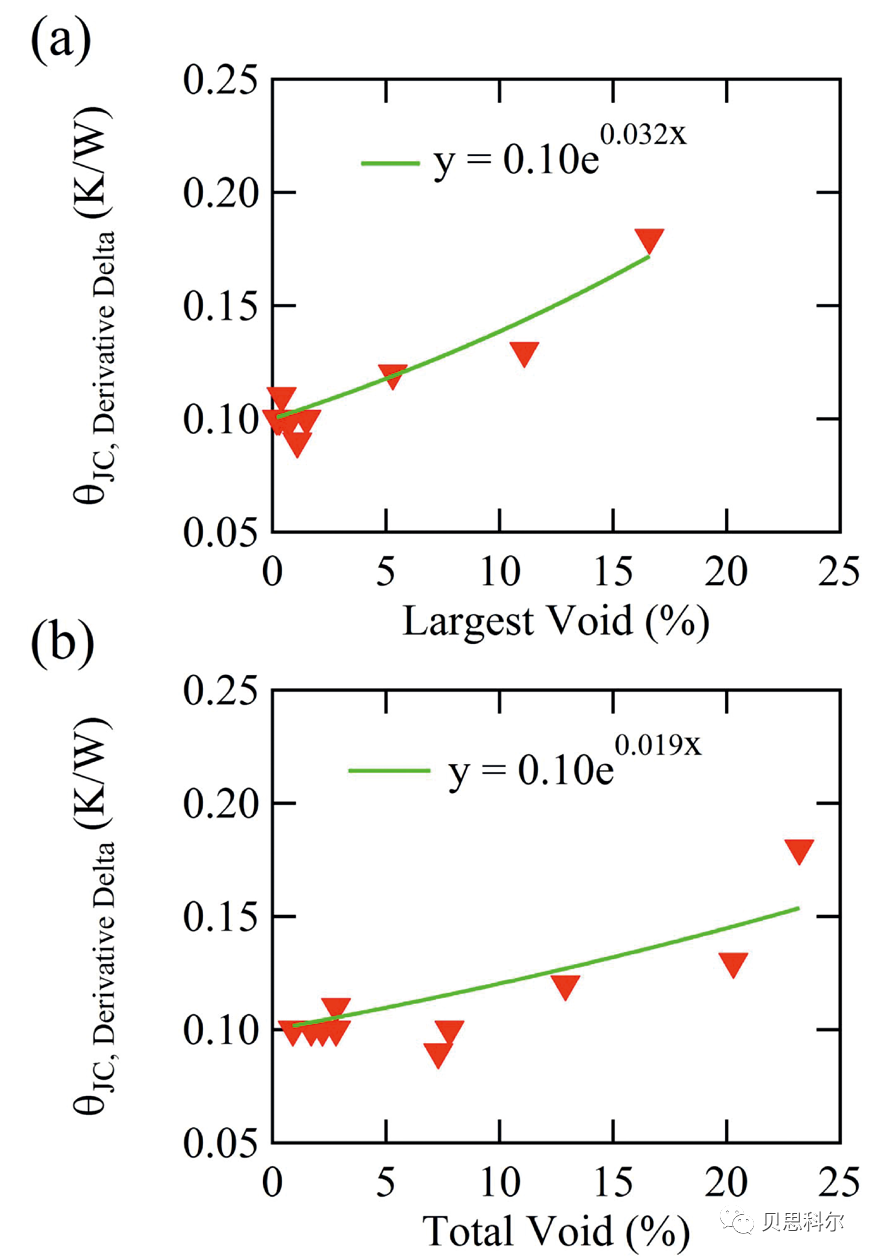

在选择了最可靠的方法来测量结壳电阻后,安森美半导体能够将注意力转向检查芯片贴装层中的孔洞对结壳电阻的影响。先前的研究发现,与分布式或随机孔洞相比,本质上是大型聚结孔洞对散热的影响更严重。为了提供高质量和高性价比的产品,必须准确了解孔洞的尺寸、位置和分布如何影响封装的热性能。

使用温度与时间导数法测量了样品 a 至样品 j 的 10 个封装,并测量了结壳电阻,结果与最大孔洞对应的面积百分比和总孔洞百分比相关。图 6 显示了该分析的结果。

从结果可以清楚地看出,在约 10% 的总孔洞面积以下,孔洞的存在不会明显增加结壳电阻。由此得出的结论是,包含在总孔洞百分比中的分布式孔洞不会显着严重影响散热。最大的孔洞尺寸(占总面积的百分比)对结壳电阻的影响更为明显。

随着最大孔洞百分比的增加,结壳热阻的行为可以用指数拟合来描述,如图6(a)所示。选择指数函数是为了评估加速度行为的性质。

图 6:(a)和(b)结壳热阻(对于 IGBT 芯片)分别占最大孔洞百分比和总孔洞百分比的函数。

很明显,孔洞水平的增加会减少热传导的有效面积,这将导致结壳电阻的增加。对于较高的孔洞水平,随着孔洞百分比的增加,阻力的变化可能是巨大的,并且很难预测确切的行为,因为它取决于这些孔洞的分布方式。封装器件的散热受到芯片贴装孔洞的严重影响,从可靠性的角度来看,最大限度地减少这些孔洞非常重要。最大的孔洞百分比对器件的热阻影响最大。对二极管结壳电阻的测量表明,这不受 IGBT 芯片贴装中的孔洞影响,这意味着二极管热路径与 IGBT 热路径无关。

审核编辑:汤梓红

-

PCB提高中高功耗应用的散热性能2018-09-12 2249

-

元器件的贴装性能2018-11-22 2395

-

半导体集成电路芯片贴装的方法有哪些?2023-01-31 4893

-

深入了解表面贴装晶体谐振器DSX1210A2024-07-25 1159

-

了解汽车D类放大器的热性能2024-09-14 360

-

探索Littelfuse WJC - A系列表面贴装高电流跳线的卓越性能2025-12-15 360

全部0条评论

快来发表一下你的评论吧 !