眨眼学会PWM

电子说

描述

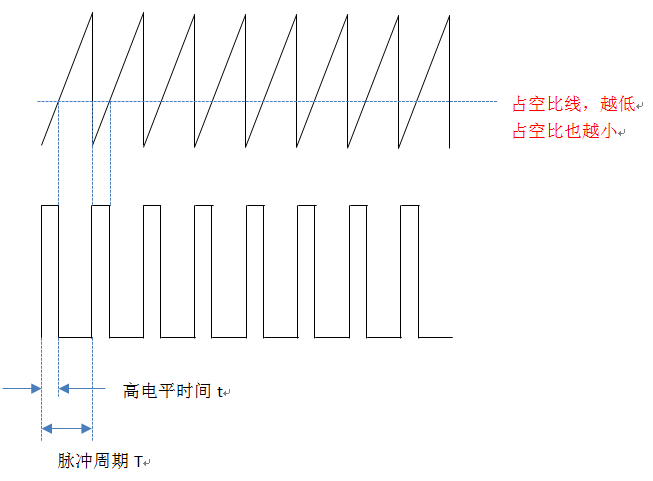

所谓PWM,就是用高电平时间和波形周期的比值代表某个数。如果这个数经过滤波后变成了接近连续的曲线表现出来那就是DA转换;如果通过这个比值表达的是控制电机的电压,那么表现出来就是电机控制。一切可以量化的东西都可以用PWM的方式去表示,这也是PWM应用广泛的原因。

产生PWM的方法:

1.产生一个计数器,满脉冲周期后翻转。

2.产生一个比较器,到达比例位置的时候输出高电平,否则输出低电平,整个过程见下图

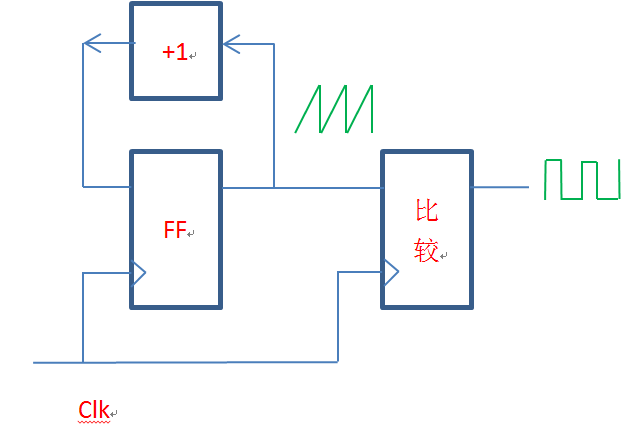

FPGA本质上是数字电路。为了生成上图的结果,所以我们需要按照上述的2步流程设计两个电路,第一个电路是计数器,第二个电路是在计数器后面的比较器,对计数器输出进行监控,一旦高于占空比对应的计数值的时候里面变为0,其余时候为1,这样就基本实现了PWM。也就对应了下面两段代码:

//计数器电路,cnt_cycle就是计数器输出计数结果 always@(posedge clk)

begin

cnt_cycle <= (cnt_cycle == (T-1)) ? 0 : cnt_cycle + 1;

end

/ 比较器电路 ,pwm_buf 为输出PWM结果,红色字为计数器输入,绿色字为比较器比较线 /

always@(posedge clk)

begin

pwm_buf <= (cnt_cycle < duty_cycle_buf) ? 1'b1 : 1'b0;

end

也就是说,以上两段代码对应的电路如下图:

针对以上电路我要作一点说明:计数器在FPGA里面的实现就是加法器和触发器组成的,加法器每次对输出+1,下一个时钟把+1的结果给到输出端,根本不是数电书上异步2分频的结果!另外再次强调,由于FPGA的设计收到实际因素的限制,数电书上某些理模型是难以在实际中大量应用的,所以FPGA内部很多结构和综合结果都与数电书上有差异,但是数字电路的基本原理是没有任何改变的!

PWM还差最后一点,因为输入占空比可以不断改变,也就是第一张图的比较线是会上下移动的,为了不影响我们在计数的过程中突然采集到突变的值最终导致,不平滑的占空比,所以占空比输入在每个计数周期完成后才会去采集。也就是大家看到的这句:

always@(posedge clk)

begin

if(cnt_cycle == (T-1)) duty_cycle_buf <= (duty_cycle > T-1) ? T-1 : duty_cycle;

end

只有在cnt_cycle计数一个周期T的时候,占空比值才会更新,也就是比较线才会移动!

-

jf_39050252

2023-06-28

0 回复 举报师学习之用,如有内 收起回复

jf_39050252

2023-06-28

0 回复 举报师学习之用,如有内 收起回复

-

PWM应用橙群微电子 2023-03-09

-

眨眼拍照的眼部传感器哪家有做?2016-05-14 2001

-

PWM怎么样才能学会啊,求帮忙2016-12-29 3643

-

眨眨眼睛,开关电器——新型传感器研制出来了!2017-08-07 2272

-

Xilinx XUPV5LX110T错误导致眨眼没有停止正常吗?2019-08-21 1664

-

PWM的异常行为2019-09-27 1345

-

pwm程序停止调用回调函数2020-03-05 2351

-

PWM怎么样学习2020-07-08 1265

-

会眨眼的电子猫电路图2009-05-21 2080

-

声控眨眼玩具电路图2009-07-29 1425

-

基于Adaboost算法的驾驶员眨眼识别2009-11-09 1361

-

会眨眼的小猫咪电路图2009-11-18 1431

-

免动手摄影 眨眼时便按下快门2018-04-17 1431

-

如何快速学会PLC编程2019-09-07 11174

-

儿童乐高Arduino教程之眨眼草图2023-07-10 443

全部0条评论

快来发表一下你的评论吧 !