NOR FLASH和NAND FLASH基本结构和特点介绍

存储技术

描述

非易失性存储元件有很多种,如EPROM、EEPROM、NOR FLASH和NAND FLASH,前两者已经基本被淘汰了,因此我仅关注后两者,本文对FLASH的基本存储单元结构、写操作、擦除操作和读操作的技术进行了简单介绍,对了NOR和NAND由存储结构决定的特性和应用场合的差异,对后续的硬件设计和驱动编程起到铺垫作用。

1 FLASH基本存储单元---浮栅场效应管

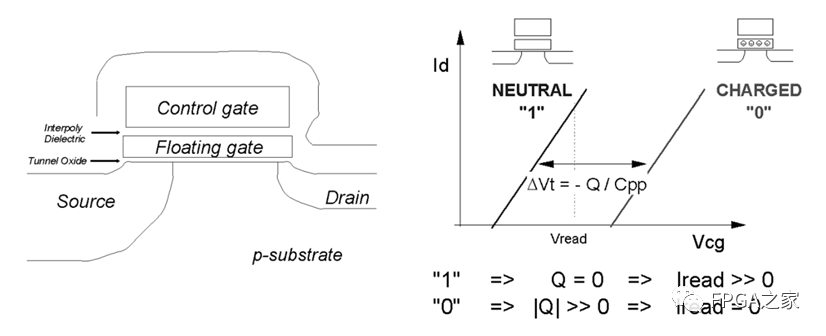

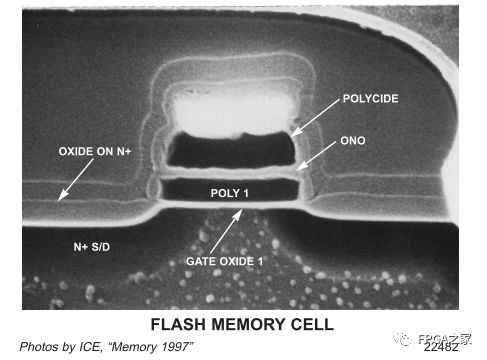

NOR FLASH和NAND FLASH都是使用浮栅场效应管(Floating Gate FET)作为基本存储单元来存储数据的,浮栅场效应管共有4个端电极,分别是为源极(Source)、漏极(Drain)、控制栅极(Control Gate)和浮置栅极(Floating Gate),前3个端电极的作用于普通MOSFET是一样的,区别仅在于浮栅,FLASH就是利用浮栅是否存储电荷来表征数字0’和‘1’的,当向浮栅注入电荷后,D和S之间存在导电沟道,从D极读到‘0’;当浮栅中没有电荷时,D和S间没有导电沟道,从D极读到‘1’,原理示意图见图1.1[1],图1.2是一个实际浮栅场效应管的剖面图。

注:SLC可以简单认为是利用浮栅是否存储电荷来表征数字0’和‘1’的,MLC则是要利用浮栅中电荷的多少来表征‘00’,‘01’,‘10’和‘11’的,TLC与MLC相同。

2 FLASH基本存储单元的操作---写/擦除/读

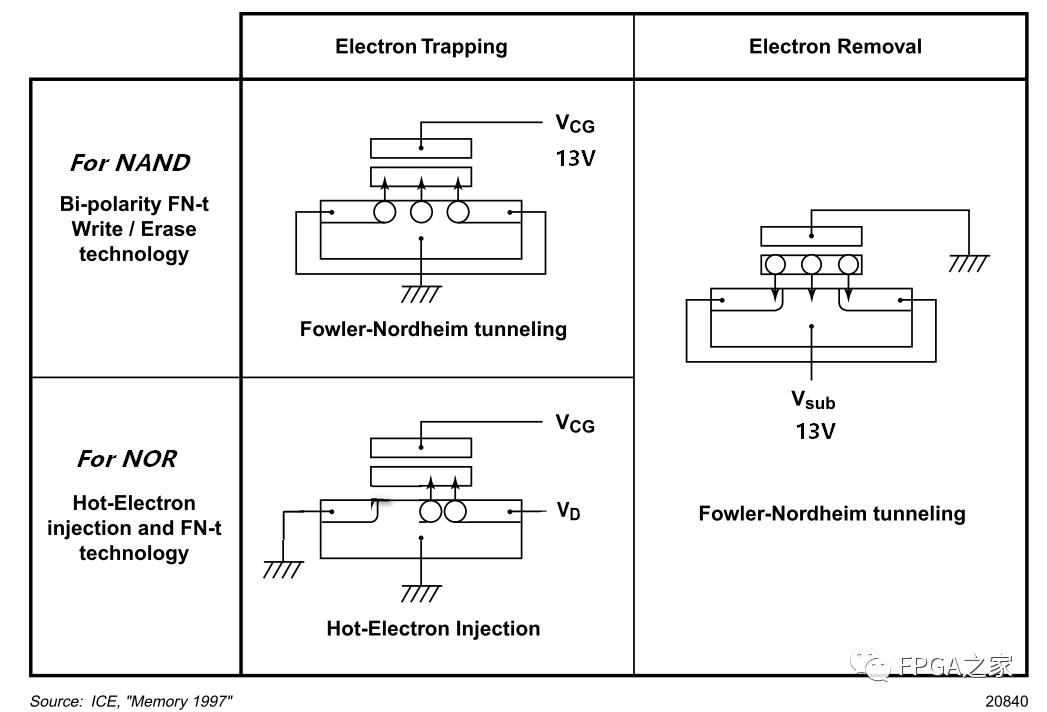

FLASH中,常用的向浮栅注入电荷的技术有两种---热电子注入(hot electron injection)和F-N隧道效应(Fowler Nordheim tunneling);从浮栅中挪走电荷的技术通常使用F-N隧道效应(Fowler Nordheim tunneling),基本原理见图2[2]。

写操作就是向浮栅注入电荷的过程,NOR FLASH通过热电子注入方式向浮栅注入电荷(这种方法的电荷注入效率较低,因此NOR FLASH的写速率较低),NAND FLASH则通过F-N隧道效应向浮栅注入电荷。FLASH在写操作之前,必须先将原来的数据擦除(即将浮栅中的电荷挪走),也即FLASH擦除后读出的都是‘1’。

擦除操作就是从浮栅中挪走电荷的过程,NOR FLASH和NAND FLASH都是通过F-N隧道效应将浮栅中的电荷挪走的。

读出操作时,控制栅极上施加的电压很小,不会改变浮栅中的电荷量,即读出操作不会改变FLASH中原有的数据,也即浮栅有电荷时,D和S间存在导电沟道,从D极读到‘0’;当浮栅中没有电荷时,D和S间没有导电沟道,从D极读到‘1’。

3 NOR FLASH 和NAND FLASH的结构和特性

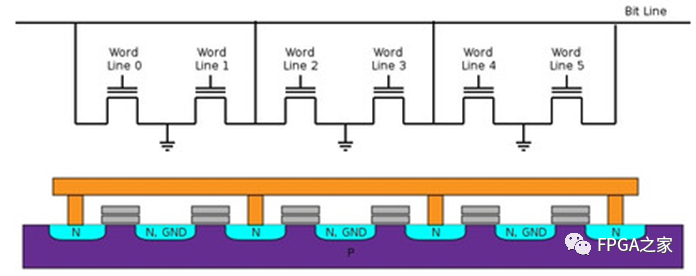

3.1 NOR FLASH的结构和特性

NOR FLASH的结构原理图见图3.1,可见每个Bit Line下的基本存储单元是并联的,当某个Word Line被选中后,就可以实现对该Word的读取,也就是可以实现位读取(即Random Access),且具有较高的读取速率,图3.1是一个3*8bit的NOR FLASH的原理结构图,图3.2是沿Bit Line切面的剖面图,展示了NOR FLASH的硅切面示意图,这种并联结构决定了NOR FLASH的很多特性。

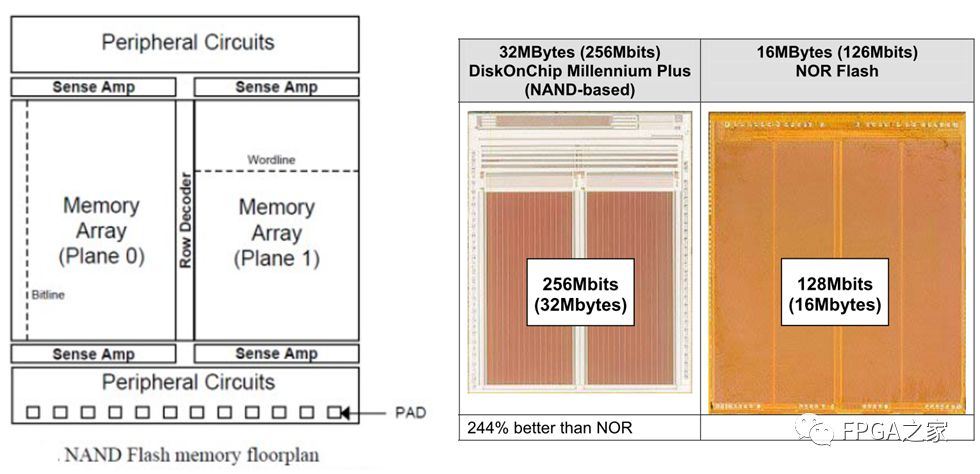

(1)基本存储单元的并联结构决定了金属导线占用很大的面积,因此NOR FLASH的存储密度较低,无法适用于需要大容量存储的应用场合,即适用于code-storage,不适用于data-storage,见图3.3[3]。

(2)基本存储单元的并联结构决定了NOR FLASH具有存储单元可独立寻址且读取效率高的特性,因此适用于code-storage,且程序可以直接在NOR 中运行(即具有RAM的特性)。

(3)NOR FLASH写入采用了热电子注入方式,效率较低,因此NOR写入速率较低,不适用于频繁擦除/写入场合。

最后来个小贴士:NOR FLASH的中的N是NOT,含义是Floating Gate中有电荷时,读出‘0’,无电荷时读出‘1’,是一种‘非’的逻辑;OR的含义是同一个Bit Line下的各个基本存储单元是并联的,是一种‘或’的逻辑,这就是NOR 的由来。

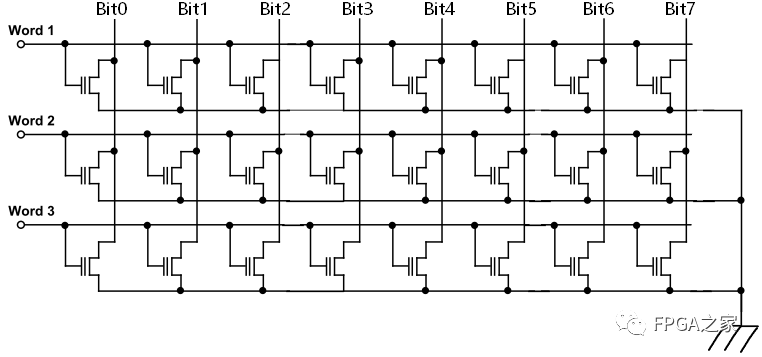

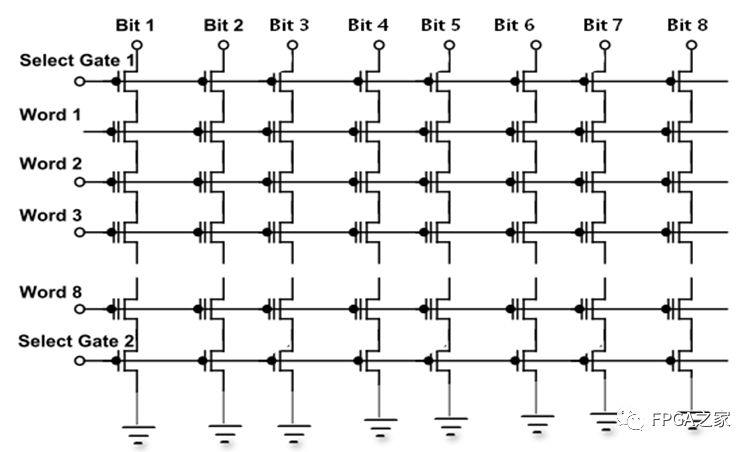

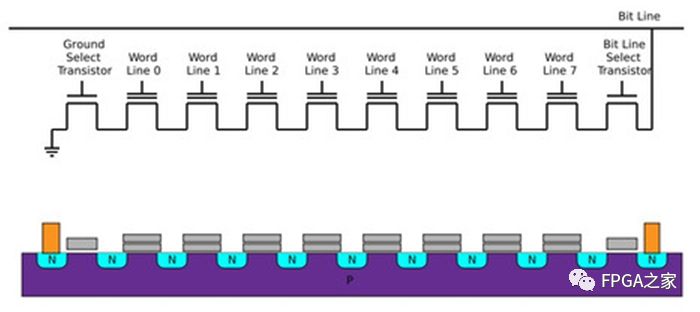

3.2 NAND FLASH的结构和特性

NAND FLASH的结构原理图见图3.4,可见每个Bit Line下的基本存储单元是串联的,NAND读取数据的单位是Page,当需要读取某个Page时,FLASH 控制器就不在这个Page的Word Line施加电压,而对其他所有Page的Word Line施加电压(电压值不能改变Floating Gate中电荷数量),让这些Page的所有基本存储单元的D和S导通,而我们要读取的Page的基本存储单元的D和S的导通/关断状态则取决于Floating Gate是否有电荷,有电荷时,Bit Line读出‘0’,无电荷Bit Line读出‘1’,实现了Page数据的读出,可见NAND无法实现位读取(即Random Access),程序代码也就无法在NAND上运行。

图3.4是一个8*8bit的NAND FLASH的原理结构图,图3.5是沿Bit Line切面的剖面图,展示了NAND FLASH的硅切面示意图,NAND FLASH的串联结构决定了其很多特点.

(1)基本存储单元的串联结构减少了金属导线占用的面积,Die的利用率很高,因此NAND FLASH存储密度高,适用于需要大容量存储的应用场合,即适用于data-storage,见图3.3[3]。

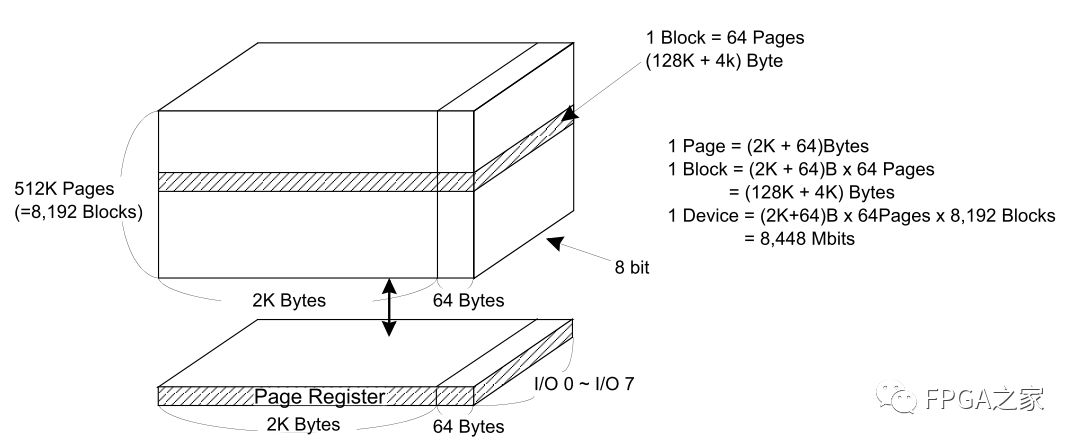

(2)基本存储单元的串联结构决定了NAND FLASH无法进行位读取,也就无法实现存储单元的独立寻址,因此程序不可以直接在NAND 中运行,因此NAND是以Page为读取单位和写入单位,以Block为擦除单位,见图3.6。

(3)NAND FLASH写入采用F-N隧道效应方式,效率较高,因此NAND擦除/写入速率很高,适用于频繁擦除/写入场合。同时NAND是以Page为单位进行读取的,因此读取速率也不算低(稍低于NOR)。

最后来个小贴士:NAND FLASH的中的N是NOT,含义是Floating Gate中有电荷时,读出‘0’,无电荷时读出‘1’,是一种‘非’的逻辑;AND的含义是同一个Bit Line下的各个基本存储单元是串联的,是一种‘与’的逻辑,这就是NAND 的由来。

3.3 NOR 和NAND的比对

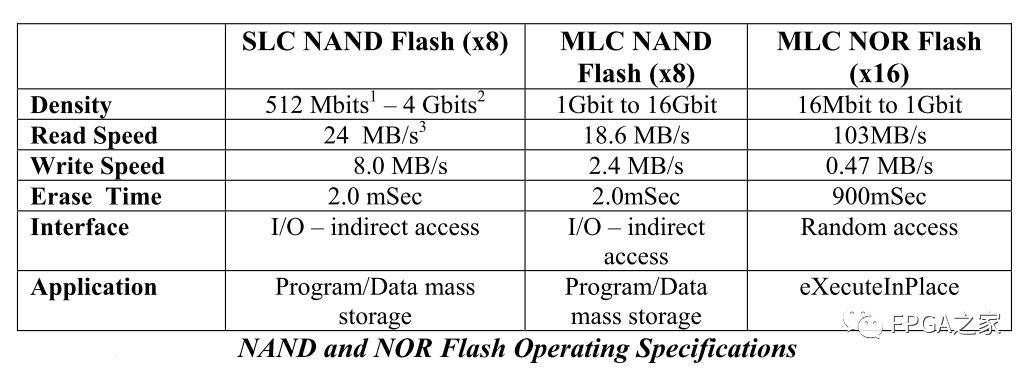

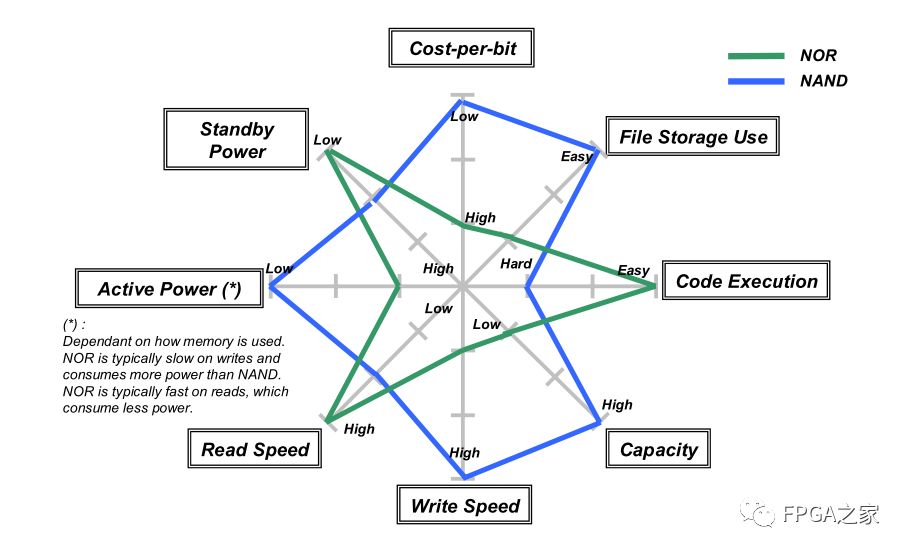

通过3.1和3.2节对NOR和NAND结构和特点的解析,我们可以得出图3.7[5]和图3.8[5]中的结论,更详细的比对请见参考文献[3]

审核编辑:刘清

-

张鹏420

2024-08-25

0 回复 举报111 收起回复

张鹏420

2024-08-25

0 回复 举报111 收起回复

- 相关推荐

- 热点推荐

- 场效应管

- EPROM

- Nand flash

- slc

- NOR flash

-

NAND Flash和NOR Flash的差别2023-09-11 12082

-

NOR Flash的技术体系和结构特点2023-09-22 9421

-

NAND FLASH与NOR FLASH的技术对比2023-10-01 3732

-

nand nor flash区别2008-06-30 1613

-

浅谈EEPROM和flash的区别 及 nor flash和nand flash2018-10-07 25567

-

非易失性存储器-Nor Flash的特点都有哪些2020-12-07 4605

-

NOR falsh、NAND flash、SDEMMC、QSPI flash、SPI flash2021-12-02 2394

-

NOR Flash和NAND FLASH的区别是什么2022-01-25 62742

-

一文了解SPI NAND Flash和SPI NOR Flash的区别2023-03-06 9870

-

为什么Nor Flash可以实现XIP,而Nand flash就不行呢?2023-10-29 2494

-

NAND Flash和NOR Flash的区别2023-11-30 4446

-

NAND Flash和NOR Flash哪个更好2024-07-29 3764

-

从NOR Flash 到 NAND Flash 和SD NAND,从底层结构到应用差异2026-03-05 374

-

NOR Flash和NAND flash有什么区别2026-03-11 503

-

NOR FLASH和NAND FLASH的对比2026-03-31 429

全部0条评论

快来发表一下你的评论吧 !