缓启动电路的工作原理、实例分析与应用

描述

01缓启动电路的工作原理

通信产品一般采用分散供电方式,各单板上采用DC/DC模块将-48V电源转换为其所需的5V、3.3V、2.5V等子电源。由于输入电压高,电源电路中又存在用于滤波和防止DIP的大电容,在单板插入上电时,会对-48V电源造成冲击,瞬时大电流将造成-48V电源电压出现跌落,可能影响到其它单板的正常工作;同时,由于瞬时大电流的原因,单板插入时在接插件上会产生明显的打火现象,这会引起电磁干扰,并对接插件造成腐蚀。为了避免上述现象,-48V电源供电单板需要“缓慢”上电。

一、缓启动电路的作用

通信设备产品单板上几乎都在电源模块的输入端设计有缓启动电路,缓启动电路的功能主要有两个:

1、延迟单板电源的上电时间:我们的单板一般都要求支持热拔插,当单板插入子架时,单板插头和母板插针的接触是不稳定的,为了避免这种抖动的影响,可以在电源模块和母板电源之间加一个电路,使母板的电源延迟一段时间以后再加到电源模块。

2、减小上电的冲击电流:由于单板电源都接有滤波电容,电源上电瞬间跳变时由于电容的充电,会产生较大的冲击电流,造成母板电源电压抖动,跌落,以及强烈的电磁辐射,很容易对其他工作中的单板造成不良影响,如果能把电源的上电速度变缓一些,就能有效的减小这种影响。

二、缓启动电路的工作原理

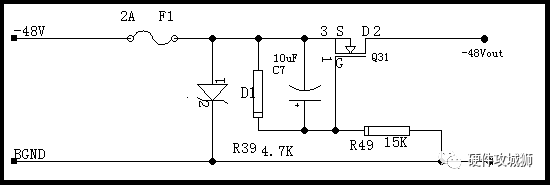

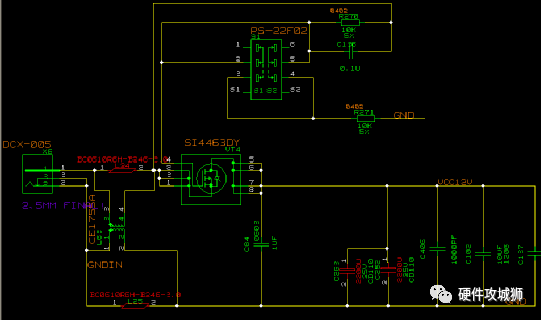

电路的原理图:

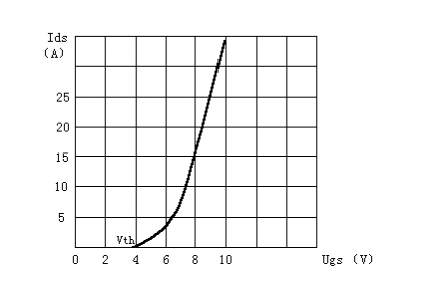

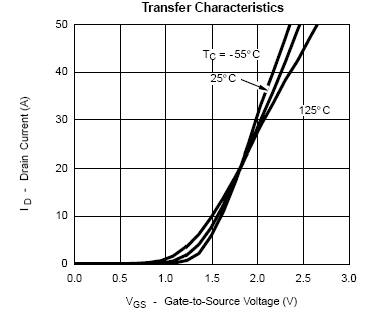

缓启动电路由R39,R49,C7和Q31组成,Q31是绝缘栅型场效应管,也是缓启动电路最关键的器件。为了理解缓启动的原理,首先我们来回顾一下MOS管的一点基础知识。下图大致描述了典型的MOS管的转移特性:

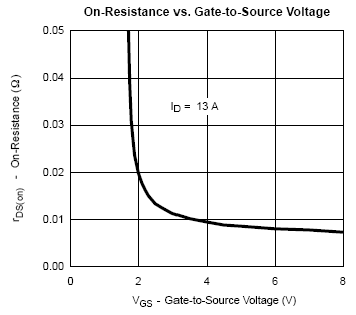

MOS管的特性表明,当Vgs小于一定电压(Vth)时,DS极之间的电阻Rds是很大的,可以认为开路,电流不能通过;当Vgs达到Vth时,MOS管开始导通,Rds随Vgs的增加迅速减小。当Vgs达到一定的程度,Rds很小,可以认为DS之间是近似短路的。Vth可以称之为开启电压(Voltage-Gate threshold),一般为2-4V。

在的缓启动电路中,电阻R39,R49和C7构成了分压式RC时间常数电路,C7并联在Q31的GS极之间,也就是Vc7=Vgs。当48V电源刚加到单板时,C7未充电,Vgs=0,MOS不导通,电源模块不供电。随后,48V通过R39,R49向C7充电,当C7的电压达到Vth时,MOS开始导通,这一阶段,完成的是延时上电的作用,延迟时间可由下式估算:

Uin(R39/(R39+R49))(1-e-T/ )=Vth

其中,T为延迟时间, Uin=48V,为RC电路的时间常数,=C7(R39//R49),Vth一般取4V。将原理图中数值代入计算可知,延迟时间T约等于15.3ms。

MOS管开始导通后,Vgs继续增加(直到12V左右),Rds迅速减小,缓启动的输出电压逐渐升高直到到与输入电压基本一致。电源模块开始工作,单板正式上电。在这一过程中,输出电压并不是瞬间跳变到最高的,因此,大大减轻了冲击电流的干扰。这一过程的时间与C7的充电速度,MOS的特性,负载特性都有关系,难以具体计算,具体还需实测调整。

三、实测波形分析

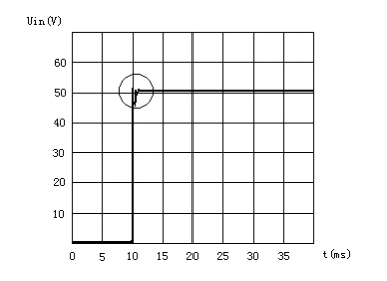

下图是缓启动的输入电压上电波形

这是缓启动输入端在电源开关闭合瞬间的波形,可以看到画圆圈处的抖动,持续时间约1ms,如果是热拔插,这个抖动的幅度和持续时间都将可能更大。

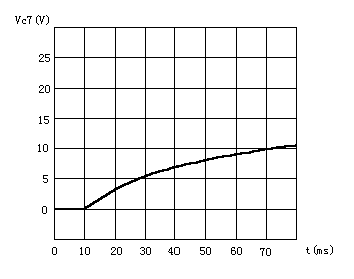

下图是缓启动的C7电压上升波形

可以看到,上电15ms后,C7电源上升到约4V,与理论计算值基本一致。

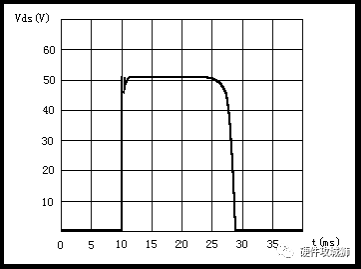

下图是缓启动MOS管的D,S间电压波形。

可以看到,在开关闭合后的14ms以内,输入电压完全加在MOS的DS两端,这与理论计算值基本一致(由于MOS管的Vth并不一定是4V,有些误差是很正常的),从14ms开始,Vds以指数方式下降,过程时间约4ms。

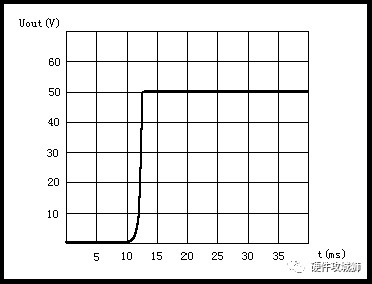

下图是缓启动输出的电压波形。

可以看到,对比缓启动的输入电压上电波形,缓启动的输出电压不再有开关闭合时的抖动,而且上电边沿也非常明显,过程约4ms,实现了减小上电冲击的目的。

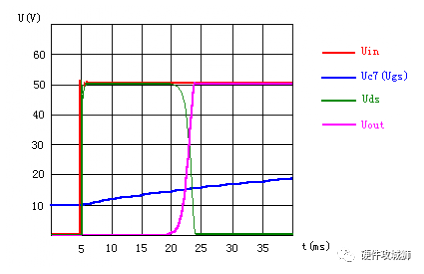

让我们再把所有的波形放在同一时间轴上来比较一下,如下:

可以看到,经过缓启动电路之后,单板实际供电电压Uout比输入电压Uin总共延时了将近20ms,不但消除了上电抖动,而且有效减小了冲击。

四、总结

1、缓启动的时间常数电路必须确保电容充电完成后其电压不能大于15V,因为一般大功率MOS管的G,S间击穿电压在20V左右,电压过高,会损坏MOS管(现在很多单板上在电容两端并联了一个稳压管就是起这个作用的),但是也不应该低于10V,因为一般大功率MOS管的D,S间电阻Rds都需要Vgs达到10V后才达到最小值(一般在0.1ohm量级)。

2、缓启动的延迟时间不能太长,原因有二。其一,延迟太长,热拔插时,单板接口信号线已连接,而电源仍未上电,会造成接口器件闩锁损坏;其二,缓启动关键器件MOS管在从截止到导通转换的过程中瞬间功耗是非常大的,如果电容充电过于缓慢,造成边沿时间太长,MOS管将因为功耗过大而损坏。延时一般取几十毫秒。

02缓启动电路实例分析与应用

根据某产品单板电路测试过程的浪涌电流冲击问题,详细分析了MOS管缓启动电路的RC参数,通过分析和实际对电路参数的更改,使电路的浪涌电流冲击满足板上电源要求。

一、问题的提出

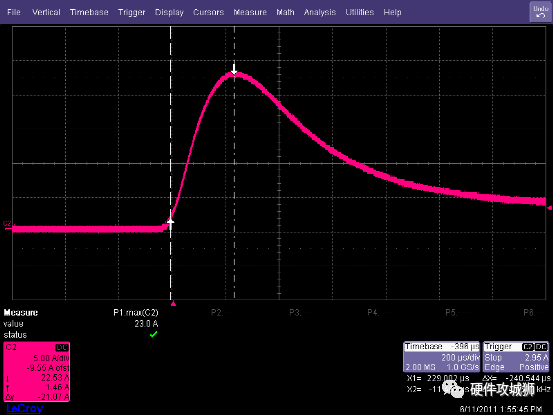

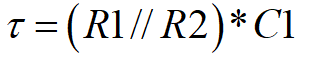

某通信产品电路测试时发现浪涌电流冲击过大,可能会损坏保险丝或MOS管等器件,而且有的即使没有损坏也有可能会影响其使用寿命(图1)。

根据某产品单板电路测试过程的浪涌电流冲击问题,详细分析了MOS管缓启动电路的RC参数,通过分析和实际对电路参数的更改,使电路的浪涌电流冲击满足板上电源要求。

图1改前测试冲击电流

从上图可以看出冲击电流很大,达23.0A,远大于满载工作电流(1A左右),板上电源设计指南要求是满载工作电流的3~5倍,所以需要整改以达到板上电源要求,电路原理图如图2所示。

图2原电路原理图

二、解决思路

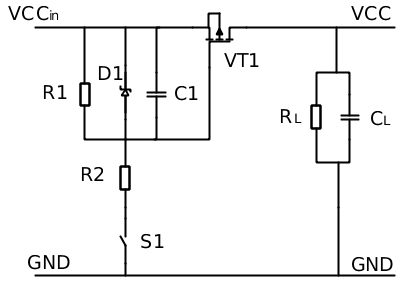

将原电路原理图(图2)等效为图3。

图3原理图等效[注1]

注1:R270等效为R1,R271等效为R2,C136等效为C1,MOS管为VT1,全部负载等效为RL,全部电容等效为CL,D1在计算中用不到。

根据MOS管开启电压和RDS的特性曲线(图4)可知,控制了MOS管VGS电压线性度就能精确控制冲击电流。所以图3中外接电容C1、R1和R2被用来作为积分器对MOS管的开关特性进行精确控制,达到控制上电冲击电流的目的。

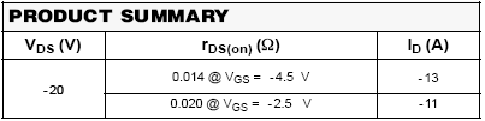

图4本文原理图中MOS管(Si4463DY)VGS(th)与电流ID和电阻RDS的关系

原电路就是利用这个原理进行上电控制的,但是参数设置有问题,所以才出现了图1中的较大冲击电流。

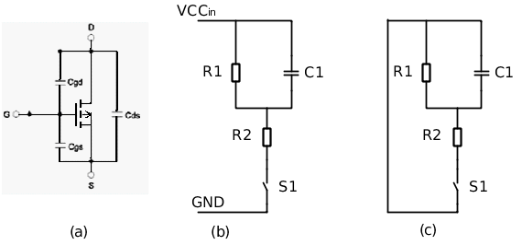

现将简化电路原理图(图3)VT1前面的上电控制电路等效为图5进行计算。

图5简化VT1前面的上电控制电路

1、上电时间计算

1)时间参数τ。

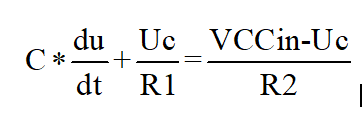

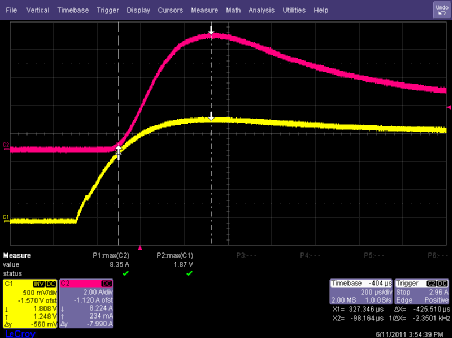

由于图5(a)中MOS管内部电容Cgs<

2)计算电容上电时间。

根据图5(b)得:

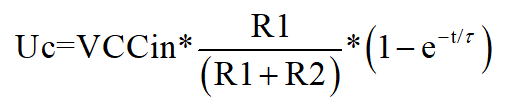

最后计算得出:

所以Uc的上电完成时间只与τ相关,但是上电的斜率将同时与R1/(R1+R2)和τ相关,下面用两个实验予以说明。

2、实验验证

实验(1):更改时间参数τ(更改C1)控制VGS开启速度

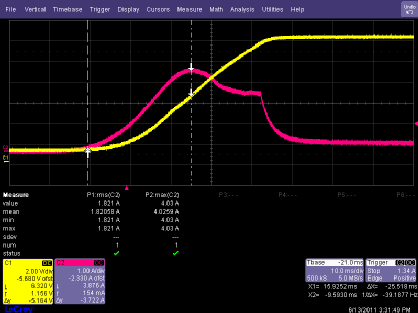

图6R1=R2=10Kohm,C1=2.2uF时上电电流波形

根据计算τ=(R1//R2)*C1=11mS,从图6可以看出上电时间变大了,为3.6mS,冲击电源也由原来的23.0A变为现在的9.26A。说明一定程度上控制了其上电时间和冲击电流。

但是,τ变为原来的22倍,电流冲击时间变为原来的15倍,冲击电流只变为原来的40%,不能完全够达到精确控制的目的。

实验(2):设置Uc电压以达到控制上电时间的目的

根据MOS管开启电压的特性曲线图4,可以看出:1V~2.5V这段为MOS管开启的过程,精确控制这段电压的上升过程(斜率)将可以有效控制上电冲击电流的大小。

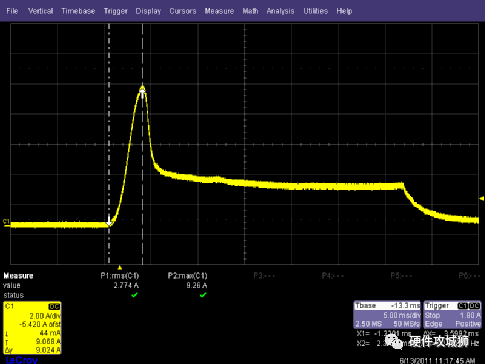

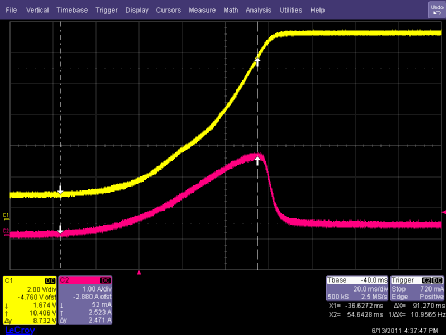

更改电阻R1=2.7K,R2=10K和C1=0.1uF不变时上电电流波形如图7所示。

图7R1=2.7K,R2=10Kohm,C1=0.1uF时上电电流波形

(红色曲线为上电电流波形,黄色为Uc两端电压波形)

根据计算τ=(R1//R2)*C1=0.2mS,变小了,但是从图7可以看出上电时间却变大了,为425uS,冲击电源也由原来的23.0A变为现在的8.35A。

对比两个实验可以发现:改变R1,τ变小了,但电流上电时间却变大了,而且电流冲击时间在只变大1.8倍的情况下,冲击电流的幅度却变为原来的36%;而改变τ(即改变C1),在电流冲击上升时间变为原来的15倍时,电流幅度才变为原来的40%,所以改变R1对MOS管VGS的精确控制效果明显。

3、原因分析

电容归一化上电波形如图8所示:

图8归一化电容上电波形

从图8可以看出:原电路中Uc两端最终电压在1τ(图8中红色曲线部分)内将从0V上升到Uc*0.632=3.8V,而从3.8V上升到6V需要至少4τ(1τ~5τ)。而电路中MOS管开启电压是1V~2.5V,这段电压在小于0.5τ时间内就完成了,所以可以得出其上电时间(1~2.5V的时间)应小于0.5τ,即小于250uS,根据图1可以看出,冲击电流的时间约为240uS左右,与计算基本吻合。

实验(1)电路中Uc最终两端电压与原电路相同为6V,不过τ变为原来的22倍为11mS,MOS管开启电压在1V~2.5V段上升时间也应该小于0.5τ,实测试为3.6mS,小于0.5τ(5.5mS)也基本与理论计算吻合

实验(2)电路中Uc最终两端约为2.5V。开启电压的时间段处于了约1τ~3τ之间后,虽然τ变小了,但电流上电冲击时间,实测试为1.8倍[注2],基本与理论吻合。

(注2:原电路用约0.5τ完成电流冲击,实验二电路用约2τ,原电路τ=500uS,而实验二τ(R1=2.5K)=200uS,基本上实验二的2τ(R1=2.5K)为原电路0.5τ的2倍,所以实测1.8倍基本与理论符合。)

经过上面的讨论,可以看出:对MOS管的控制有两种方法:

(1)设置Uc两端最终电压,控制VGS电压上升的斜率。

(2)更改时间参数τ控制VGS开启速度(也在一定程度上控制斜率)。

当然可以结合两种方法,同时进行控制,以达到控制冲击电流的目的。

三、实践情况

结合到上两个实验及分析,用两种方法控制,将参数更改为R1=27K,R2=100K,C1=2.2uF,测试上电冲击电流波形如图9所示。

图9R1=27K,R2=100K,C1=2.2uF,测试上电冲击电流波形

(红色为冲击电流波形,黄色为负载电压波形)

最大冲击电流为4.03A,基本满足板上电源设计要求(冲击电流为3~5A)。不过电流上电时间变为25.5mS,如需要再次降低冲击电流,可以继续加大电容。比如图10。

当电容增加到10uF时(R1=27K,R2=100K)时的电流上电波形。

图10R1=27K,R2=100K,C1=10uF,测试上电冲击电流波形

图10中电流上电波形变为90mS。从上面的介绍可以看出“通过设置Uc两端最终电压”和“更改时间参数τ控制VGS开启速度”基本上达到了控制上电冲击电流的目的,至于如何选择合适的参数,需要根据具体情况进行分析。

四、效果评价

可以用示波器对I2T进行的计算,(标称2A适配器测试)如图15、16、17所示。

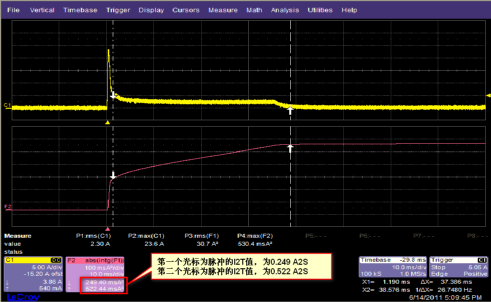

图11 原电路R1=R2=10K,C1=0.1uF时冲击电流I2T计算

图15可以认为是原电路中MOS管基本没有控制,上电瞬间适配器作为恒压源产生了“冲击”,经过示波器精确计算,在“冲击”脉冲结束时(第一个光标处)值为0.249 A2S,在正常工作前(第二个光标处值为0.522 A2S)。

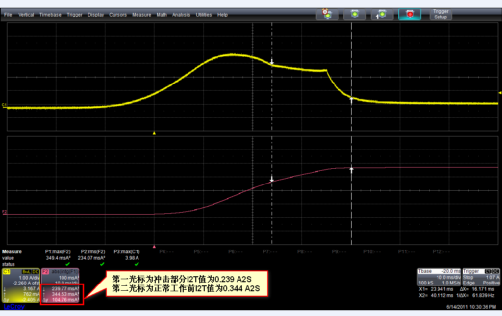

图12 更改电路参数R1=27K,R2=100K,C1=2.2uF时冲击电流I2T计算

更改电路参数后,MOS管有一定的控制作作,但是还是产生了一个“台阶”(第一光标与第二光标之间)经过示波精确计算,在脉冲结束时(第一个光标处)值为0.239 A2S,在正常工作前(第二个光标处值为0.344 A2S)。

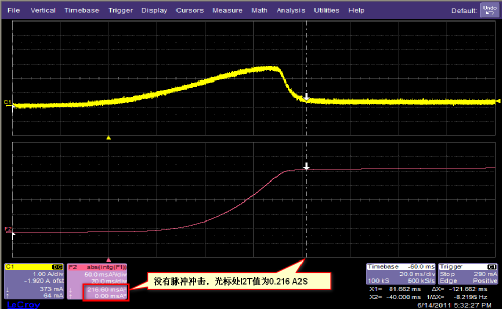

图13 R1=27K,R2=100K,C1=10uF,测试上电冲击电流波形

由于对MOS管的上电控制已经接近或小于了适配器的电流提供能力,所以基本已经没了“冲击”电流(可以认为完全是MOS管控制下的电流),经过计算,在正常工作前的I2T值为0.216 A2S(第二个光标处)。

注意:τ也不能过大,过大时引起上电波形过缓,导致板内器件上电时序问题,同时过于缓慢的上电波形可能还会“损伤”或引起MOS管烧毁。

通过以上三个图对比:MOS管的控制能力越强,“冲击”电流越小,I2T值也越小,对保险丝等器件的“损伤”也越小。

五、总结

通过以上的分析和实际测试基本上达到了控制VGS电压上升的斜率的目的,有效降低了脉冲“冲击”电流对保险丝管的影响。所以可以结合如下两种方法,同时进行控制,以达到控制冲击电流的目的。

1、设置Uc两端最终电压,控制VGS电压上升的斜率。

2、更改时间参数τ控制VGS开启速度(也在一定程度上控制斜率)。

在电路设计中有几点需要特别关注。

1、Uc两端的最终电压一定要保证VGS完全开启和该电压下MOS管体电阻基本达到最小。

2、τ也不能过大,过大时引起上电波形过缓,导致板内器件上电时序问题,同时过于缓慢的上电波形可能还会“损伤”或引起MOS管烧毁。

上电时间的选择可根据实际情况进行,建议只要满足板上电源设计要求的3~5倍“冲击”电流即可。

鉴于缓启动电路具有的优点,我们在器件选型和电路设计中可以加以利用,来提高产品的性能和质量。

t

1τ

2τ

3τ

5τ

Uc

0.632

0.865

0.95

0.9933

-

【实用电路设计案例】缓启动电路实例分析与应用2022-10-25 8020

-

TTL电路分析、工作原理、使用方法2023-05-18 7377

-

电源的缓启动电路原理分析2012-08-11 10900

-

缓启动电路2016-05-13 7224

-

labview测试缓启动2017-08-01 3966

-

电源缓启动原理2018-10-11 3562

-

电压型缓启动电路的工作原理是什么?主要的作用是什么?2021-07-20 3454

-

电源缓启动(软起动)原理分享2023-02-23 1575

-

GSM手机射频工作原理与电路分析2016-02-18 923

-

Doherty功放工作原理和设计实例2023-02-09 812

-

缓启动电路实例分析与应用2023-06-26 3566

-

缓启动电路的工作原理 缓启动电路的作用2023-10-24 7792

-

什么是缓跳式温控开关?它的工作原理及优势介绍2024-02-01 1810

-

自启动电路的工作原理 自启动电路需要输入吗2024-02-06 4018

-

缓启动电源有什么优势及作用2024-10-07 4335

全部0条评论

快来发表一下你的评论吧 !