什么是D触发器,D触发器如何工作的?

描述

什么是触发器?

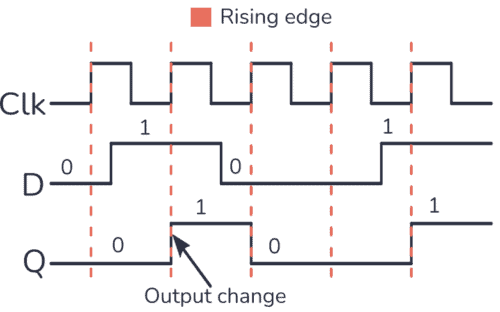

锁存器和触发器有时组合在一起,因为它们都可以在其输出上存储一位(1或0)。与锁存器相比,触发器是需要时钟信号(Clk)的同步电路。D 触发器仅在时钟从

0 到 1(上升沿)或 1 到 0(下降沿)时存储来自 D 输入的新值。

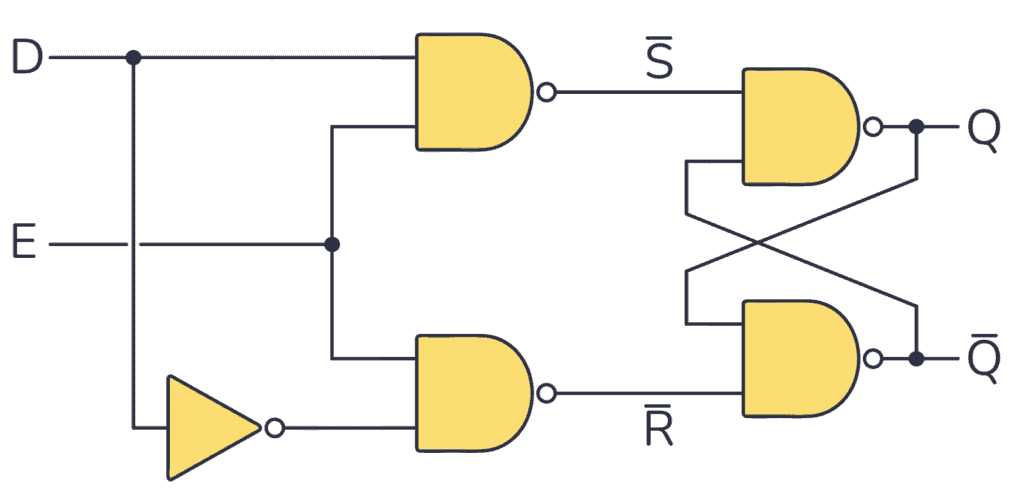

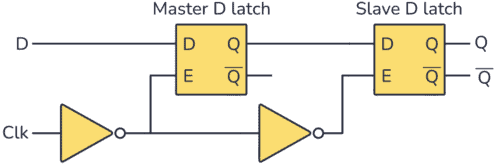

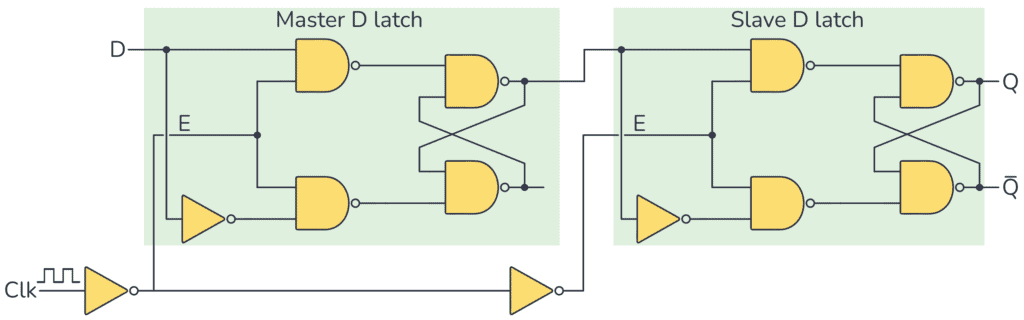

D 触发器由两个 D 闩锁构成。您可以看到一个 D 触发器,它在下面的上升沿更新:

D 触发器主从电路

D 触发器主从电路

该电路的时序图如下所示。它显示了上升沿触发的 D 触发器的行为。输出Q仅在时钟从0变为1时变为D输入的值。

D触发器的时序图

D触发器如何工作?

由于输出 Q 仅在时钟输入从 0 变为 1 时发生变化,因此您将获得以下真值表:

时钟DQ描述

0XQ内存

(无变化)

0→1 (↑)00将 Q 重置为 0

0→1 (↑)11将 Q 设置为 1

1XQ内存

(无变化)

在真值表的第一行和最后一行中,时钟输入为 0 和

1。它们都不是上升沿信号,因此不会发生任何事情。Q输出保留其具有的任何值。在这种情况下,无论D输入具有什么值,Q输出都不会改变,它将保持其值不变。这就是这个电路“记住”一点的方式。

看看中间的两排。这里的时钟输入从0到1,所以你有一个上升沿。这意味着如果D输入为0,Q输出将复位为0。如果 D 输入为 1,则 Q 输出将设置为

1。

预 置

您在准备使用的芯片(例如 CD4013)中找到的 D 触发器通常还具有设置和重置输入,您可以使用这些输入强制 D 触发器在输出上以 1 或 0

开头。使用这些引脚有时称为“预设”D触发器。

D 触发器与锁存器的优势

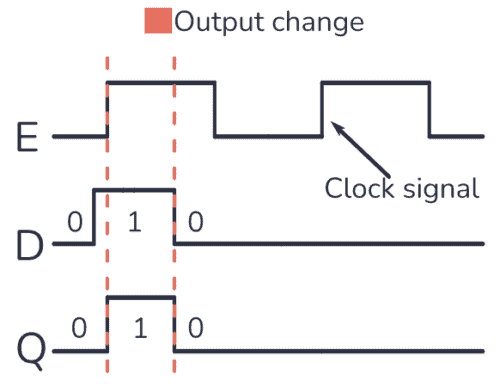

D 锁存电路

D锁存器的缺点之一是,当其使能引脚为1时,其输出可以随时改变。因此,如果将时钟信号应用于 D 锁存器,则在正脉冲持续期间,Q

输出也可能发生变化。

在上面的时序图中,您可以看到在一个时钟周期内,输出既是1又是0,因为D输入在时钟脉冲期间发生变化。这是你不希望在时钟数字系统中发生的事情。

要使该触发器仅在时钟信号的上升沿上改变其输出,您可以构建一个主从D触发器电路,该电路需要两个D锁存器的组合,如下所示:

D 人字拖的工作原理

当Clk输入为0时,主锁存器的输出将更改为D输入的输出。

如果Clk为0,则表示从锁存器的使能输入也为0。因此,此锁存器的输出不会发生任何事情。

但在Clk从0变为1(上升沿)的那一刻,从锁存器的使能输入设置为1。这意味着当Clk从0变为1时,主锁存器输出端的任何内容都将保存到从锁存器的输出中。

如果用 NAND 门构建的 D 锁存器替换符号,您将获得:

-

d触发器是电平触发还是边沿触发2024-08-22 3356

-

t触发器与d触发器的区别和联系2024-08-11 7506

-

d触发器有几个稳态 d触发器和rs触发器的区别2024-02-06 6400

-

D触发器的结构特点、工作原理及主要应用2022-10-11 177887

-

关于D触发器的问题2019-01-16 5101

-

J-K触发器组成D触发器电路图2010-09-24 8968

-

D触发器组成T和J-K触发器电路图2010-09-20 22056

-

D触发器,D触发器是什么意思2010-03-08 5417

-

D触发器/J-K触发器的功能测试及其应用2009-02-14 5563

-

D触发器2008-10-20 3228

-

JK触发器 D触发器 RS触发器 T触发器 真值表2007-09-11 20505

全部0条评论

快来发表一下你的评论吧 !