D锁存器快速入门教程

描述

D 锁存器是最常用于在数字系统中存储数据的逻辑电路。它基于 S-R锁存器,但没有“未定义”或“无效”状态问题。在本教程中,您将了解它的工作原理、其真值表以及如何使用逻辑门构建一个。

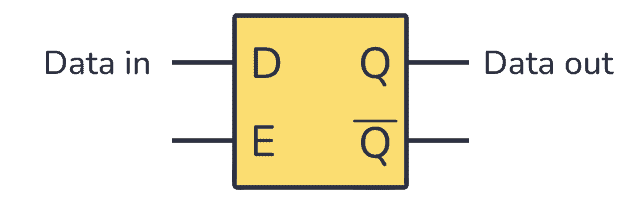

D 闩锁符号

D 闩锁符号

什么是 D 锁存器?

D 锁存器可以存储位值,即 1 或 0。当其使能引脚为高电平时,D引脚上的值将存储在Q输出上。它以 S-R

锁存器的设计为基础,增加了一些逻辑门。您可以在下面看到一个基于 S-R 锁存器的 D 锁存器电路,该锁存器采用 NAND 门构建:

D 锁存电路

D 锁存电路

输入端的逆变器确保S和R输入始终相反,以避免两者为1的无效状态。两个NAND门创建一个新的输入E(使能),允许您控制何时要将输出更改为D输入上的任何输出。

这意味着输出Q只有在使能信号为1时才能改变。如果为 0,则输出不受 D 上任何更改的影响。

您还可以构建带有 AND 和 NOR 门的 D 锁存器,如下所示:

D 锁存器还可用于在定时电路中引入延迟、缓冲器或以特定间隔采样数据。

闩锁和翻转有什么区别?

术语锁存和触发器有时会被错误地用作同义词,因为两者都可以在其输出中存储位(1 或 0)。

虽然锁存器只要启用即可随时更改其输出,但触发器是一种边缘触发设备,需要时钟转换来更改其输出。

要构建 D 翻转翻转,您需要两个 D 闩锁,如下所示:

D 闩锁如何工作?

由于输出 Q 仅在 E 输入为 1 时发生变化,因此您将获得以下真值表:

在真值表的第一行中,E 输入为

0。这意味着闩锁未启用,因此没有任何反应。Q输出保留其具有的任何值。无论D输入具有什么值,Q输出都不会改变,它将保持其值不变。这就是这个电路“记住”一点的方式。

看看接下来的两行。此处 E 输入为 1,因此锁存器已启用。这意味着如果D输入为0,Q输出将复位为0。如果 D 输入为 1,则 Q 输出将设置为

1。

分析电路

您可以通过向 S-R 锁存电路添加三个逻辑门来构建 D 锁存电路。在下图中,您可以看到 D 锁存电路在启用时的位路径,并且在 D 输入上为0。

要分析上述电路,您需要记住,NAND门仅在其两个输入均为0时才产生1。在所有其他情况下,它给出 1。

首先,第一个NAND门的输入为1和0,因此,其输出为1。第二个 NAND 门的两个输入均为 1,因此返回 2。

第一和第二 NAND 门的输出是代表基本 S-R 锁存器的电路部分的输入。考虑到这一点,您可以将位分为两组:S-R 锁存器之前的位(红色)和 S-R

锁存器产生的位(绿色)。

最后,如果你看一下第 4 个 NAND 门。您可以看到,由于第二个 NAND 门,其输入之一为

0。该信息足以告诉您,无论其其他输入的值如何,它都会给出 2。该位是对第三个NAND门输入之一的反馈。由于第一个NAND门,另一个是1,因此Q输出的结果为3 –

与输入D相同。

当 D 为 1 时尝试执行此操作,您将看到输出变为 1。

从此位路径可以得出结论,只要 E 输入为 1,D 锁存器就会将输出 Q 更新为 D 输入上的 Q。

实验:构建自己的D锁存电路

举一个实际示例,您可以使用逻辑门构建基本的D锁存电路,并使用按钮进行测试。R1和R2是下拉电阻,以确保在未按下按钮时输入为0:

正如您在图像的第 1 部分中看到的,Q 为 0(LED L1 熄灭),并且 PB1 和 PB2 均未按下。

接下来,查看推送 PB2 的第 2 部分。现在,D 输入上有一个 1,但输出 Q 仍为 0,因为 E 输入尚未收到使能信号。

第 3 节显示了如何按下 PB1,因此在 E 输入端出现一个 1,并将位 1 从 D 放置到 Q。当 Q 为 1 时,它打开 LED L1。

当 PB1 和 PB2 恢复到第 4 节中的原始状态时,LED L1 保持亮起,表示 Q 输出未改变。

要更改输出 Q,您需要再次推送 PB1。

要组装上述电路,您需要:

四个 NAND 门(例如 CD4011)

一个非门(例如 CD4049 或 CD4069)

2x 按钮

1x 指示灯

2x 10 kΩ电阻(R1和R2)

1x 330 Ω电阻 (R3)

-

Proteus快速入门教程2013-08-03 9309

-

FPGA/SOPC开发快速入门教程2008-08-06 915

-

pro/engineer wildfire 快速入门教程2009-01-14 951

-

FPGA/SOPC开发快速入门教程_elecfans.com2015-11-09 920

-

TimeQuest_Timing_Analyzer快速入门教程2015-12-14 1229

-

超详细Proteus_快速入门教程2017-09-18 1425

-

S-R锁存器快速入门指南2023-06-29 25435

-

allegro快速入门教程2024-02-29 1788

全部0条评论

快来发表一下你的评论吧 !