AND GATE的clock gating check简析

电子说

描述

Gating Cell

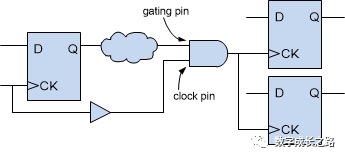

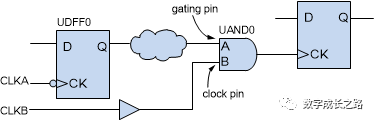

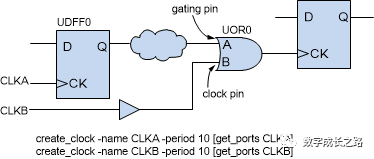

一个cell的一个输入为clock信号,另一个输入为gating信号,并且输出作为clock使用,这样的cell为gating cell。图1中的and gate为gating cell。

图1 gating cell

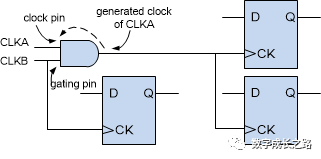

其中这个clock信号需要穿过gating cell,并且gating cell的fanout需要满足以下任意一点:1. 连接到register的ck pin;2. 连接到output pin或inout pin;3. 作为generated clock的master clock。gating信号不能是clock,或者是一个clock,但是不能穿过gating cell。图2中CLKA与CLKB均为clock,但是and gate的输出端定义了generated clock,master clock是CLKA,CLKB不会穿过and gate,这种情况下,PT工具会对and gate进行clock gating check。

图2 两个clock输入的gating cell

AND GATE的clock gating check

在and gate与nand gate上,PT工具会进行active-high clock gating check, gating信号为高时,clock能通过gating cell;同时gating信号的变化需要在clock信号为低时进行,否则将会产生glitch。下面将会对and gate作为gating cell的timing关系进行分析。

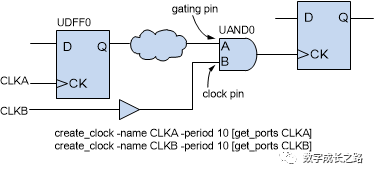

图3 gating cell为and gate

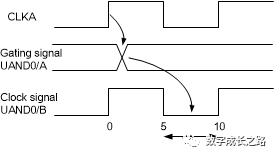

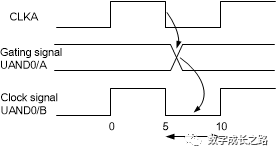

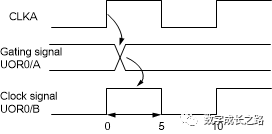

由图4可以看出,UAND0的gating信号需要在CLKB为低时变化。即UAND/A的信号的变化窗口为5-10ns, clock gating setup check时需要UAND0/A在CLKB上升沿之前变,clock gating hold check时需要UAND0/A在CLKB下降沿之后变。PT工具在进行setup/hold gating check时,如果library中没有定义gating cell的setup和hold time,工具会将setup与hold设置为0。我们也可以使用set_clock_gating_check指令设置setup与hold值。图5与图6分别是clock gating check setup与hold的timing报告。由于UAND0/A变得太快,在CLKB为高时变化,hold gating check有violation。

图4 上升沿产生gating信号时序图

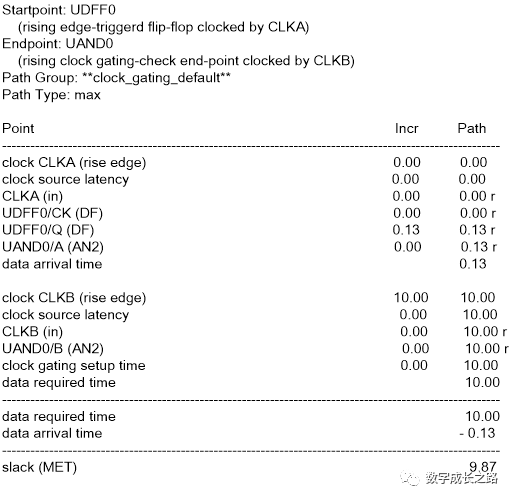

图5 上升沿产生gating信号setup check report

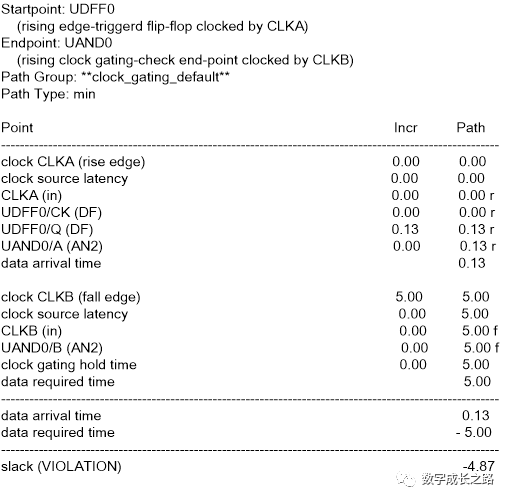

图6 上升沿产生gating信号hold check report

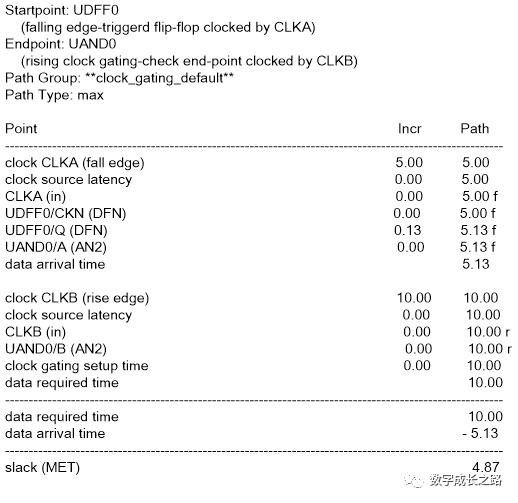

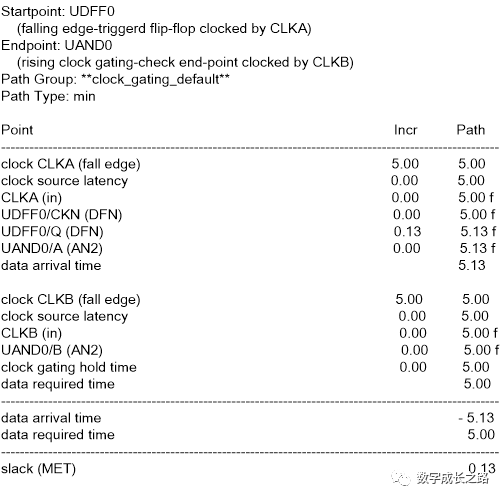

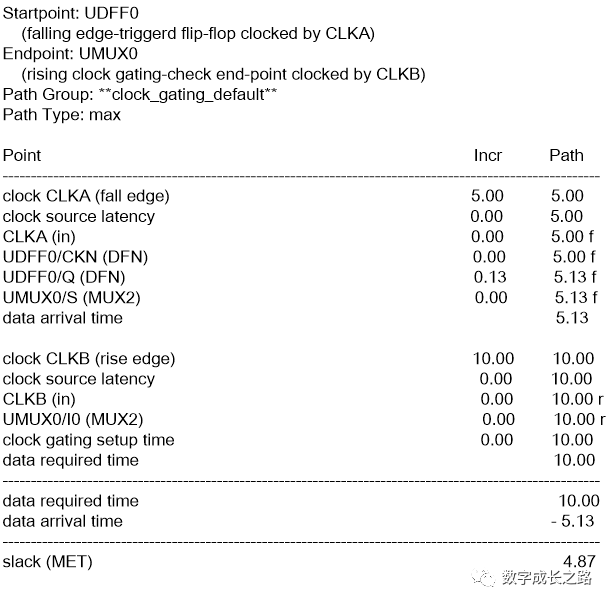

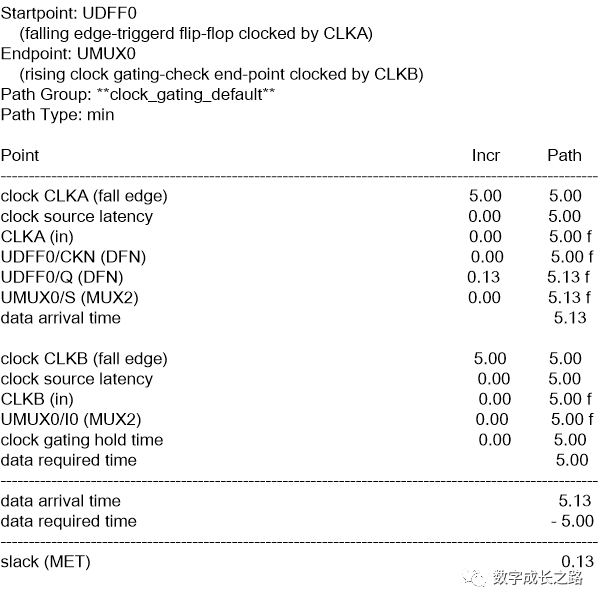

如果UDFF0采用下降沿触发,如图7~图10,setup与hold gating checks都能满足要求。

图7 gating 信号下降沿产生

图8 下降沿产生gating信号时序图

图9 下升沿产生gating信号setup check report

图10 下升沿产生gating信号hold check report

OR GATE的clock gating check

or gate与nor gate上PT工具会进行active-low clock gating check, gating信号为低时,clock能通过gating cell;同时gating信号的变化需要在clock信号为高时进行,否则将会产生glitch。下面将会对or gate作为gating cell的timing关系进行分析。如图11~图14,UDFF0是上升沿触发寄存器,使用or gate作为gating cell, setup与hold gating check均满足timing要求。

图11 gating cell为or gate

图12 gating cell为or gate时序图

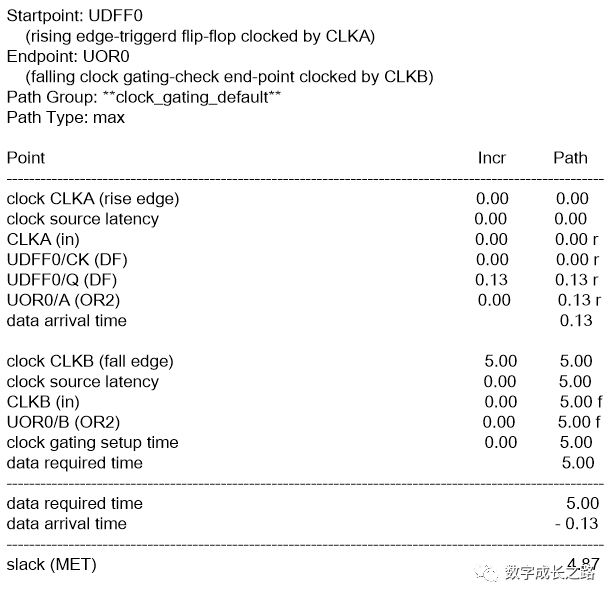

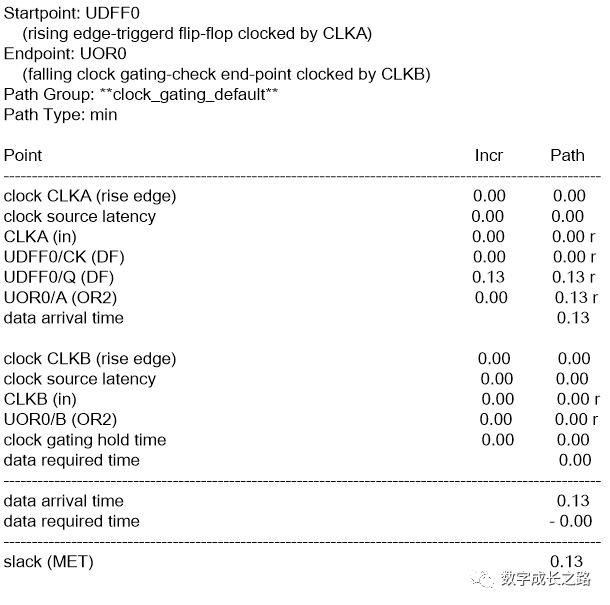

图13 or gate setup gating check report

图14 or gate hold gating check report

Clock Gating with a MUX

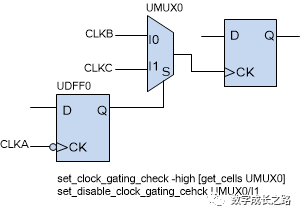

PT工具识别到and gate与or gate这种简单功能的cell为gating cell时,会自动进行clock gating check。但是像mux或者xor这种复杂功能的cell,PT工具会给出一个warning, no clock gating check inferred。除非我们设置set_clock_gating_check指令。如果设置了指令, cell不符合gating cell的功能,PT工具也会给出一个warning。

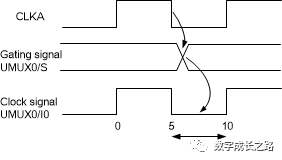

图15中,CLKA与CLKB是周期为10,duty cycle为50%的时钟,当UMUX0/S变化时,需要保证CLKC已经关上了,CLKB处于低。类似active-high clockgating check。我们不关心的pin,UMUX0/I1,可以将clock gating check关掉。图17~图18为mux setup/hold gating check report。

图15 mux做gating cell

图16 mux切换时序

图17 mux setup gating check report

图18 mux hold gating check report

-

clock-gating的综合实现2023-09-04 3473

-

浅析clock gating模块电路结构2023-09-11 4239

-

门控时钟(Clock-gating)介绍2026-01-16 99

-

门控时钟检查(clock gating check)的理解和设计应用2023-06-19 6449

-

低功耗设计基础:Clock Gating2023-06-27 2833

-

clock gate时序分析概念介绍2023-07-03 4892

-

Clock Gating的特点、原理和初步实现2023-07-17 6931

-

ASIC的clock gating在FPGA里面实现是什么结果呢?2023-08-25 1610

-

SOC设计中Clock Gating的基本原理与应用讲解2024-04-28 4372

全部0条评论

快来发表一下你的评论吧 !