在Vivado中使用逻辑分析仪ILA的过程

电子说

描述

FPGA综合出来的电路都在芯片内部,基本上是没法用示波器或者逻辑分析仪器去测量信号的,所以xilinx等厂家就发明了内置的逻辑分析仪。

在vivado中叫 ILA(Integrated Logic Analyzer),之前在ISE中是叫ChipScope。基本原理就是用fpga内部的门电路去搭建一个逻辑分析仪,综合成一个ILA的core核伸出许多probe去探测信号线。

下面逐步讲解在线debug的过程,主要侧重ILA中clock domain的正确使用。

第一大部分 添加被测信号线

通常有两种方式 :

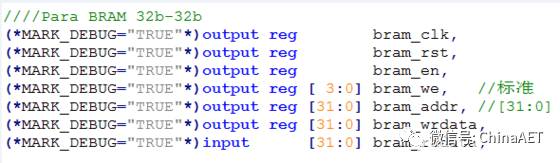

1、在代码中添加这么一句 ( MARK_DEBUG="TRUE" ) 。不管是reg还是wire型的,接口信号或者内部变量,都可以添加。

2、在Setup Debug过程中,直接添加Netlist

我一般是,常用信号都加DEBUG标识,临时测量的就手动加net,需要的就加,不要的就删。

第二大部分 生成ILA模块

1、完成综合之后,Open Synth Design,点里面的Set Up Debug

2、按需要选一个

3、进去之后,就可以添加/删除被测net。如果提示没有参考时钟,右键选择一个合适的即可

4、选择FIFO深度。这个深度可以选很大,每个被测信号都会得到这么大的一个FIFO,所以逻辑分析仪非常占用bram资源!合理设置触发条件,FIFO就不用选太大的。

5、我这里再跳回上一步选时钟域的部分,结合上面的FIFO来说明选取clock domain的重要性。

时钟域的选择会影响两大方面:生成几个ILA核,以及能探测多少时间。

1) 选了3个时钟就一定会生成3个ILA核,毕竟给D触发器的clk不一样嘛;

2) FIFO的参考时钟不同,直接决定FIFO多久会被存满;

比如我这个设计中有3个时钟进来 50mhz 20mhz 以及8mhz转400khz给IIC用。如果IIC的参考50mhz,那scl sda的FIFO瞬间就存满了,触发后FIFO的任务完成了,但是我们连一个信号跳变都看不到。如果参考400khz的,那从起始条件到8bit数据到停止条件都能抓到了。

FIFO存数据是参考信号时钟的,有一拍clk才会存1bit数据。

选择合适的clock domain非常重要,因为最终影响到资源的占用。ILA核的个数,FIFO的个数(经常会出现要抓500个甚至1000个信号。为什么这么多!比如你32位的地址,32位的总线,还读写分开,还有好几个,慢慢就聚集多了,fpga本来功能就是采用并行总线提高速度的原理)。

比如下面这个设置,铁定会生成3个ILA核,分3个波形界面显示。其实如果资源确实够用的话,建议按照大功能分开,这样能显示在不同界面上,然后各自设置触发条件。

第三大部分 信号波形

1、连上jtag,open目标板,然后烧写bit和ltx文件。

2、设置触发条件。这里就跟示波器是一样的用法了,可以run也可以trig。

3、右键有很多功能:short显示名 设置颜色 进制转换 分组 等等,可以琢磨一下。

4、举例子

下面被测的信号是20mhz的clk,但是显示的波形却不是均匀方波!为什么?因为是用50mhz的时钟采的,就是这样的,没有错。所以再说一遍,clock domain的选择非常重要。

-

ILA 抓取MCU200T的内部信号2025-10-29 272

-

逻辑分析仪multisim的应用2024-07-18 2905

-

集成逻辑分析仪(ILA)的使用方法2023-10-01 8178

-

逻辑分析仪是干啥用的 逻辑分析仪的主要用途 逻辑分析仪的应用场景2023-09-19 5653

-

Vivado逻辑分析仪使用教程2023-04-17 1713

-

Vivado逻辑分析仪使用教程简析2023-03-13 4451

-

Vivado中关于ILA的详解2022-02-08 29383

-

Vivado之ILA详解2021-01-22 9362

-

无法在Vivado逻辑分析仪中查看wavefrom2020-03-20 2225

-

Xilinx Vivado软件ILA使用心得2018-11-23 2183

-

为什么要使用逻辑分析仪2017-10-13 3468

-

逻辑分析仪的工作原理2008-11-27 3564

全部0条评论

快来发表一下你的评论吧 !