一文带你搞定高速电路设计

一文带你搞定高速电路设计

电子说

1.4w人已加入

描述

为了方便初次接触高速信号的朋友们能快速入门,并应用到实际的电路设计中。作者特地整理了高速电路设计中常见的一些知识点,具有较强的工程性、实用性,能直接应用到嵌入式硬件、手机等设计中。(有关详细的知识点,持续关注信号完整性基础的更新吧)

01 高速信号定义

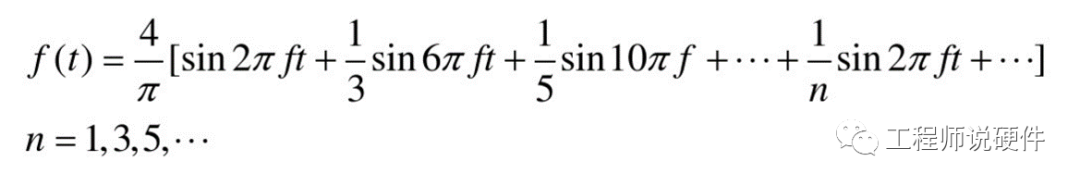

(1)方波的傅里叶变换:周期信号可以分解为一系列余弦信号的叠加。波形边沿越陡峭,谐波分量频率越高。

反射的影响:反射会带来过冲、振铃、回沟等一系列现象,容易造成器件失效、逻辑判断出错、EMI等问题。

图1:方波的傅里叶变换

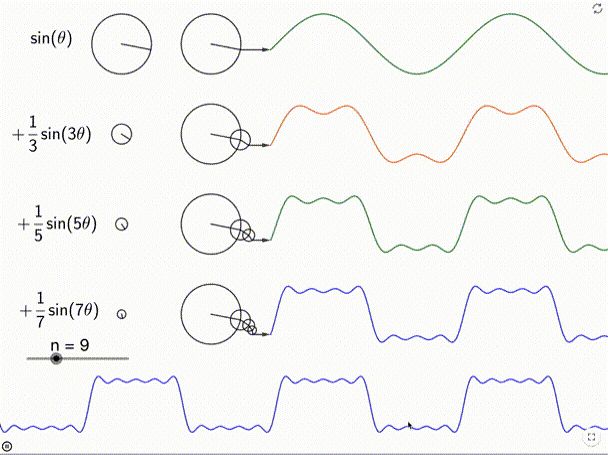

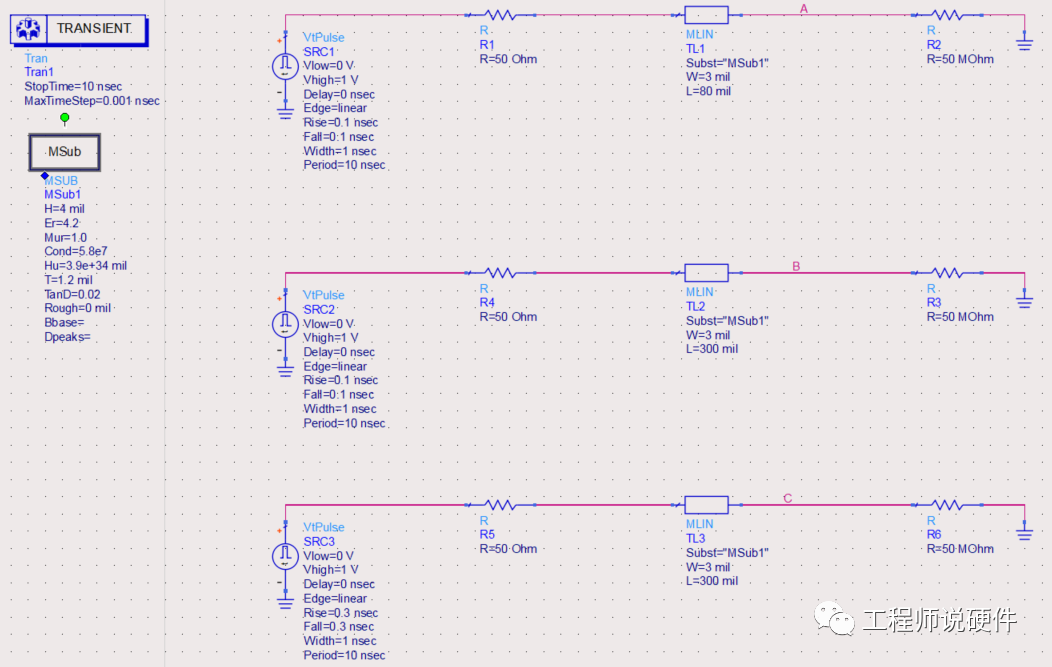

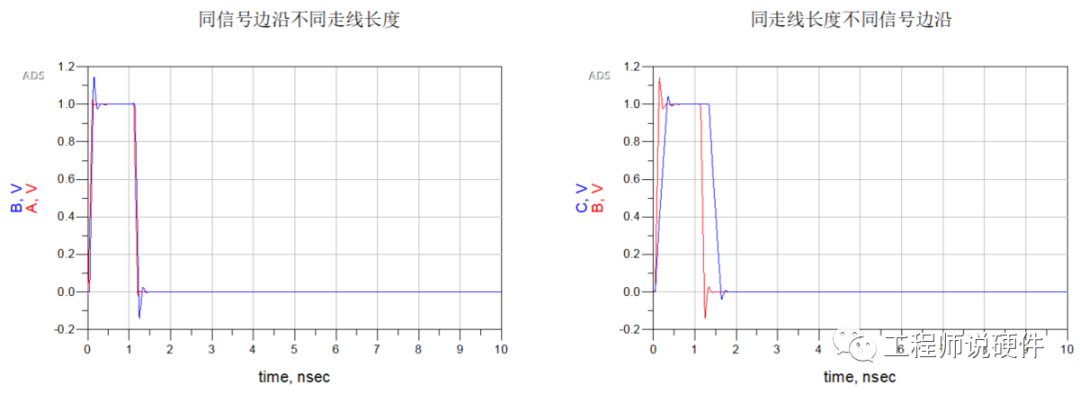

(2)什么时候需要考虑反射:只有当走线的长度达到高速信号定义时需要考虑反射(信号边沿小于4~6倍的走线时延)。如果走线很短,产生的反射会被掩盖在边沿之中。

如下图边沿时间为0.1ns和0.3ns的信号在60mil和300mil走线不连续情况下的仿真结果。

图2、3 ADS仿真:不同边沿和走线长度对信号的影响

02 传输线阻抗和反射

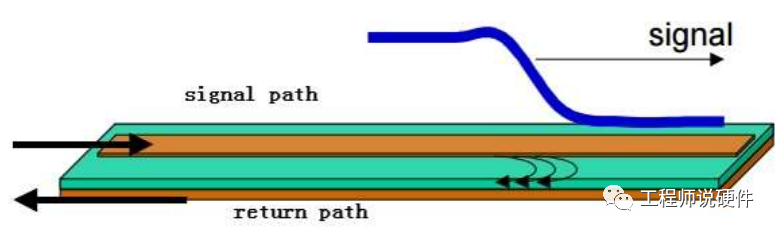

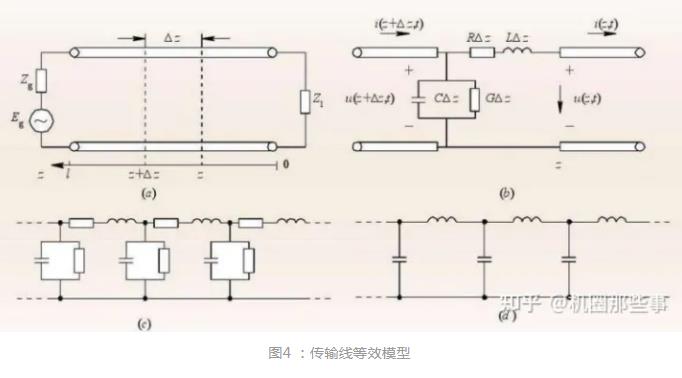

(1)传输线:有信号回流的信号线,PCB常见微带线、带状线、共面波导,同轴线,双绞线。

图4 :传输线示意图

信号在传输过程中每达到一个点,该处信号线和参考平面就会形成电场,进而产生瞬间的小电流,这样在信号传输的过程中,传输线的每一点都会等效成一个电阻,这就是传输线的特性阻抗。

简化公式:Z ≈sqrt( /C)

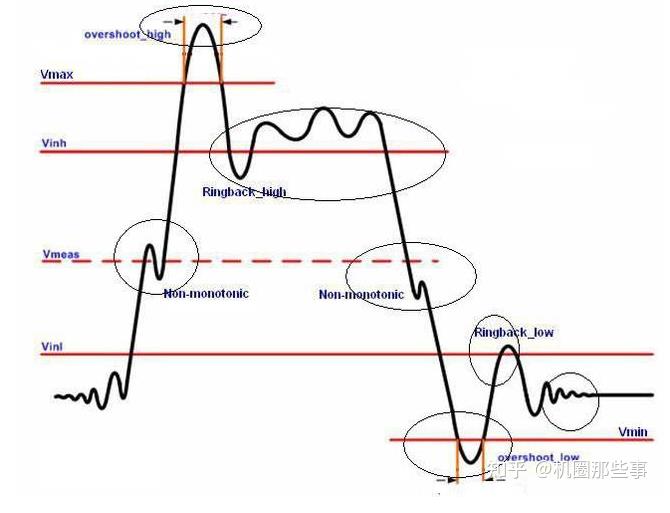

(3)信号在传输线传播的过程中遇到阻抗不连续时造成部分信号回弹的现象,称之为反射。

反射的影响:反射会带来过冲、振铃、回沟等一系列现象,容易造成器件失效、逻辑判断出错、EMI等问题。

图5 :信号完整性问题示意图

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

智慧公交是什么?一文带你详解智慧公交的解决方案!2024-11-05 1904

-

高速电路设计指南2022-09-13 894

-

高速电路设计交流2022-03-31 719

-

高速电路设计实践.pdf2022-03-07 5648

-

彻底搞定电路设计中的接地问题2021-06-08 1222

-

【高手问答】电子老顽童带你看懂电路设计2019-10-31 166506

-

模拟电路原理在高速数字电路设计的应用分析《高速数字电路设计教材》2018-09-10 1777

-

华为高速电路设计教材2018-01-22 41005

-

高速电路设计实践2016-11-18 1203

-

高速MOS驱动电路设计和应用指南2016-06-22 1374

-

高速电路设计与实现2016-01-18 758

-

高速电路设计2015-07-06 3716

-

高速数字电路设计教程2010-06-23 1203

全部0条评论

快来发表一下你的评论吧 !