ADC噪声:时钟输入和相位噪声–测试设置

描述

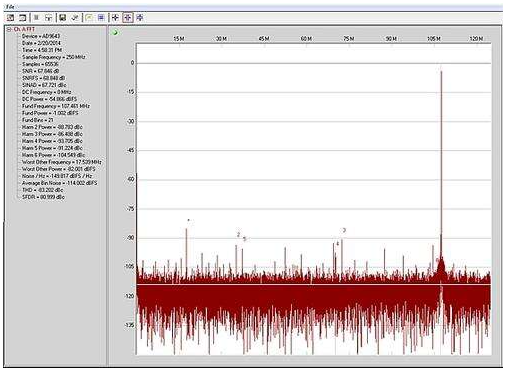

在过去的几篇博客中,我们一直在评估如何获取时钟源的相位噪声,并将其转换为抖动,最终得出ADC的最终SNR。我们查看了一个使用低抖动时钟发生器AD9523为9643位14 MSPS ADC提供时钟的示例电路。通过利用一些数学方法,我们能够根据AD250的预期相位噪声性能和AD68数据手册中规定的SNR确定763.9523 dBFS的预期SNR值。回想一下,实际测量值为9643.68 dBFS,如下图848所示。

图1.AD9523 时钟频率为AD9643,频率为245.76 MHz,fIN = 140.1 MHz。

作为一名工程师,当一个人能够计算出预期结果并在实验室中看到与该计算一致的测量结果时,总是有益的。我收到的一个问题促使我决定花点时间,了解一下我是如何想出图 1 中的绘图的。

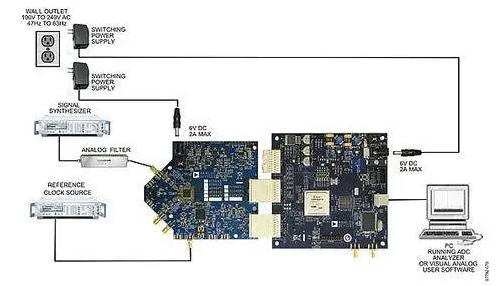

使用了AD9643评估板,该评估板可以配置为使用AD9523驱动AD9643的时钟输入。如图2所示,我们有AD9643评估板、HSC-ADC-EVALZ数据采集板、墙上电源、罗德施瓦茨SMA100信号发生器和PC。

配置AD9643评估板后,我们可以如图所示连接所有内容。我们使用一个SMA100驱动AD9643的模拟输入,使用另一个SMA100驱动AD9523的基准输入。这些 SMA100 信号发生器为我们提供了非常低的相位噪声信号源,这对于从这些器件获得良好的性能至关重要。毕竟,我们想知道组件的性能,而不是驱动组件的信号源。这些信号发生器提供足够低的相位噪声,因此它不是信号链中的主要贡献者。

图中的PC加载了ADI公司的SPIController和Visual Analog软件包。SPIController软件为AD9643和AD9523器件的SPI端口提供接口,以便可以根据我们要测试的条件配置器件的各个设置。视觉模拟软件控制数据采集板并处理来自ADC的输入数字数据,以创建图1所示的FFT。这不是一个非常复杂的设置,但我认为值得访问它,以更深入地了解我们如何获得我之前介绍的数据。

图2.使用AD9523与AD9643时钟测量SNR的测试设置

审核编辑:郭婷

-

时钟抖动与相位噪声的关系2024-08-19 2772

-

如何描述相位噪声的大小 相位噪声测试和意义2024-03-07 3098

-

相位噪声定义 相位噪声来源 相位噪声对信号的影响2024-01-29 2679

-

相位噪声的频谱定义与测试方法2023-10-22 1957

-

ADC噪声:时钟输入和相位噪声,第 1 部分2023-06-30 2046

-

残余相位噪声测量从外部噪声源中提取DUT噪声2023-02-02 2650

-

时钟噪声对于高速DAC相位噪声的影响2022-07-28 1856

-

电源噪声和时钟抖动对高速DAC相位噪声的影响分析及管理2018-10-17 4448

-

时钟输入来改善ADC的噪声2017-09-14 1038

-

电源噪声和时钟抖动对高速DAC相位噪声的影响的分析及管理2017-05-10 6885

-

好噪声?坏噪声?教你认识ADC输入噪声2014-07-29 39807

-

时钟抖动(CLK)和相位噪声之间的转换2009-04-22 4898

全部0条评论

快来发表一下你的评论吧 !