交错式ADC:基础知识

描述

交错式ADC转换器绝对是推动更高效接口的一部分。交错式ADC转换器为系统设计人员提供了多种优势。然而,随着转换器带宽的增加,需要在FPGA或ASIC中处理大量数据。必须有一些有效的方法来处理转换器中的所有数据。在采样速率在千兆采样范围内的转换器中继续使用LVDS接口变得不切实际。因此,JESD204B是将大量数据从转换器传输到FPGA或ASIC的良好、高效方法。

让我们花点时间离开界面,看看交错。在通信基础设施中,除了对DPD(数字预失真)等线性化技术有更宽的带宽要求外,还不断推动更高采样速率的ADC,以允许多频段、多载波无线电。在军事和航空航天领域,更高的采样速率ADC允许多用途系统,可用于通信、电子监控和雷达等。在工业仪器仪表中,对更高采样速率ADC的需求总是在增加,以便可以精确测量更高速的信号。首先,让我们了解交错式ADC的基础知识。

利用m个ADC可以将有效采样速率提高m 倍。 为了简单易懂,我们只关注两个ADC的情况。在这种情况下,如果两个ADC的采样速率为fS交错,所得采样率仅为2fS.这两个ADC必须具有时钟相位关系才能正确交错。时钟相位关系由公式1决定,其中n是特定的ADC,m是ADC的总数。

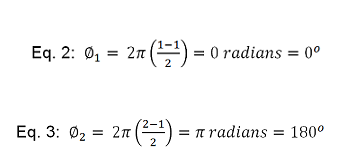

例如,交错连接两个采样速率为250MSPS的ADC,以实现500MSPS的采样速率。在这种情况下,公式1可用于推导两个ADC的时钟相位关系,由公式2和3给出。

现在我们知道了时钟相位关系,可以检查样本的构造。图1直观地显示了两个250MSPS交错ADC的时钟相位关系和样本结构。

图1

两个交错式250MSPS ADC – 基本图

请注意 180° 时钟相位关系以及样本的交错方式。输入波形由两个ADC交替采样。在这种情况下,交错是通过使用500MHz时钟输入实现的,该输入被分频为<>。分频器负责将时钟所需的相位发送到每个ADC。

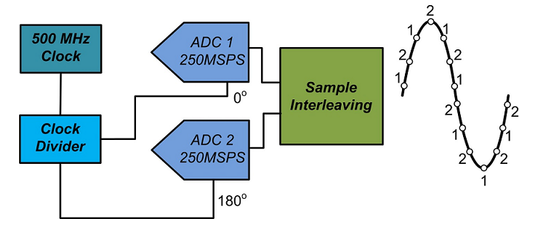

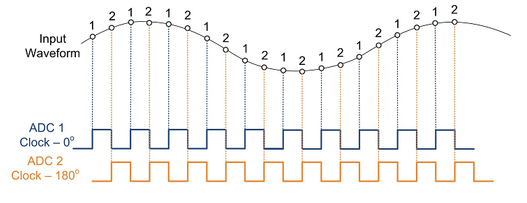

图 2 显示了此概念的另一个表示形式。

图2

两个交错式 ADC – 时钟和采样

通过交错这两个250MSPS ADC,采样速率提高到500MSPS。这将转换器奈奎斯特区的宽度从125MHz扩展到250MHz,使可用工作带宽翻倍。增加的操作带宽带来了许多优势。无线电系统可以增加支持的频段数量;雷达系统可以提高空间分辨率,测量设备可以实现更大的模拟输入带宽。

审核编辑:郭婷

-

伺服环路ADC测试的基础知识介绍2023-08-21 2950

-

一文带你了解交错式ADC(数据转换器)2023-05-11 2120

-

交错ADC:揭开谜团2023-01-08 2617

-

模拟基础知识:处理SAR ADC输入驱动难题2021-11-05 3415

-

嵌入式系统基础知识讲解2021-07-30 1105

-

交错式ADC之间的带宽失配分析2021-04-02 1281

-

ADC转换器的基础知识详细资料说明2019-07-18 1499

-

有ADC和传感器的基础知识吗?2019-02-21 5325

-

模拟数字转换器(ADC)基础知识2018-06-05 1673

-

ADC入门_基础知识2016-03-11 1152

-

嵌入式系统基础知识2016-03-03 855

-

ADC【DSP基础知识】2016-01-06 555

-

交错式ADC的基础知识2014-04-17 4965

-

交错式功率因数校正2010-07-30 431

全部0条评论

快来发表一下你的评论吧 !