ADC噪声:时钟输入和相位噪声,第 1 部分

描述

正如我们大多数人在日益混合信号的世界中工作时可能知道的那样,模拟和数字设计人员通常以不同的方式看待同一问题。对一个人来说,它是po-tay-to,对另一个人来说,它是po-tah-to,或者可能是to-may-to而不是to-mah-to。对于模拟工程师来说,它是相位噪声,但对于数字工程师来说,它是抖动。这一切都取决于你用什么眼镜来观察世界,以及设计中什么是重要的。

那么,如果我们是介于模拟和数字世界之间的ADC,我们该怎么办?好吧,我们必须了解它们以及如何将它们联系起来。

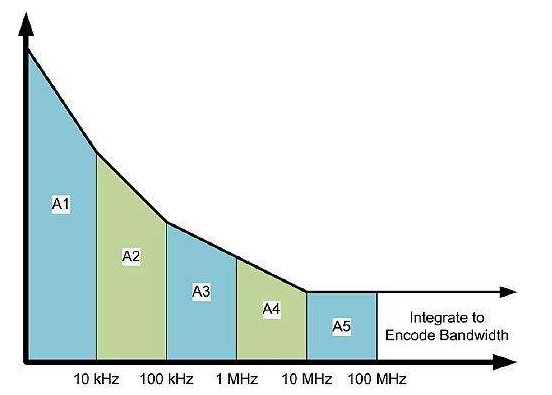

这是为数不多的跨越围栏是有利的情况之一。目前市面上的许多时钟产品都指定器件的相位噪声,而不指定抖动。让我们来看看如何从相位噪声变为抖动。然后,我们将能够预测具有一定抖动的ADC的SNR。一个例子将不得不等待,因为我在这里只有这么多空间。现在让我们专注于数学。下图显示了我们如何根据时钟源的相位噪声计算抖动。

编码带宽上的相位噪声积分。

这实际上是一个非常简单的概念。如您所见,相位噪声曲线下有不同的区域被突出显示(A1至A5)。这些区域只是时钟源数据手册中为每个区域给出的积分相位噪声功率(dBc)。为了稍微简化数学,我们将采用梯形近似来获得每个区域中的面积。为了从该相位噪声信息中获得抖动,我们将从接近基频时钟频率到编码带宽(即ADC采样速率)的相位噪声进行积分。

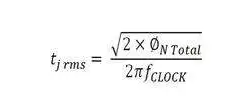

首先,我们对曲线上所有相位噪声点进行反对数运算,然后将它们相加以实现积分噪声。接下来,我们需要以秒为单位将其转换为均方根抖动,以便我们可以用它来计算对ADC噪声(SNR)的影响。为此,我们需要以下等式。

我们可以获取这些数据并对相位噪声进行积分,以找到均方根抖动,然后得出对ADCSNR的影响。如MT-008所示,近载波相位噪声对ADC的SNR没有太大影响。宽带相位噪声的影响最大。因此,我们可以做一些假设,使计算更容易一些,节省一些时间,并对最终SNR进行很好的评估。正如我们稍后将看到的,我们可以根据从时钟源的相位噪声得出的均方根抖动来非常准确地预测ADC的SNR。

因此,现在我们有了工具,可以根据给定时钟源的相位噪声计算均方根抖动。现在,我们可以采用这些方程,利用时钟源的相位噪声推导出均方根抖动,并找到其对ADCSNR的影响。

审核编辑:郭婷

-

时钟抖动与相位噪声的关系2024-08-19 2694

-

什么是相位噪声 产生相位噪声的原因 相位噪声的表示方法及影响2024-01-31 5415

-

相位噪声定义 相位噪声来源 相位噪声对信号的影响2024-01-29 2597

-

ADC噪声:时钟输入和相位噪声,第 2 部分2023-06-30 2775

-

如何测量ADC噪声2023-03-16 3917

-

残余相位噪声测量从外部噪声源中提取DUT噪声2023-02-02 2611

-

LDO基础知识:噪声 - 第1部分2022-11-01 853

-

时钟噪声对于高速DAC相位噪声的影响2022-07-28 1837

-

测量较低时钟频率的相位噪声和相位抖动2021-06-24 3729

-

DAC相位噪声测量改进以支持超低相位噪声DDS应用2018-10-17 1650

-

时钟输入来改善ADC的噪声2017-09-14 1016

-

电源噪声和时钟抖动对高速DAC相位噪声的影响的分析及管理2017-05-10 6860

-

好噪声?坏噪声?教你认识ADC输入噪声2014-07-29 39599

-

时钟抖动(CLK)和相位噪声之间的转换2009-04-22 4871

全部0条评论

快来发表一下你的评论吧 !