如何为ADC噪声提供通道

描述

在考虑ADC中的噪声时,几乎可以将ADC视为混频器。如果有噪声从各种门口中的任何一个进入ADC,则噪声可以表现在输出数据的FFT中。

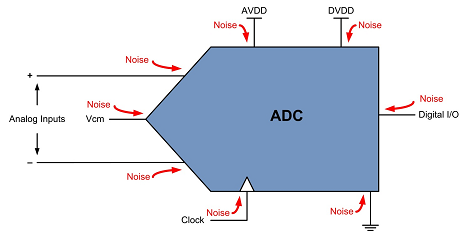

图1显示了我们之前讨论的噪声门口,其中包括电源输入、模拟输入和时钟。但是,在使用ADC时,我错过了更多我们绝对应该考虑的门口。第一种是共模电压(Vcm)输出,为模拟输入提供共模电平。接下来是数字输入和输出(I/O),它们可能是噪声进入ADC的路径。最后,有一个门口可能是最容易被忽视的门口之一——地面或电路。

图1

额外的ADC噪声“门口”

如今,许多高速ADC都使用Vcm输出为ADC模拟输入提供共模基准电压。它是ADC输入最小到最大范围内的中点电压。该引脚通常需要一个大约0.1μF的去耦电容。这为输出稳定性以及高频噪声的滤波提供了一个主导极点。进行适当的去耦非常重要,因为该节点为ADC模拟输入的噪声提供了潜在的直接线路。即使它是输出,噪声也会强行进入ADC的内部偏置电路。

除电容外,许多具有两个或更多通道的ADC还需要少量串联电阻,每次连接Vcm输出到每个通道。这也是降噪的一种形式,因为它通常有助于减少ADC通道之间的串扰。另一种说法是,额外的串联电阻有助于改善通道间的隔离,使来自一个通道的信号不会进入另一个通道。

ADC的数字I/O线也是噪声的门口。数字I/O有几种不同的功能,因此噪声通过每种功能进入ADC的方式也不同。最明显的是数字输出接口。对于具有CMOS输出的ADC来说,由于其单端实现,这更令人担忧。

通常,具有LVDS输出的ADC或采用串行JESD204B接口的ADC对噪声耦合的免疫力要强得多。除数字输出外,ADC内部的数字电路数量也越来越多,这为通过控制线的噪声提供了一些潜在的入口点。随着数字内容的增加,需要为这些功能提供 I/O。有时,额外的I/O是通过SPI(串行端口接口)完成的。有时,SPI 无法处理所有需要处理的问题。

关于SPI的附带说明:SPI不仅是一个潜在的噪声门,还可能导致其他转换问题。各种建议表示,在系统运行时(进行转换时)不要访问ADC的SPI。

其他I/O包括模式控制、掉电、待机、超量程指示器、同步引脚等。这些都是需要注意的事项,除了良好的布局实践以避免噪声耦合外,还要确保使用适当的去耦。

可能最容易被忽视的门口(我上次自己当然也忽略了这一点)是ADC的地面。请注意,当我说接地时,我指的是电路通用。另请注意,通常有多个接地连接,例如模拟接地和数字接地。对于这两个理由,您有时需要考虑它们粘合或捆绑在一起的位置。这是某个时候另一个博客的主题。

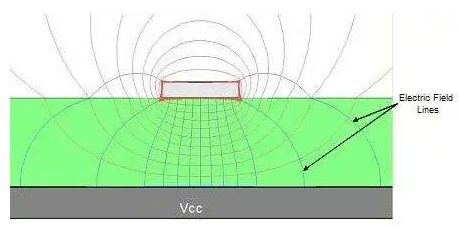

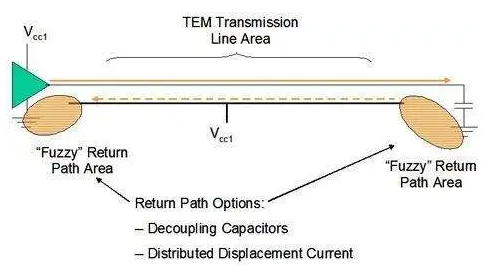

地面通常被认为是一个坚实的参考点。然而,地并不总是一个稳定的参考点,并且可能允许噪声进入ADC。在系统设计和布局中注意接地层非常重要,以确保有足够的平面面积而不会中断,并且有足够的接地过孔以允许适当的电流返回路径。在设计中必须考虑所有电流返回路径,而不是假设接地是一个稳定的参考点。

如果没有适当的系统设计,噪声可能会存在于接地层中,并可能进入ADC。

流向其他地方的电流,而不是你认为它将或应该流动的地方,实际上并不是最严格意义上的噪音,但它显然是麻烦。

审核编辑:郭婷

-

拆解 AD7193:4 通道超低噪声 24 位 Σ-Δ ADC 的卓越性能与应用潜力2026-04-01 480

-

ADC3683 双通道、18位、65MSPS、低噪声、超低功耗、低延迟ADC技术手册2025-11-01 1254

-

使用PSoC™ C3 ADC的16 S/H,如何为各个通道配置不同的采样频率?2025-04-21 2516

-

ADC3660 16位、0.5至65MSPS、低噪声、低功率双通道ADC数据表2024-07-18 589

-

ADC3644 14位125MSPS低噪声低功耗双通道ADC数据表2024-07-17 620

-

ADC364x 14位、10至65MSPS、低噪声、低功率双通道ADC数据表2024-07-12 751

-

ADC噪声:时钟输入如何提供帮助2023-06-30 1601

-

4.5 计算ADC系统的总噪声#ADCEE_Voky 2022-08-16

-

5 计算ADC系统的总噪声#ADCEE_Voky 2022-08-15

-

如何为ADC增加隔离而不损害其性能2022-08-01 2548

-

AD7196:2 通道、 4.8 kHz 、超低噪声、 集成 PGA 的 24 位 Σ-∆ 型 ADC2021-03-20 1115

-

其中一个ADC通道噪声很大2018-09-27 2472

全部0条评论

快来发表一下你的评论吧 !