交错杂散:增益失配的更多数学细节

描述

现在事情变得越来越有趣。我们一直在研究交错杂散的位置,并查看了偏移失配产生的杂散水平。通过进行一些计算,我们能够看到两个交错ADC之间的失调失配会产生多大的杂散。就像我们在查看马刺的位置时所做的那样,我们现在将采取类似的路径。我们首先研究了偏移失配,所以现在让我们深入了解如何计算在fS/2 ± f在由于增益不匹配。

又到了戴上我们数学家的帽子的时候了......不过别担心,我们不会穿太久。我们需要它一段时间,因为我们继续关注一些不匹配并深入研究增益不匹配刺激。

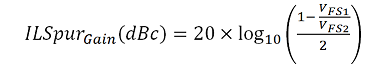

那么,我们如何知道增益不匹配的刺激会有多大呢?让我们看一下下面的公式 1,其中 V科技委和 V科技委是我们交错的两个ADC的满量程峰峰值电压。

等式 1

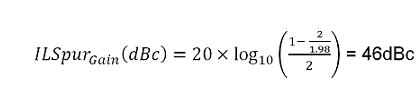

现在,让我们考虑双通道器件中两个14位ADC之间的典型增益失配。通常,这大约是标称值满量程的 1%。这意味着ADC1的满量程电压为2VQ-1ADC2的满量程电压为1.98VQ-1.将其代入公式1,我们得到以下结果:

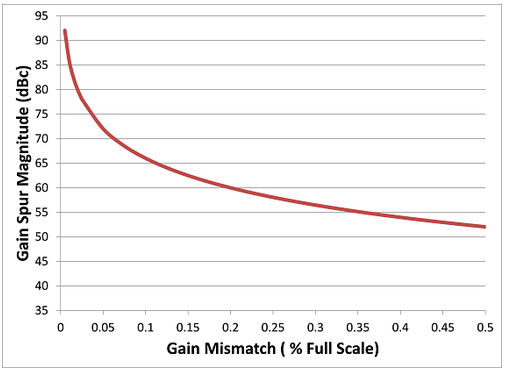

哇,这很有趣!满量程的46%似乎没有太大的增益误差,但它会产生相当大的70dBc失调杂散。我怀疑目前有许多高速ADC应用可以承受输出频谱中的这种杂散水平。这很容易主导交错式ADC的无杂散动态范围(SFDR)规格。大多数应用需要至少46dBc或更好的SFDR,这意味着70dBc太高了。让我们来看看为了达到或超过1dBc的水平,我们需要在哪里。在图<>的下面,增益失配杂散的大小相对于以满量程百分比给出的增益失配表示。

图1

增益杂散与增益失配(交错式14位ADC)

该图为我们提供了一些很好的信息,并深入了解了我们可以容忍的增益不匹配水平。为了满足70 dBc的典型杂散要求,0位转换器的增益失配必须小于满量程的05.14%。这让我们了解两个ADC之间的增益需要匹配的程度。它很小。

然而,随着工艺技术的缩小和匹配技术的改进,最小化增益失配变得更加容易。在像AD9286这样的器件上,典型增益失配约为满量程的0.05%,这正好符合我们正在寻找的70dBc规格。如果我们能够将失配再减少0.025%,那么我们可以将增益失配杂散降低到78dBc。如果我们能更进一步,将失配降低到0.005%,那么我们可以将杂散降低到92dBc。

审核编辑:郭婷

-

深入分析时间交错技术2018-10-24 1905

-

交错ADC之间的增益不匹配2019-07-25 2284

-

模拟工程师如何解决交错式ADC宽失配问题?2019-07-31 1527

-

交错式ADC之间的带宽失配分析2021-04-02 1281

-

lna差分输出的增益失配和相位失配要怎么设置才能仿真出来?2021-06-25 2074

-

基于循环自相关的TIADC通道失配校正2009-12-31 863

-

交错式ADC之间的带宽失配解决方案2017-11-16 724

-

交错式ADC之间的带宽失配2017-12-05 791

-

交错式ADC之间的带宽失配应该如何解决2020-09-27 715

-

交错式ADC的带宽失配问题的解决方案分析2020-09-02 1508

-

失配损耗对射频功率测量和级联放大器增益的影响是什么2023-02-19 3289

-

使用时间交错数据转换器倍增采样率2023-02-24 1659

-

交错马刺:时序不匹配的数学2023-06-30 1598

全部0条评论

快来发表一下你的评论吧 !