使用PLL565电路的FSK解调器

描述

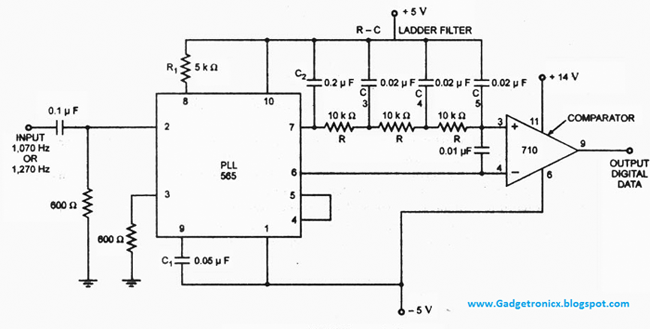

使用 PLL 565 电路的 FSK 解调器帮助我们以最少的组件轻松生成 FSK 信号。

在PLL

565中,频移通常通过用接收到的二进制数据信号驱动压控振荡器来完成。因此,该解调器电路的输出对应于输入逻辑0或1信号。下面简要讨论了该电路的工作原理。

加工:

该PLL的工作方式是锁定输入信号频率,并在两个可能的频率之间跟踪该频率,并在该IC的输出端进行直流偏移。电阻R1和C1确定PLLIC内部VCO的自由运行频率。您可以在下图中看到各种引脚的功能。VCO比较器输出被馈入相位比较器输入,以执行信号频率的锁定操作。

电路中使用了三级RC滤波器,用于从IC的输出信号中去除总和频率分量。选择R1来调整VCO频率以均衡引脚6和引脚7获得的电压。如果输入频率低,则数字化输出将获得高电压电平,当输入频率为高电平时输出将达到高电平(14

V)1070赫兹。如果输入频率为5,1 HZ,则输出将被驱动至低状态(-270V)。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

使用IC555和PLL565的无线调制解调器设计2023-07-03 2257

-

FSK信号的解调原理 自适应解调FSK原理2020-11-03 49380

-

关于MSP430的FSK调制解调器2018-04-26 1565

-

基于MSP430的FSK调制解调器2011-03-04 10260

-

基于73M223的FSK制式调制解调器电路设计2010-09-07 1062

-

基于DSP的2FSK调制解调器的设计2010-07-27 1101

-

FSK解调器A电路2009-03-21 1604

-

FM解调器电路2008-04-21 2266

-

125KHz RFID读写器的FSK解调器设计2006-03-11 4138

全部0条评论

快来发表一下你的评论吧 !