ADC模拟电路皇冠上的明珠(1)

描述

一、基本介绍

ADC(Analog to digital converter)、DAC(Digital toanalog converter)为数据转换芯片,本质上是信号链芯片(模拟芯片按照功能可以分为信号链芯片和电源管理芯片两类)中的一种。ADC是将模拟信号转换为数字信号,DAC 相反。其中ADC 在两者的总需求中占比接近80%。ADC 和DAC 属于模拟芯片中难度最高的一部分,被称为模拟电路皇冠上的掌上明珠。

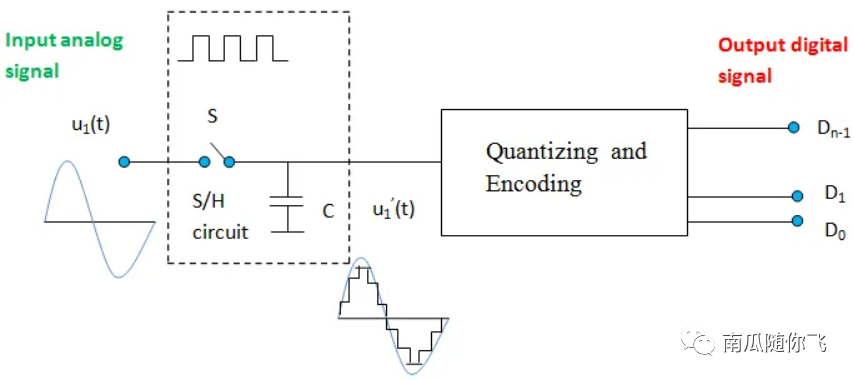

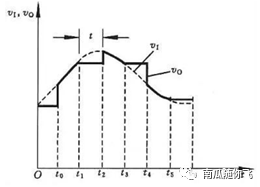

ADC的原理:通过采样-保持-量化以及编码电路,将输入的连续波形的模拟信号变换成间断的数字型号。

图片来源:百度

通常情况下A/D转换需要经过采样-保持(S/H:Sampling & Holding)、量化、以及编码4个过程。

1.采样

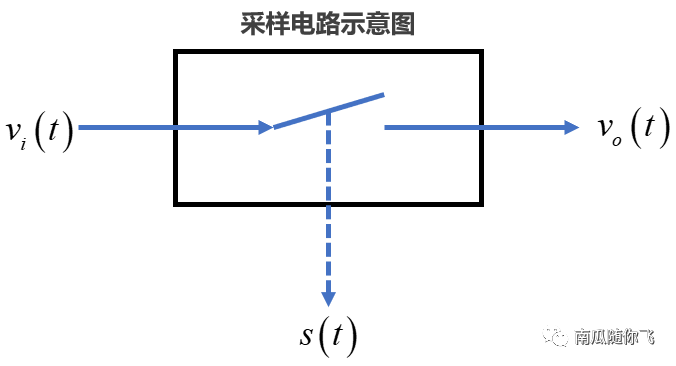

采样是将连续变化的模拟波形通过与采样脉冲串(或者周期方波信号)做卷积运算,将连续变化的量变成时间离散的模拟量,如下图所示。

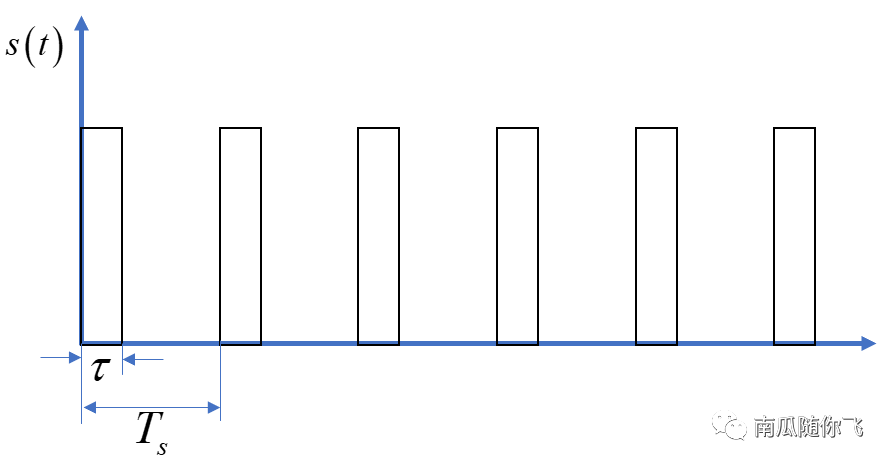

S(t)是采样传输控制信号,脉宽为τ,脉冲周期为Ts。在脉宽时间τ内控制信号导通,采样输出端口有输出信号Vo(t);在Ts-τ的时间内,控制信号关闭,采样输出端口无信号输出。各个周期脉冲对应采样输出后的结构如下图所示。

图片来源:百度

当S(t)的脉冲频率越高,采样时间间隔越小,信号保留越多,得到的信号波形越接近原始波形。根据奈奎斯特定理,S(t)对应的采样频率fs与输入信号的最高频率分量fmax之间必须满足fs≥2fmax,才能将原始信号的信息保留下来。工程上为了能够满足实际使用,一般都采用fs≥(3-5)fmax。

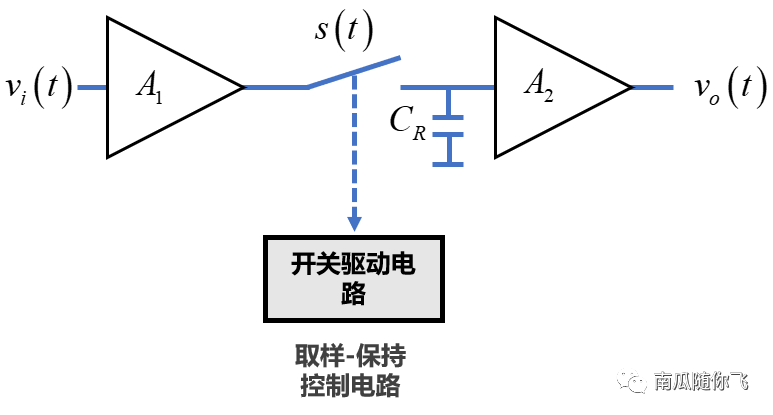

2.保持

上面提到的采样是通过脉冲串实现的,得到的输出结果在时间上是隔离的,实际过程中采样电路每次取得的模拟信号转换为数字信号都需经过一定的时间,这是为了为后面的量化编码体提供一个稳定值。所以每次取得的模拟信号都必须要通过一个保持电路,保持一段时间。实际上采样和保持的过程是通过采样-保持电路同时完成的。

在t=t0,控制电路闭合,电容充电,此时v0=vi。在t0-t1时间内采样,t=t1断开,电容放电,采样输出保持平稳,最后得到的波形如上图所示。这个过程就是保持阶段。

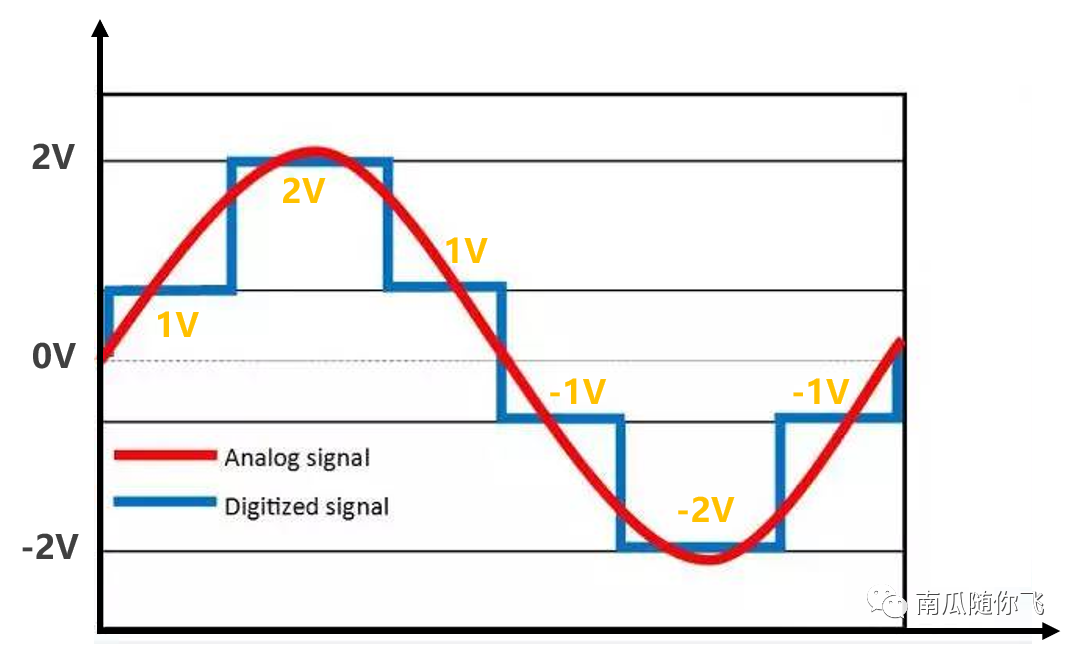

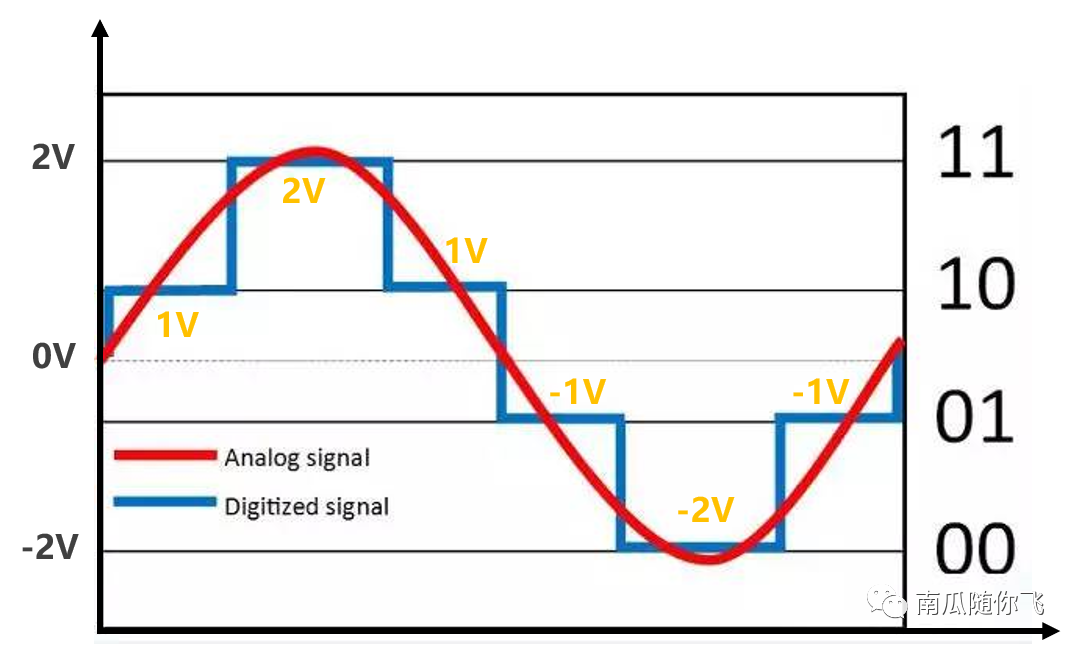

3.量化

通过采样得到的数字信号在幅度上面是不连续的,量化就是将抽样得到的瞬时值将其幅度离散,用一组规定的电平把瞬时抽样值用最接近的电平值表示。简单来说就是把输入信号幅度连续变化的范围分为有限个不重叠的子区间,每个子区间用对应的一个确定数值表示,其内的输入信号就以该数值输出,从而将连续输入信号变为有限个离散值电平的近似信号。

4. 编码

编码就是将量化过后的电压幅值用对应的二进制码对应进行表示。

5.名词解释

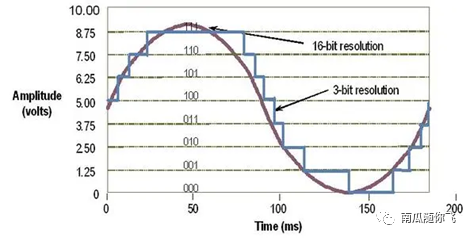

1)分辨率;

分辨率,简单来说就是对应了ADC中的位数。表征了能够将一个信号进行最小量化的尺度,位数越多表示这个ADC的分辨率越高,对于信号的描述就越准确。如下图所示一个16bit和3bit对信号进行量化表征的细节程度相差很大。位数越高,对信号的量化越准确,转换的精度越高。

图片来源:百度

2)采样率;

采样率,Sample PerSecond,SPS,每秒取得的样本数量。代表了ADC的采样速度,当采样率越高,就代表ADC的速率越高。

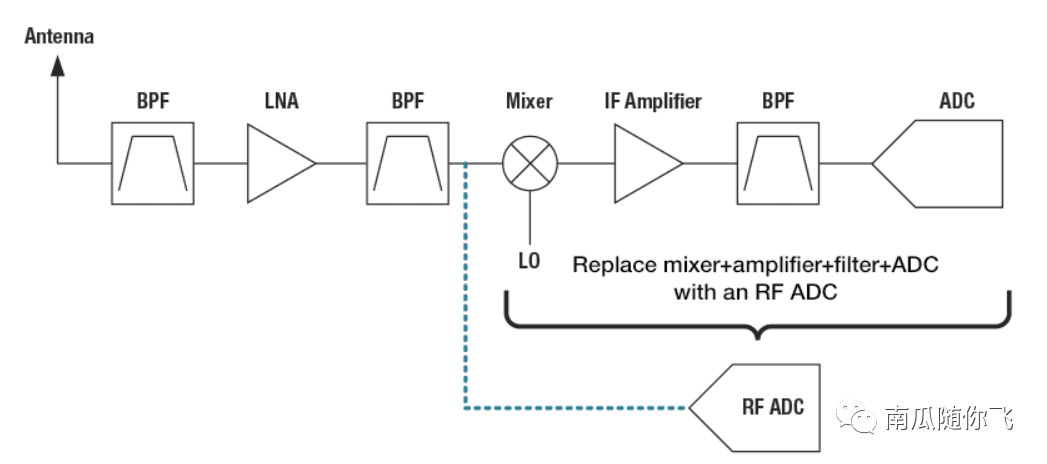

3)射频采样;

射频采样就是将ADC直接用在射频信号中。传统的采样是需要将输入信号通过一个下变频器件,将信号频率降低到一个较低的中频频率之后再做AD变换。射频采样是不需要将信号经过下变频,而直接对输入的射频信号进行AD变化,其在信号链路中的位置如下所示。

图片来源:ADI官网

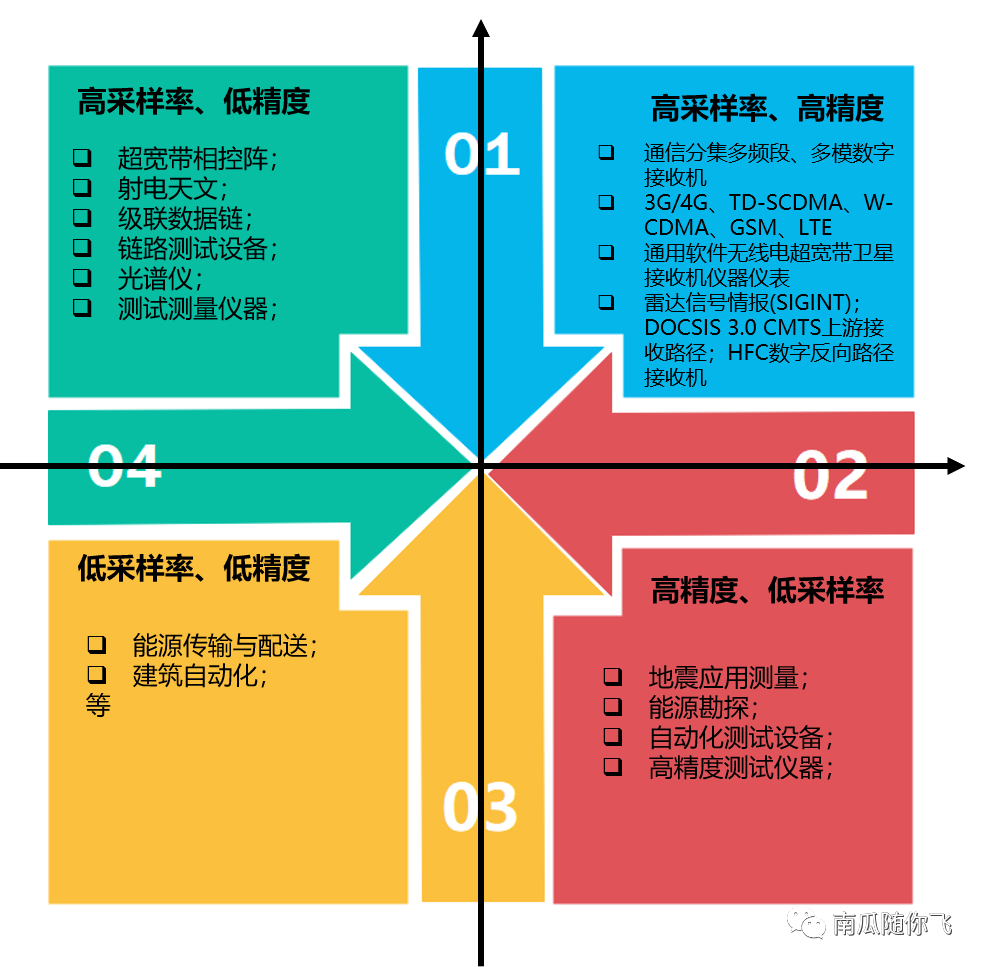

采样率和分辨率是两个相互矛盾的指标,当位数越高,需要采集、比较的数越多,相应的ADC芯片的架构越复杂,比较器越多,运行的时间越长,速度越慢。

二、ADC分类

ADC按照工作原理可以大致分为两大类:

- 直接转换型ADC:将输入电压信号直接转换为数字代码,不需要经过中间任何变量;

- 间接转换型ADC:将输入电压信号转变成某种中间变量(时间、频率、脉冲宽度等),然后再将这个中间变量转换成数字代码输出;

按照采样定理的原理可以分为两种:

- 奈奎斯特采样ADC:采样率=2信号最高频率;

- 过采样ADC:采样率>2信号最高频率;

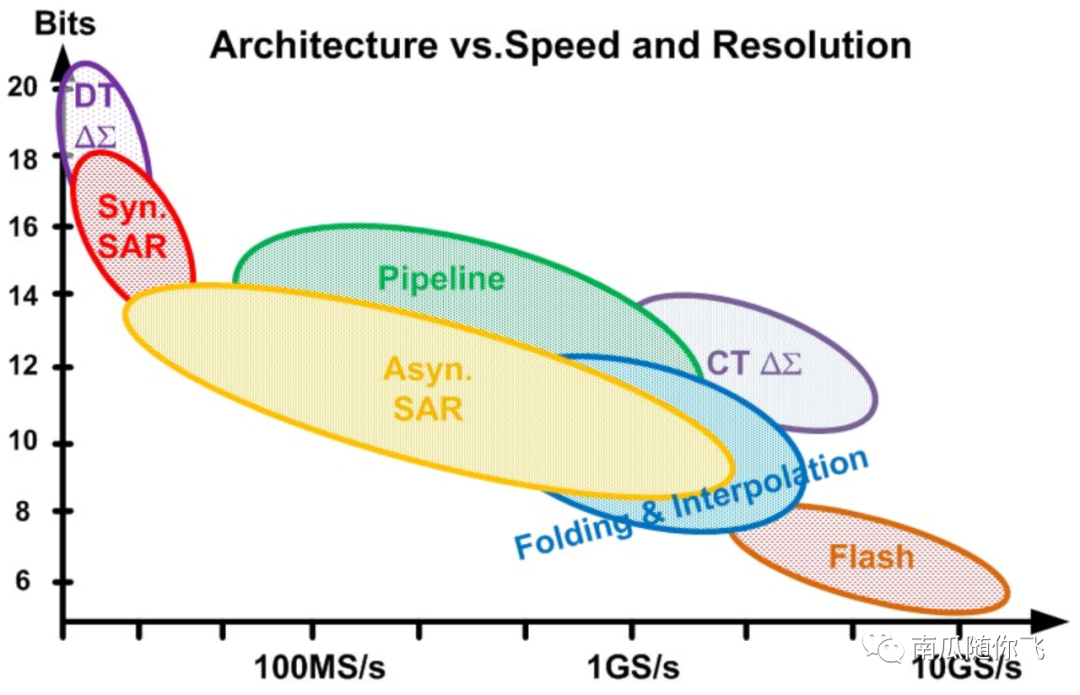

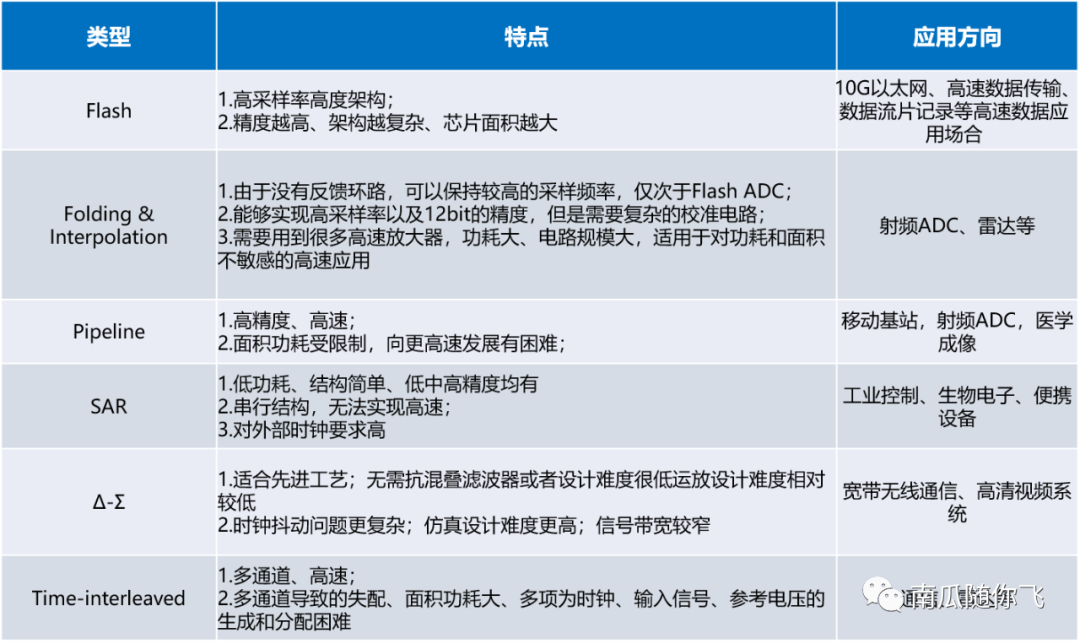

按照不同的精度和采样速率可以分为Δ-Σ 、SAR、Flash、Folding & Interpolation、Pipeline等不同种类。这几种不同的ADC之间精度和速率的关系如下图所示:

图片来源:髙速低功耗逐次逼近式ADC研究与实现

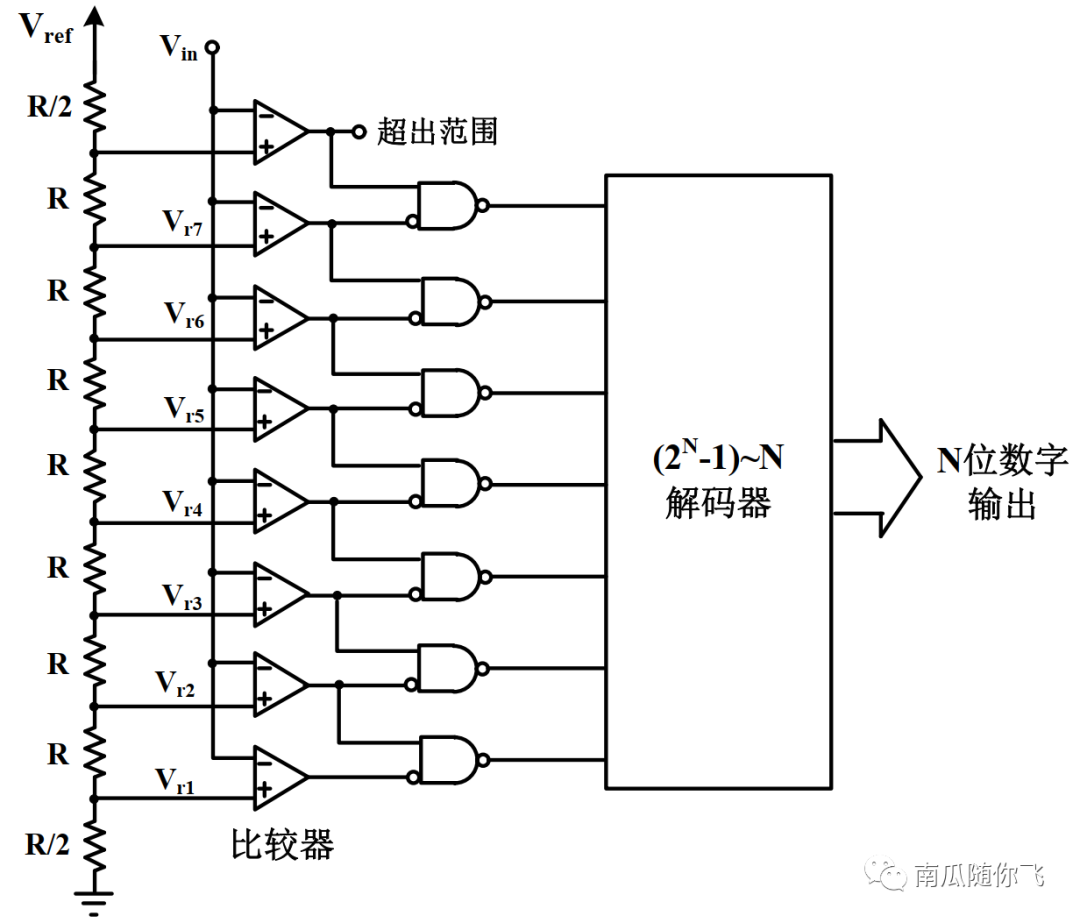

1.Flash

Flash是一种高速的ADC架构,是目前成熟的采样速率最高的ADC架构。其架构如下图所示。

图片来源:高精度Σ-Δ ADC设计

从它的结构中可以得到,输入电压Vin与参考电压Vref是分别同时接入到不同的输入端口进行对比,也就是输入信号是被多个端口并行处理,执行一次运算只需要一个时钟周期。

也正是因为其并行运算的架构使得其无法做到很高的分辨率(既高位数)。上图显示的是一个3位,用到了7个比较器。一个N位的ADC采用Flash架构,需要2的N次方-1个比较器,因此增加一位,就需要增加2的N次方个比较器。这也是导致Flash无法做到太高精度的主要原因,精度越高、架构越复杂、芯片面积越大。

另外,比较器对于输入电压都是并联的,呈现十分大的输入电容,需要用很大的功率来驱动这一类ADC,对于功率、功耗等方面也受限制。

目前Flash最高可用位数为8bit,高于8bit之后就需要采用其他架构。8bit的Flash ADC速率可以达到1GS/s,6bit的ADC可以达到12GS/s。

Flash ADC除了可以作为单片使用,还经常在Pipeline ADC、Δ-Σ ADC、SAR ADC中作为子ADC使用。

2. Folding & Interpolation

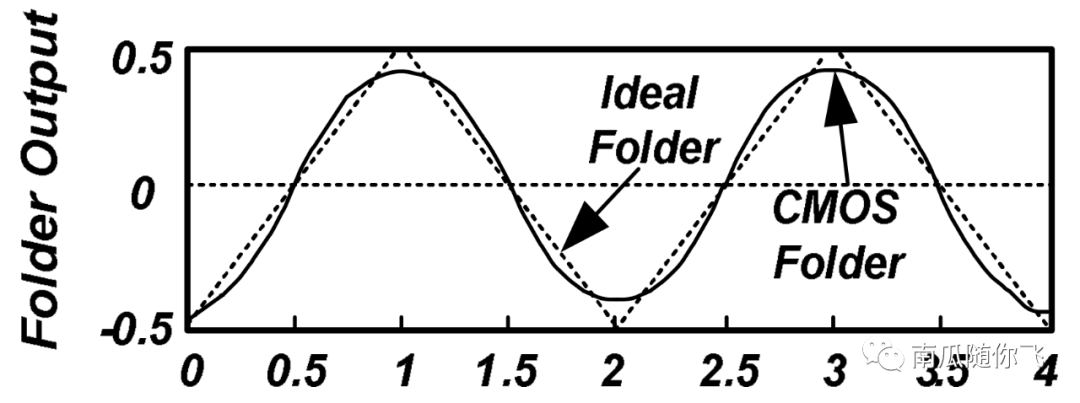

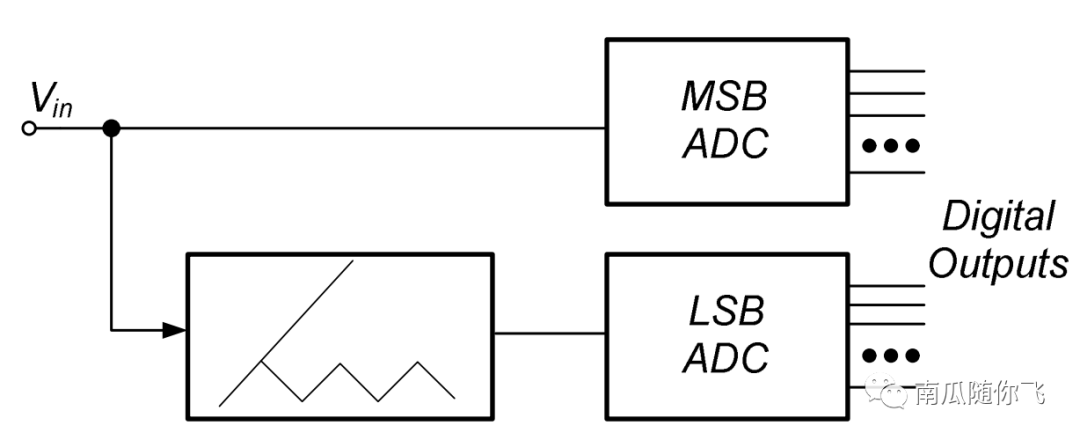

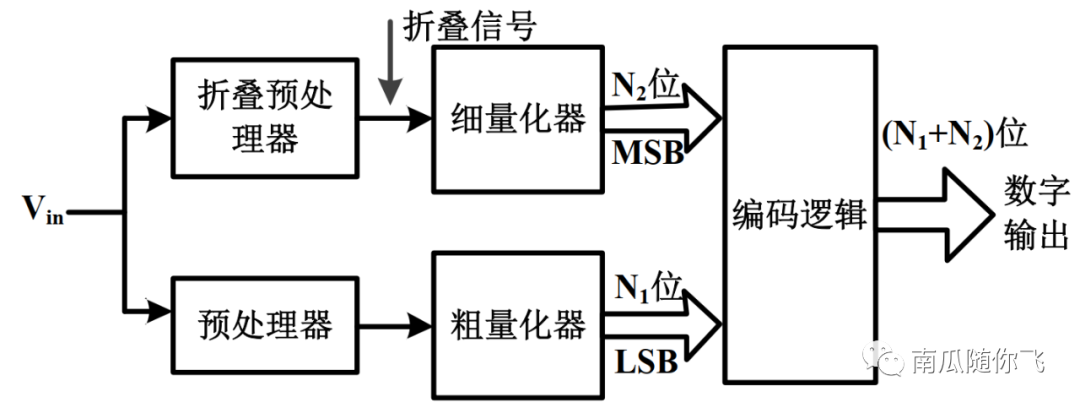

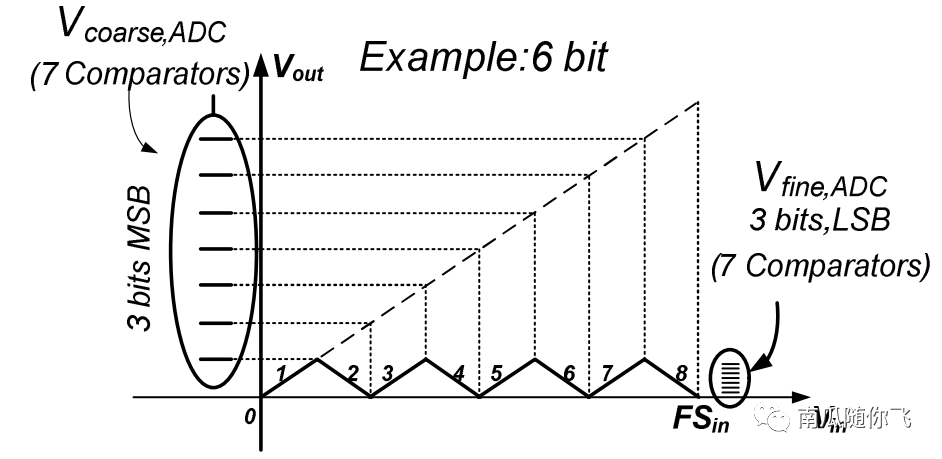

Folding & Interpolation,折叠内插式ADC,其核心思想是划区、分段再组合。

划区:将输入型号进行折叠划区,如下图所示,输入信号被划分为四个区域,然后分别对不同区段进行量化。

分段:将输入电压分成两路信号,一路直接通过低精度Flash ADC,进行粗量化,得到高位的MSB;另外一路通过折叠放大器分成小的量化区间再进行细量化。

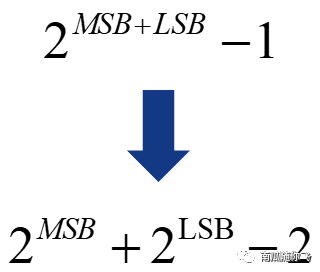

组合:将两路信号对应的MSB+LSB位数组合成一个完整的精度表示。

采用Folding& Interpolation架构,会相比与采用Full Flash架构用到的比较器少很多。系统架构简化。同时其处理的精度得到提高、采样的速率相对较高。

Folding & Interpolation ADC的特点如下:

- 由于没有反馈环路,可以保持较高的采样频率,仅次于Flash ADC;

- 能够实现高采样率以及12bit的精度,但是需要复杂的校准电路;

- 需要用到很多高速放大器,功耗大、电路规模大,适用于对功耗和面积不敏感的高速应用;

3.Pipeline

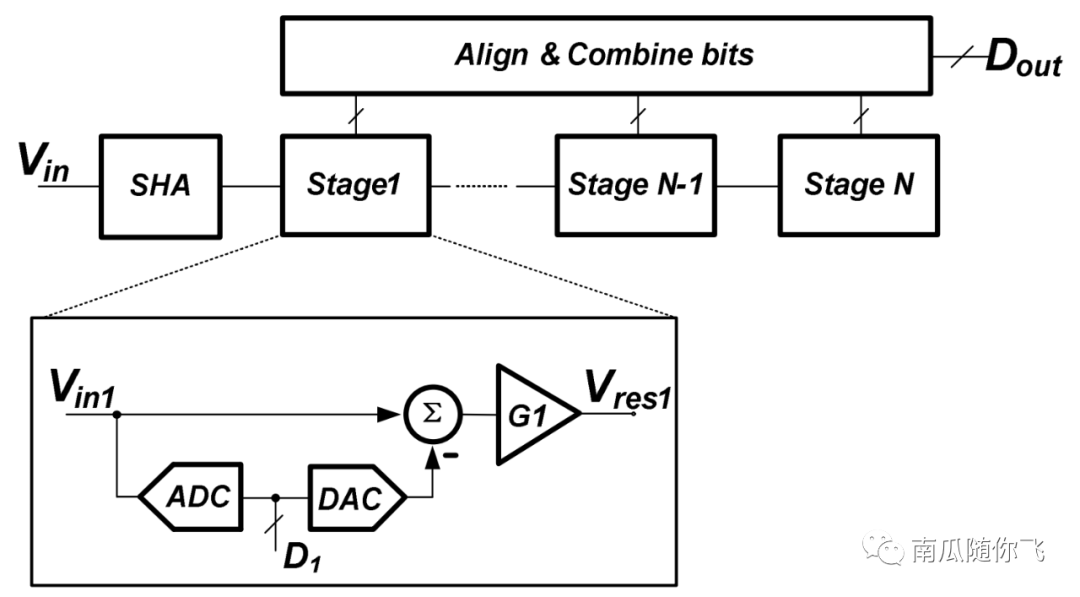

Pipeline ADC,流水线式ADC架构。正如其名字一样,采用了类似于加工产线上的流水线生产流程和原理,将输入信号进行分段处理,然后逐个传输到每个ADC完成对应的采样+量化的工作,最后拼接输出。与Folding & Interpolation结构不同,Pipeline将输入信号在时间和空间上都进行分段了,前者仅在空间上分段,然后并行处理两路信号。

上图所示为Pipeline ADC的基本结构,可以看到输入信号需要经过不同的流水线节点Stage。每一个Stage中包含了一个子ADC、一个子DAC以及一个残差放大器(Residue Amplifier)。每一个Stage在前半个时钟内接收信号完成一次采样,然后在后半个时钟内由子ADC完成量化,输出量化结果D。

Pipeline ADC需要保证分段的量化在半个周期内完成,同时其不想Flash或者Folding & Interpolation同时完成所有位数的量化,因此其在高精度的基础上还可以保留一定的速度优势,但是相对于Flash和Folding & Interpolation高速来说稍显不足。

主要的优点:

- 高精度:其每级的残差放大可以抑制后级的误差,类似于射频链路中的级联噪声作用,提高了整体的精度;分段结构能够更灵活的对每一位进行校准,能够达到10-16bit;

- 高速:目前可实现单通道250MS/s+16bit,1.5GS/s+12bit的性能,适用于基站、通信、雷达等应用;

- 量化校准方便,能够通过灵活的校准算法提高精度、降低功耗;

主要的缺点:

- 随着工艺制程不断降低,晶体管的沟道效应增强,本征增益下降,放大器难以保持高增益,因此限制了残差放大器的精度;

- 高速、高精度需要更高的功耗和更大的面积,系统的架构也越发复杂,进一步导致功耗和面积的增大;

- 流水线式的固有数据延迟特点使得其无法实时输出当前量化结构,使其无法朝向更高速的应用场景发展;

高速Pipeline ADC发展趋势:

- 低功耗:功耗是限制传统Pipeline ADC发展的瓶颈问题,降低功耗也是研制高速、高精度Pipeline ADC的重要方向;

- 混合结构:为实现兼容高速、高精度、低功耗的特点,往往采用了混合结构实现,例如Pipeline+SAR可以实现低功耗和中高精度;Pipeline+ Δ-Σ ,可以实现高精度;

4.SAR

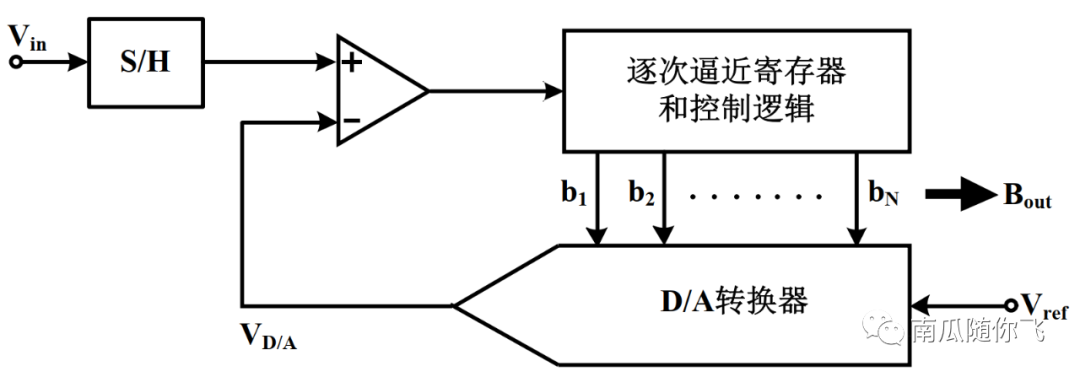

Successive-approximation Register,SAR,逐次逼近式ADC。传统架构的SAR式时间同步取样,主要优势低功耗、结构简单、低中高精度均有,能够应用在工业控制、生物电子、便携设备中。

由采样+保持电路、逐次逼近寄存器、控制逻辑、DAC构成。举个列子来说明其工作流程和原理。

由采样+保持电路、逐次逼近寄存器、控制逻辑、DAC构成。举个列子来说明其工作流程和原理。

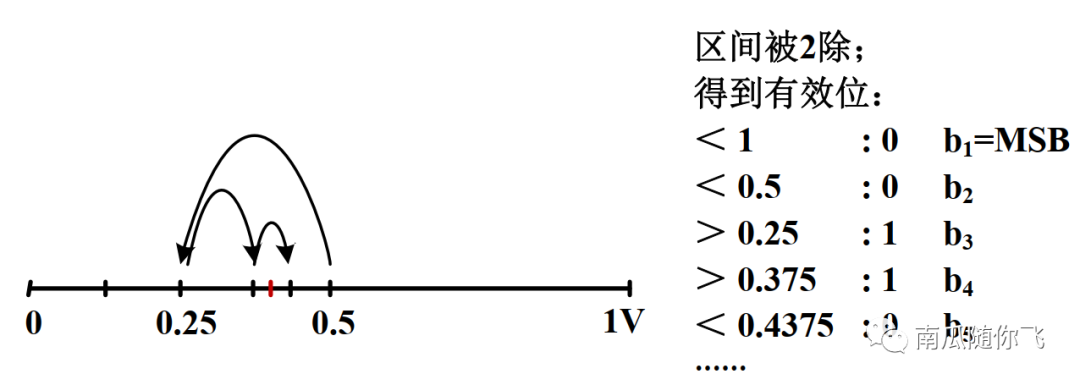

假设输入电压是0.4V(参考电压为1V)。

1)第一次比较,0.4V <1V,最高有效位为0;

2)二分区间,输入电压与<0.5V 相比较,再次产生一个0;

3)二分区间,输入电压>0.25V 相比较,有效位为1;

4)1作为控制信号,将比较值从0.25V 选为0.375V,而不是0.125V;

5)比较程序继续N 次,得到N 位输出。

主要缺点:

- 逐次逼近是串行结构,使得其无法实现高速采样;

- 同步时钟电路控制,模块之间传递信号存在较多等待;

- 基于分频的时钟控制,外部时钟频率要高于内部采样时钟N+1倍或以上;

采用异步时钟的结构能够有效解决其关键问题:外部时钟无需N+1倍于内部采样时钟,降低了对外部时钟速度和精度的要求,简化了电路设计;异步时钟下电路模块在传递信号的时候没有等待问题,时间延迟小。因此异步时钟的SAR ADC是目前SAR ADC的主流解决方案。

5.Δ-Σ

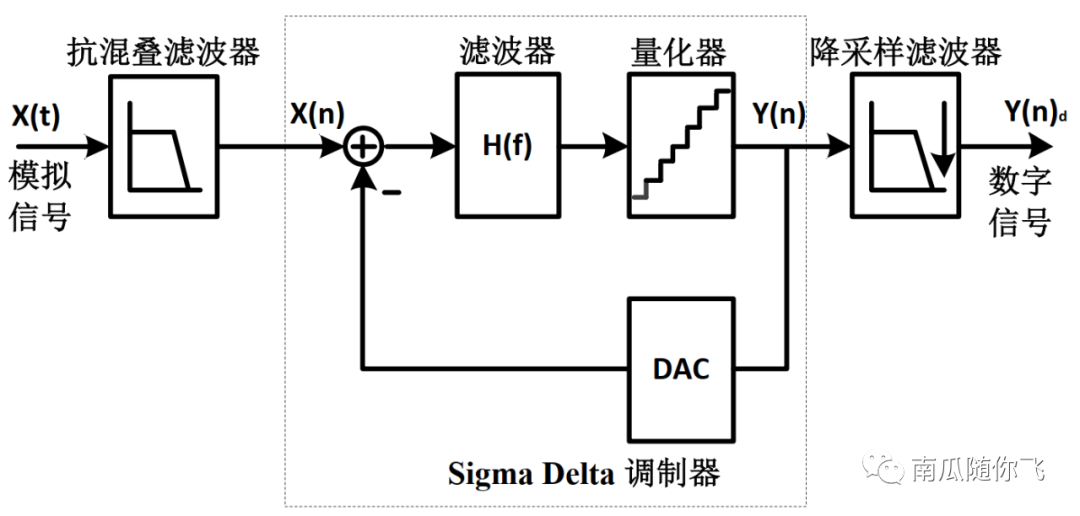

Δ-Σ ,增量累加ADC。与其他几种ADC不同,这一类ADC成为过采样ADC,其采样率远大于2倍信号最高频率,根据应用场合的不同范围从20-1000。其他结构如下图所示。

信号的采样率越高,噪声对信号信息的影响就越小,SNR也随着过采样率的提高而提高,因此ADC的分辨率也会提高。Δ-Σ 就是通过速度来换取高分辨的一种架构。其采样进度能够达到24bit。

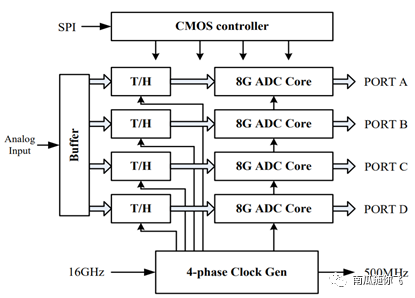

6. Time-interleaved

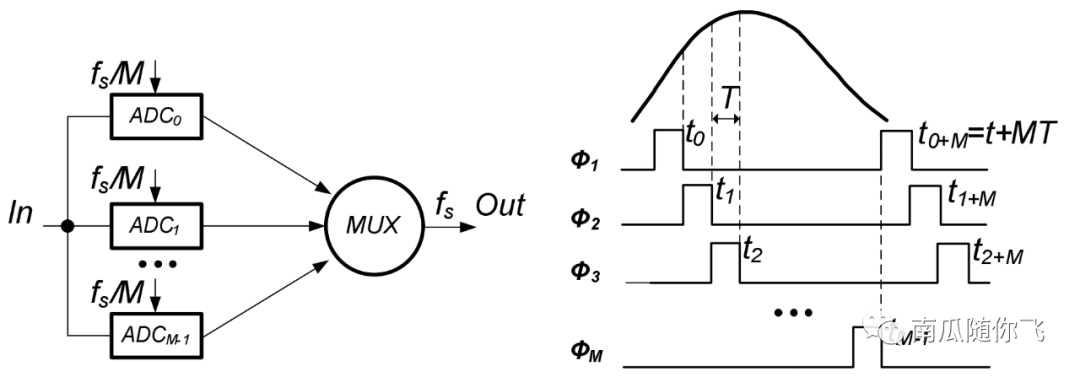

Time-interleaved,时间交织ADC。时间交织的核心思想是两点:多路处理+时钟交织。其结构如下图所示。M个采样率为fs/M的ADC阶梯式并行采样。在第一个采样时钟信号到达的时候把第一个采样值传递个ADC0,第二个时钟周期来到的时候把第二个采样值传递给ADC1,这样类推。

Time-interleaved ADC是目前实现多通道ADC采样的方案,是实现高速ADC的重要方案。但是面临由多通道导致的失配、面积功耗大、多项为时钟、输入信号、参考电压的生成和分配困难等问题。

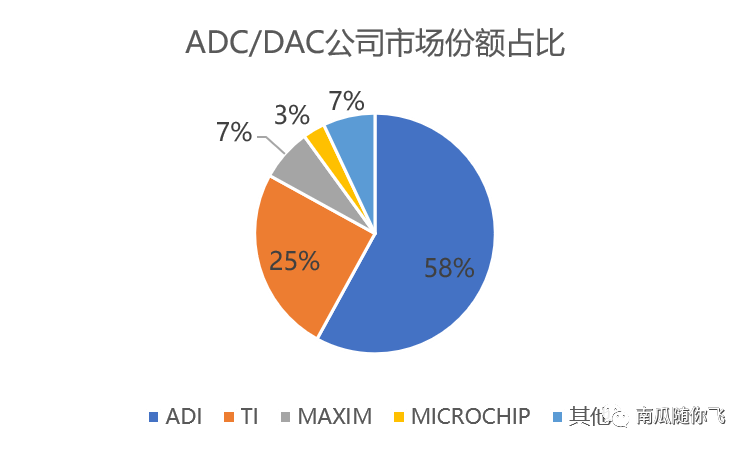

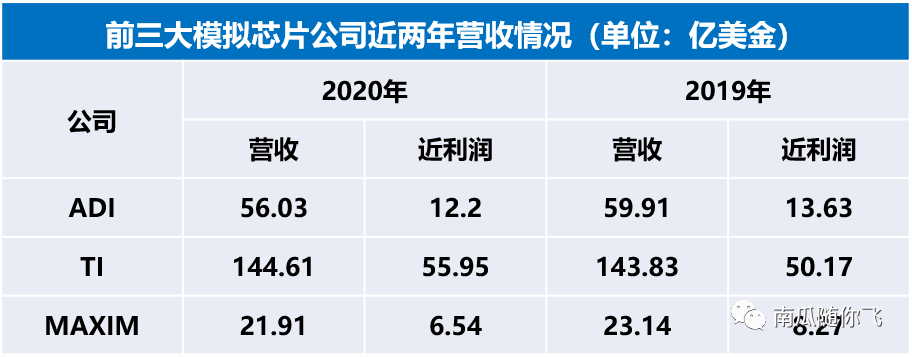

三、海外龙头占据市场主要份额

根据相关数据统计显示,在2018年全球的ADC/DAC市场分别别ADI、TI、MAXIM、MICROCHIP等国外企业垄断。

国企的企业起步时间早、技术迭代时间长、技术积累深厚,同时具有IDM模式或者先进工艺实现途径。通过早期的技术突破,以及后期的不断的研发投入形成了技术、市场双壁垒。

从产业链的角度来看,国外的公司从芯片的设计、制造、封测到最后的销售形成了完整技术、市场双重覆盖。有很强的自主可控能力。

从技术角度来看,国外的公司早期实现了技术突破,通过不断注入研发资金,形成产品良性迭代。研制出了具有高性能的高速、高精度的产品,应用领域覆盖了工业控制、卫星、通信、汽车、消费电子等各个领域。

从公司的规模角度来看,国外的公司通过长期的市场垄断,形成了市场的护城河。营收规模大,公司团队都已经达到一定的体量。

在ADC方向,TI、ADI、MAXIM三家占了国内高速、高精度ADC/DAC市场的95%,其中ADI占58%,TI占25%。

1.ADI

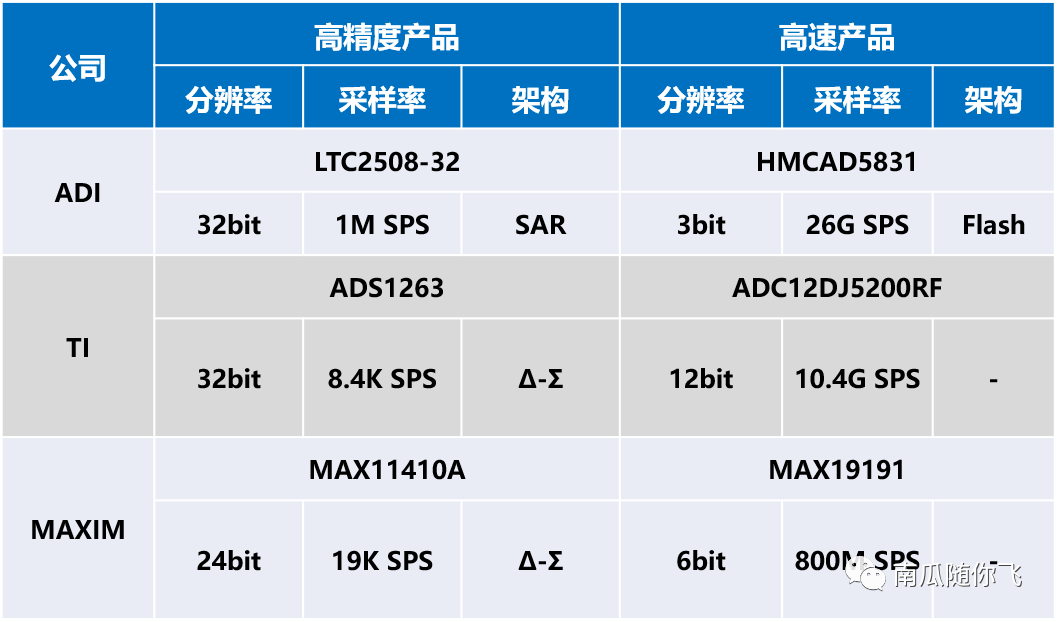

1)目前在高速ADC方面的产品有511款,采样率从10M-26G SPS均有覆盖,对应的分辨率从3-24bit。

ADI最新推出的几款产品,ADC最高采样率达到4G SPS,分辨率最高为16bit。

- AD9081是一款混合型号前端芯片,集成了4个16-bit,12G SPS采样率的射频DAC,4个12bit,4G SPS采样率的射频ADC。可用于无线通信架构、微波点对点E波段通信、5G毫米波、宽带通信系统、相控阵雷达和电子战、电子测试测量系统;

- AD9083,采用了Continuous time Δ-Σ 架构(连续时间增量累加),支持125M信号带宽,2G SPS采样率,低功耗设计。主要用于毫米波成像、相控阵波束成形、多通道宽带接收机、电子测量等;

- AD9699,14bit,3G SPS采样率。针对宽带信号的直接采样使用,信号带宽可达5G。可用于:分集多频带和多模数字接收机、3G/4G, TD-SCDMA, W-CDMA, GSM, LTE, LTE-A、电子测试测量系统、相控阵雷达和电子战、DOCSIS 3.0 CNTS上行接收路径、HFC数字变换路径接收机、LiDAR;

最高采样率的型号为HMCAD5831

- 3bit,26G SPS采样率,采用Full Flash超低延时架构,支持20GHz的输入带宽。

- 主要针对超过宽带相控阵、射电天文、级联数据链、链路诊断测试设备、光谱仪等领域。

目前在高精度ADC方面的产品有677款,分辨率从8-32bit ,采样率从6.8-160M SPS均有覆盖。

2)其中最新款产品分别为ADAQ4001、AD4695、AD4696、AD7606C-16、ADAQ23875、AD4680、AD4681、AD4682、AD4683、AD7606C-18、ADAQ4003、AD4114、AD4115、AD7383、ADUM7702。

最高精度的型号:分辨率为32bit的LTC2508-32和最新高精度的型号:分辨率为24bit的AD4115。

- LTC2508-32:

a.一款低噪声、低功耗、高性能的32bit、最大采样率1M SPS ADC;

b.采用了双输出的SAR ADC架构,功耗为24mW(1Msps);

c.主要应用在地震探测、能源勘探、自动化测试设备、高准确度仪表等领域

- AD4115:

a.一款低功耗、低噪声、24bit的ADC;

b.±10V的输入电压,采用了Δ-Σ 架构;

c.主要应用在PLC控制和分布式控制系统模块、测试仪器设备

2. TI

1)目前TI关于高速ADC的产品共有351款,采样率从1M-10.4G SPS,分辨率从7-18bit均有覆盖。

新产品:ADC09QJ1300-Q1、ADC3563、ADC3663、ADC3583、ADC3683、ADC3664\\、DC12DJ5200RF、ADC3643、ADC3660、ADC12SJ1600-Q1、ADC12DJ1600-Q1、ADC12QJ1600-Q1、ADC3541。

- ADC12DJ5200RF:最高采样率

a.是一款射频采样千兆采样模数转换器 (ADC),可对从直流到 10GHz 以上的输入频率进行直接采样;

b.目前TI单通道采样率最高的产品。10.4G SPS 单通道或 5.2G SPS 双通道、 12 bit、功耗4W;

c.JESD204C串行数据接口,最多16个串行通道,最大通道速率:17.16Gbps;

d.主要应用:示波器和宽带数字转换器、通信测试仪(802.11ad,5G)、电子战(信号情报、电子情报)、卫星通信 (SATCOM) 、射频采样软件定义无线电 (SDR) 、光谱测量

2)目前TI关于高精度ADC的产品共有556款,分辨率从4.5-32bit,采样率从0.015K SPS-8MSPS均有覆盖。

新产品:ADS7067、ADS127L11、ADS131M02 、ADS131M03、ADS125H01、ADS131B04-Q1、ADS7038-Q1、ADS7138-Q1、ADS8686S、ADS9226

- ADS1263:最高精度产品

a.集成PGA、电压基准和内部故障监视器的低噪声、低漂移、8.4kSPS、32bit Δ-Σ ADC。ADS1263 集成有一个 24 bit辅助 Δ-Σ ADC,专用于后台测量;

b.主要应用:高分辨率可编程逻辑控制器 (PLC) 、温度、压力测量、秤重天平和应力计数字转换器、面板仪表、图表记录器、分析仪器

3. MAXIM

- 目前MAXIM高速ADC的产品共有48款,采样率从7.5-800M SPS,分辨率从6-16bit,均有覆盖。

- MAX19191:最高速产品

a.双通道,6bit,采样率800M SPS,fin≈200MHz时SNR为37dB,输出为LVDS接口,功耗2.6W;

b.主要应用:VSAT 接收机、WLANs、测试仪器、通信系统;

2)目前MAXIM关于高精度ADC的产品共有424款,分辨率从8-24bit,采样率从0.0016K SPS-3MSPS均有覆盖。

- MAX11410A:最新的高精度ADC

a.多通道、低功耗、24bit、19K SPS采样率,采用了Δ-Σ架构;3ppm的INL

b.输入端集成了一个低噪声可变成增益放大器,使得该ADC能够驱动高阻抗源

c.主要应用:传感器测量、便携仪器、电阻电桥测量

从上述三家龙头企业来看,他们的产品种类齐全、覆盖范围广、指标性能领先,并且针对不同的应用领域提供了不同芯片。用户可以根据具体的需求去选择及时快速的货架产品,一定程度上避免了定制化带来的时间、研发以及应用方面的成本问题。同时,产品的性能决定了它们在用户市场上的地位,高精度和高速的ADC已经经过多轮的技术迭代形成稳定的性能,保持了业界高水平。

四、国产厂商悄然升起,逐步崭露头角

近年受到美国贸易制裁,对于关键的、核心的、高性能的芯片应用愈发受限。在ADC/DAC领域,国内企业也逐步浮出水面,进入市场参与的公司也正在增加。大致可以将国内的企业划分为三个类型:

- 国家级的骨干研究院所:航天772所(时代民芯)、中电24所、中电55所、中科院微电子所、吉芯科技(中国电科声光电公司)、中科芯集成电路股份有限公司(中电58 所);

- 国内高校创业企业、上市公司:苏州云芯微、苏州迅芯微电子、苏州纳芯微、北京昆腾微电子、上海贝邻、芯海科技;

- 海归企业团队:深圳灵矽微、上海韬润半导体、苏州思瑞浦、上海冶精微电子、上海类比半导体、北京核心互联;

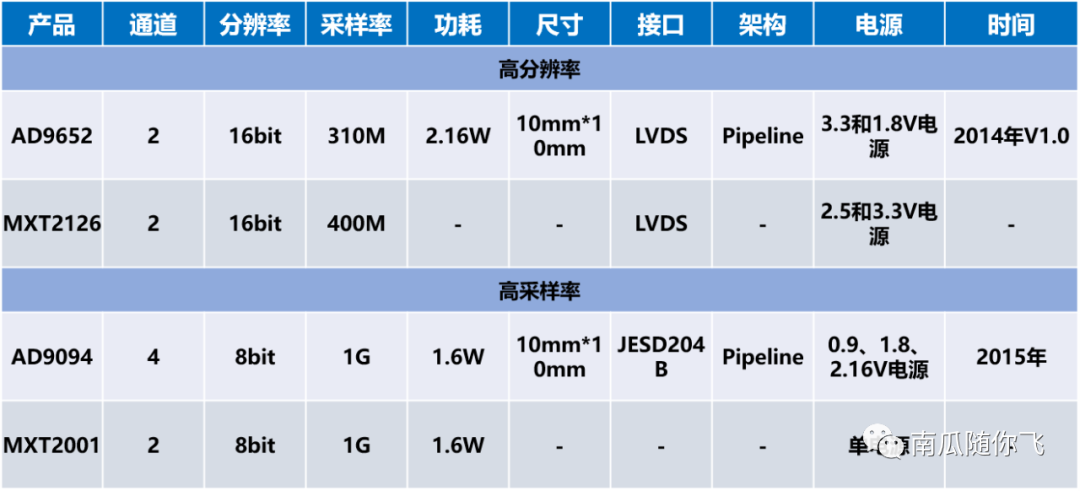

1. 航天772所-时代民芯

成立于2005年11月,是由中国航天时代电子公司和航天电子技术股份有限公司(原长征火箭技术股份有限公司)重组航天微电子资源而成立的股份有限责任公司,现为航天电子技术股份有限公司的全资子公司。专业从事集成电路设计、开发、生产(不包括晶圆加工)和服务;半导体二极管、三极管和MEMS惯性器件的设计、开发、生产和服务。

公司在ADC方向的主要产品如下所示:

ADC最高精度16bit,最高采样率1G SPS,与国外企业相比,产品属于中低端。高速产品采样率仅突破1G。从产品性能来看,公司的产品方向主打高16bit分辨率低采样率、8bit分辨率高采样率。属于中等分辨率低采样率,低分辨率中等采样率的产品范围。

以ADI的产品为对标分析,公司的产品性能指标相对于ADI在2014年左右的产品性能相当,按照摩尔定律来看,相差了2-3代。

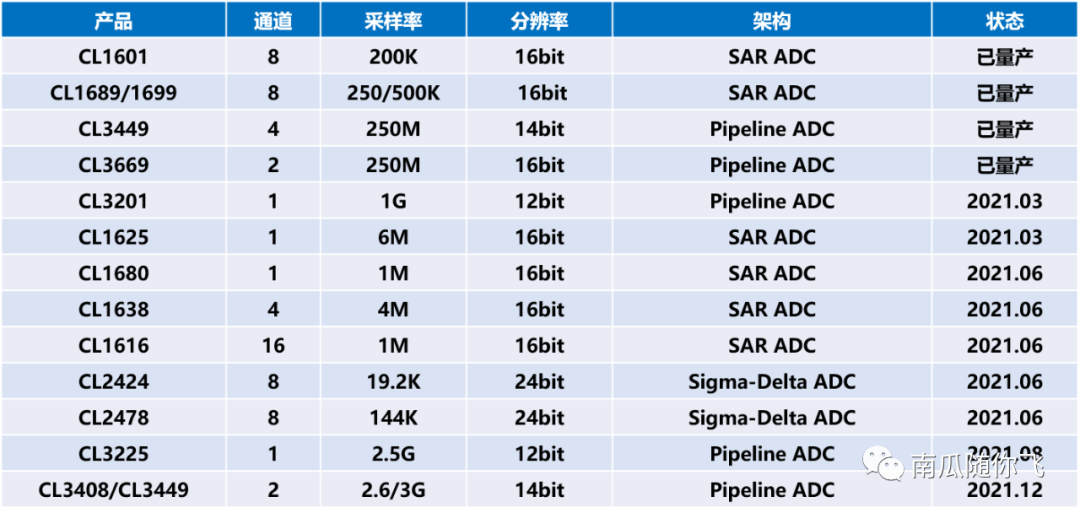

2.苏州云芯微

2010年5月创办于江苏省昆山市花桥经济开发区,致力于高速高精度数模混合集成电路芯片(ADC/DAC)和集成中射频、模拟、数字功能等集成芯片(SOC&SIP)的设计、开发、生产及销售。产品涵盖高性能模数转换芯片(ADC),数模转换芯片(DAC),直接数字式频率合成芯片(DDS) ,正交数字上变频芯片(QDUC)、多频多模射频收发芯片(SOC、SIP)等多个门类。公司产品广泛用于无线通信、遥测遥控等领域。

从公司目前已经发布的产品来看,分辨率最高16bit,采样率最高达到250M SPS。相对于国外公司来说相差很大,从高速、高精度来定义仍然具有很大的差距。

3. 苏州迅芯微电子

成立于2013年,以集成电路及软硬件系统的设计、研发、销售为一体。团队在超高速数据转换器(ADC/DAC)芯片、高速串并/并串转换(DEMUX/MUX)芯片,以及微波单片集成电路(MMIC)领域具有丰富的研究经验。

AAD06S032G,采用Si基工艺,4路交织技术,子ADC采用Folding & Interpolation架构,可对输入信号做6bit转换,功耗10W。主要针对高速数据采集、宽带通信以及示波器等方向。

从公司的发布的产品来看,迅芯微在ADC方向注重于高速ADC,采用多路交织技术,集成Folding & Interpolation子ADC,用多路架构提高采样率,实现高速。但是缺乏高精度的ADC产品。

4. 苏州纳芯微

成立于2013年,专注于围绕各个应用场景进行产品开发,由传感器信号调理ASIC芯片出发,向前后端拓展了集成式传感器芯片、隔离与接口芯片、驱动与采样芯片,形成了信号感知、系统互联与功率驱动的产品布局。

在ADC方向主要产品为隔离ADC,高性能隔离Δ-Σ调制器,可在隔离高压下将模拟信号转化为数字信号进行传输。发布产品仅有两款:NSi1306M25、NSi1306M05。

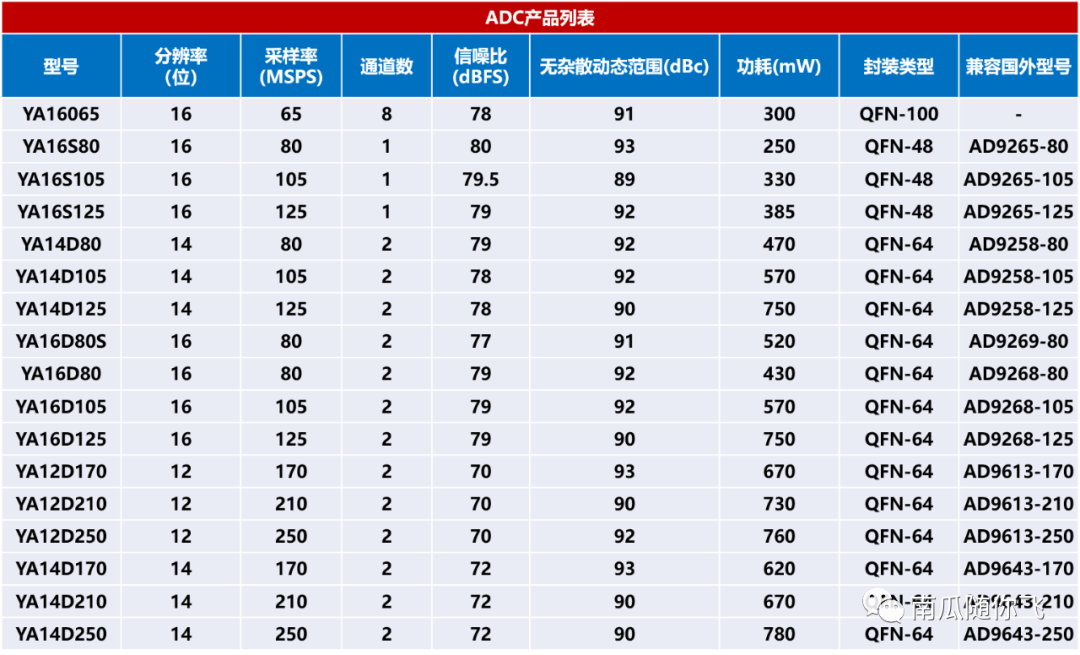

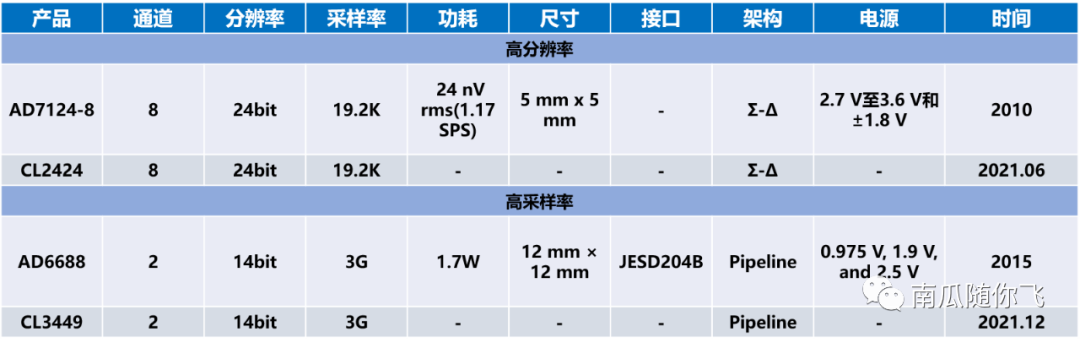

5.北京核心互联

公司创立于2017 年,团队来自于清华北大以及北美名校,有着多年国内外大厂的工作经历,如AMD、英伟达、华为等。2018 年获得5000 万元个人投资者种子轮投资。公司同时掌握ADC/DAC、时钟芯片、运算放大器、高速接口和RISC-V IP 等多项技术,具备信号链全链芯片及相关IP 设计研发能力。目前公司主要芯片产品为高速高精度ADC,工业级MCU以及高性能RISC-V+AI+DSP异构SoC。

从公司已发布的产品可以看到,公司是少数能够研制24bit高精度ADC的企业,同时其在高速ADC方面也能够达到3G采样率,同时保持14bit的分辨率。

在高速、高精度ADC方面具有较明显的技术优势,属于国内技术领先的民营企业。

对比ADI的相关产品,相对比于国外的产品平均落后了5-10年。

6. 重庆吉芯科技

重庆吉芯科技成立于2019年06月21日,是中国电科声光电公司旗下的公司。公司在2021年发布两款高性能多通道16位ADC系列产品——GAD3642ME和GAD3681ME,分别是4通道16位250MSPS ADC和8通道16位125MSPS ADC。

两款产品具有多通道、低功耗、高速串行数据输出(最高6.4Gbps)等特点,可满足医疗成像、高速成像、无线电接收机以及便携设备等应用领域需求。

其中,GAD3642ME采样率最高可达250MSPS,采用JESD204B高速串口输出(最高6.4Gbps),使用时间交织结构,专门针对低功耗(支持独立关闭内部各通道功能)、小尺寸和使用灵活性设计开发。GAD3681ME采样率最高可达125MSPS,采用JESD204B高速串口输出(最高6.4Gbps),专门针对低功耗(支持独立关闭内部各通道功能)、小尺寸和使用灵活性设计开发。

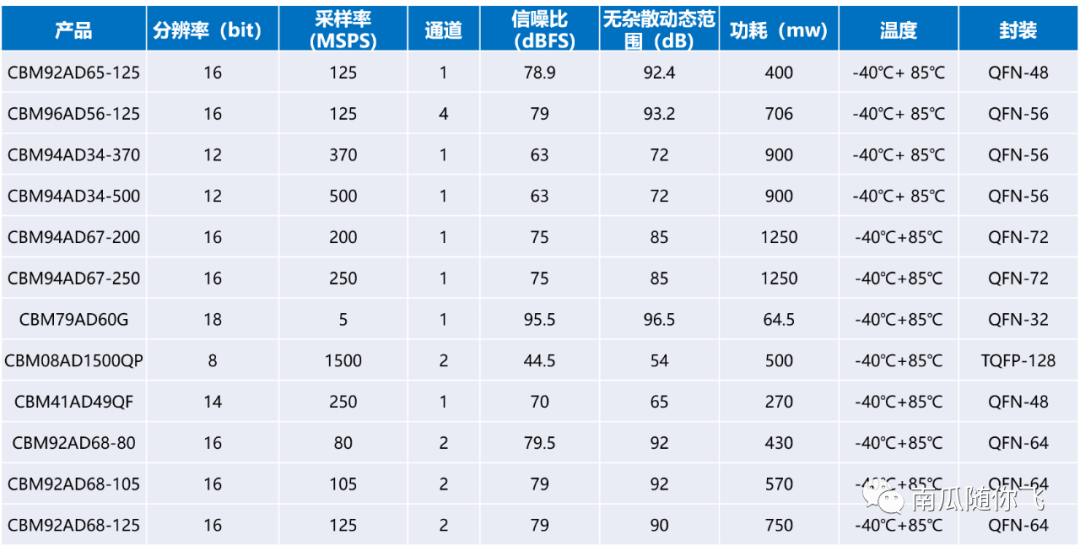

7.上海贝岭

上海贝岭(600171)成立于1988年,是集成电路设计企业,提供模拟和数模混合集成电路及系统解决方案。公司专注于集成电路芯片设计和产品应用开发,是国内集成电路产品主要供应商之一。重点发展消费类和工控类两大产品板块业务,公司集成电路产品业务细分为电源管理、智能计量及 SoC、非挥发存储器、功率器件和高速高精度 ADC 等 5 大产品领域,主要目标市场为电表、手机、液晶电视及平板显示、机顶盒等各类工业及消费电子产品。

从贝岭官网中可以看出贝岭主要生产14Bit与16Bit的ADC芯片,主要用于电量采集,常用的型号有:

高速模数转换器(高速ADC),该系列产品包括双通道高中频ADC (80MSPS -125MSPS)、四通道高频ADC(125MSPS)。

8. 芯海科技

芯海科技(688595)成立于2003年9月,专注于高精度ADC、高可靠性MCU、测量算法以及AIOT整体解决方案的研发设计。公司2020年营收3.628亿,净利润9034.53万;2019年营收2.584亿,净利润4295.61万。

图片来源:芯海科技2020年报

目前在ADC方面的产品仅有高精度ADC,9款产品。

- 多款产品初次发布时间在2014年,并于2018年进行修正,对其中相关指标进行校正设计;

- 标称分辨率为24bit,实际使用有效分辨率在19.5-22bit变动;

- 对应采样率最高仅为1.28K SPS(与SPS相同)

总体性能与ADI、TI、MAXIM相差几个数量级,从发展代数来看,相当于2-3代之前的产品。

9.芯佰微

成立于2014年,目前已达3大类100余款,已经研发的主要产品为放大器、接口电路、电源管理,时间数字转换器、DAC数模转换、ADC模数转换等。产品广泛应用于手持移动终端、消费类电子产品、个人电脑及周边,网络、电信设备、医疗设备、办公设备、汽车电子及工业控制设备等领域。

五、关于ADC行业的几点看法

- ADC属于模拟芯片中的一类,模拟芯片相对于数字芯片设计难度更大,对于研发人员技术能力要求要更高。模拟芯片一类的平均学习成长时间是数字芯片的3-5倍,需要非常扎实的学科基础,相较于数字芯片来说,对于工具的依赖较小。因此这是一个技术人才优先的领域,技术团队中如果缺少经验丰富的研发力量,对于公司的产品研发将会造成严重的滞后、成本增加甚至是白白投入;

- 相对于数字芯片追求摩尔定律极限的加工工艺(追求5-7nm的先进工艺),模拟芯片的制程一般采用0.18um、0.13um,以及28nm的工艺。成熟的工艺有助于提高产品良率,同时在客户端更愿意使用成熟的工艺。新的工艺需要经过长时间的工程验证、使用反馈迭代才能够很好的进入市场;

- ADC属于基础的、核心的、关键的元器件级芯片,对于性能的要求是应用的首要原则。虽然各个厂家都会有各种不同性能的产品,但是在对应的使用领域中,性能的绝对优势对市场的占据会起到决定性的因素。这里面包括了一些基本的性能参数、尺寸、功耗等等。因此,能够通过技术领先做到产品突破的公司,将会赢得差异化的竞争,在推广市场的时候也会有很大的优势;

- 国内外企业之间差距巨大:国外企业起步时间早、技术能力强,加上国外企业在IDM模式中能够很好的做好技术迭代、成本控制,早期形成了很高的护城河,占据了国内大部分的市场;国内企业起步时间晚,但是在大环境的影响下也有很多企业逐步走入市场的视野,通过政策利好、人员积累不断追赶着。总体来说,在中低端产品方向目前国内与国外企业的产品至少相差了2-3代,在高端市场的差距更大。

- 从市场占比方向来看,目前国外三巨头TI、ADI、MAXIM占了90%的市场,高端市场国内企业几乎找不到影子。在国产替代的大背景下,国内的ADC市场空间巨大。

- 中低端切入,逐步过渡到高端:国内企业需要从难度较小,国产替代容易,客户接受度大的中低端市场切入,做好技术、资金的双重积累,实现企业自身研发力量、研发资金的滚动迭代升级,再朝向高端市场逐步迈入。如果一开始来进入高端市场,将会直接与三巨头面对面竞争,从技术、市场、客户应用等方向会有非常大的难度;

- 国家引导,资金持续助力:想要突破国外ADC的垄断限制,需要不断的政策引导、资金注入。ADC一定是一个需要不断升级、迭代才能够做到突破的,这个过程需要大量资金的投入用来维持企业投入研发力量。

-

高性能ADC/DAC芯片供应商奇历士与世强先进达成合作2023-11-28 2512

-

ADC模拟电路皇冠上的明珠(2)2023-07-03 2121

-

余承东:操作系统是软件行业皇冠上的明珠 当前的创新研究还非常有挑战2023-02-25 1222

-

终于搞懂模拟电路中的ADC!12023-02-20 21041

-

半导体材料皇冠上的明珠,迎来国产化机遇.zip2023-01-13 549

-

详解类比半导体16~32bits Σ-Δ ADC全系产品2022-12-09 5162

-

公布!中国制造业皇冠上的明珠:28家传感器单项冠军企业!2022-10-30 1747

-

高性能与低功耗兼具的ADC产品汇聚2021-12-20 3825

-

高精度,快速度!盘点国产化浪潮下的国内ADC厂商们2021-08-19 89496

-

摘取装备制造业“皇冠上的明珠”2019-06-12 3700

全部0条评论

快来发表一下你的评论吧 !