ADC模拟电路皇冠上的明珠(2)

电子说

描述

一、28nm工艺下的ADC

随着无线通信向高速、宽带方向发展,对于无线信号接收机提出了越来越高的要求。特别是在电子战领域、信号情报侦察应用方向对于高带宽、小型化、轻型化以及低功率(Size, Weight and Power: SWaP)ADC的需求更加迫切。65nm制程的ADC在向更高速的、高带宽的数据变换器扩展的时候遇到了一些固有的障碍:工艺制程、带宽限制等方面。28nm的先进工艺制程正在打破这个界限,从而使得原本一些无法考虑实现的接收机的架构或者性能得到很大的促进。接下来我们就从几个角度来看看28nm的ADC具有哪些应用的优势。

在宽带的雷达电子战领域中,系统的研发人员在设计高性能、低SWaP的接收机的时候会面临很多挑战。在接收机中ADC扮演了一个非常重要的角色,以至于有时候会因为ADC的性能而采用不同的接收机架构。ADC的性能参数包括了采样率、带宽、分辨率,都会影响射频RF链路以及后端的DSP。高采样率和带宽能够一次性捕捉分析宽带的RF信号,同时降低扫描时间、保持更高分辨率,能够提高分析的性能,降低虚警概率。

28nm的晶体管能够降低寄生的栅极电容,实现更快的开关速度,同时仅需要很低的功率来驱动即可。28nm的工艺不仅能够提高单个晶体管的性能,同时能够在单位面积上集成更多的晶体管以获得更优异的信号处理能力。28nm工艺下实现的高采样率ADC在电子战方向中的信号情报侦察、电子战防御(Electronic Protect:EP)、电子战支援(ElectronicSupport:ES)应用需求十分迫切。

采用28nm的工艺,同时也带给了半导体厂商更多的设计思路。能够在ADC中集成更多的混合信号处理单元以保证在同等的SWaP条件下提高ADC的性能。例如NCO(Numerically Controlled Oscillators:数控振荡器,其作用类似于本振源,提供一个混频信号)和DDC(Digital Downconverters:数字下变频器,其作用是将高频信号在数字域进行下变频,降低频率以便于后续处理)。

在提高了采样率和带宽之后面临着有大量的数据吞吐(GSPS),在研发过程中就需要找到能够与之相匹配的数据接口传输数据。目前市场上很多28nm的ADC数据输出速率已经超过了10Gbps,采用的接口通常为JESD204B,但是引入由串行和解串路由Gbps带来的JESD相关电路布局、信号完整性分析方面的问题,进一步提升设计研发的难度。可以通过集成NCO、DDC实现降采样,变换到基带,结合数字滤波能够保持很高速的数据输出速率。所以集成NCO、DDC以实现降采样是保持高速数据的有效方法。另外一方面,如果JESD204B输出的数据没有经过降采样,一直维持在非常高速的传输下,所需要的功率、产生的功耗将会非常大。因此,采用抽取滤波的方式能够降低功耗。

总的来说,在电子战领域对于集成了NCO、DDC的高速的、高带宽、高分辨率的ADC的应用能够极大的提升接收机的性能,先进工艺制程的ADC能够有效的解决低SWaP与高速数据之间的矛盾关系,为实现高性能的接收机提供了有效的解决方案。

二、ADC芯片的工艺方案

在ADC方向上,CMOS工艺已经成为一种主流的工艺实现方式。CMOS工艺具有较低的寄生电容、电感以及电阻效应,是Δ-Σ、SAR以及Pipeline架构(基于开关电容型的电路)的ADC的主要实现工艺。

BiCMOS的工艺成本较高,在一些性能要求较高的模拟前端需要使用。例如混频器、采样保持电路、输入放大器以及高精度参考电压都利用双极型实现的,其他的功能电路利用CMOS实现。

GaAs在ADC方面的应用主要在6-8bit,采样率大于1G的flash架构中使用。这一类的ADC通常成本、功率都比较高,但是市场较为小。

三、ADC对接收机系统架构的影响

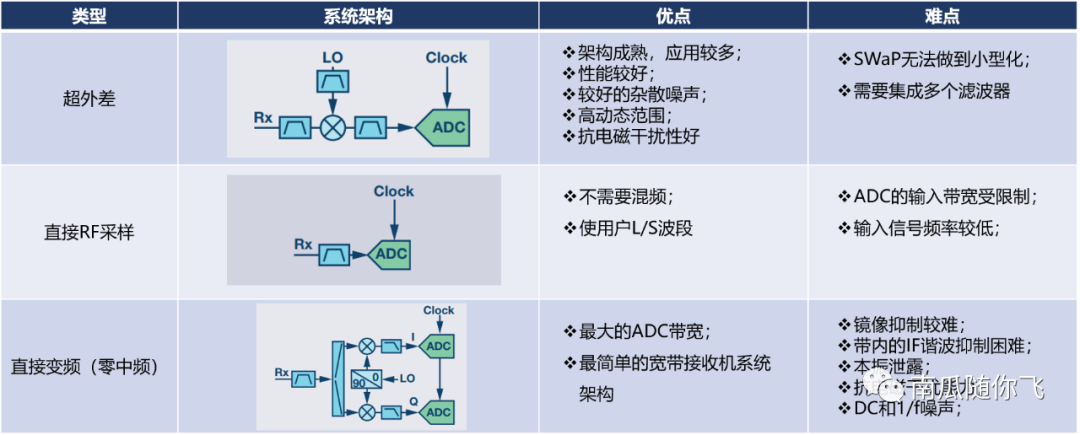

接收机按照不同的RF信号变频处理方式可以分为三种:超外差式、直接RF采样、直接下变频(零中频)。

1.超外差接收机

RF信号通过与本振信号混频后变到中频IF,在进行后入处理。超外差式接收机应用的时间早、架构较为成熟、性能表现稳定。通常会采用较高的IF频率结合滤波器来抑制镜像频率干扰,或者通过多级下变频器逐级变频实现镜频抑制。

同架构图中可以看出来,超外差接收机的架构较为复杂。通常需要很大的驱动功率以及电路布局才能够获得较合适的工作带宽,与现在系统对低SWaP的需求相违背。

2. 超外差接收机

直接RF采样是市场和研发人员一直在追求的接收机架构。目前主要的障碍在直接射频采样的速度、大输入带宽与ADC的速率之间不匹配的问题。这也是限制这类架构向更高频段发展的重要原因。

目前主要应用还是集中在较高的奈奎斯特频段(采样率与信号频率之间的关系)的L/S波段的接收机中。下一步随着ADC的发展,将会逐步向C-band,X-band扩展。

3. 零中频

零中频是对数据变换带宽利用效率最高的架构。ADC通常工作在第一奈奎斯特采样区间。信号通过与正交的本振信号混频过后形成两路I/Q正交信号,然后分别进行ADC。

主要的难点在于保持较好的I/Q信号的平衡,以获得较好的镜像抑制、本振泄露以及直流偏移等。目前通过集成整个零中频信号链路并结合数字校准技术已经解决了这些问题,进一步打开了该类型接收机的应用市场,在多种应用场合已经逐步采用这种类型的接收机。

以超外差结构为例,介绍ADC对其架构的影响。通常在低速的ADC时代,因为工作带宽与输入频率的比例很大,使得通过单级下变频直接做低频滤波较为困难,很多微波接收机通常都是采用多级变频的模式。

图片来源:ADI官网

随着ADC的采样率、输入带宽的提高,使得单级变频架构逐步进入应用。典型的框架如下图所示:

图片来源:ADI官网

接收链路最开始是一个低噪放,但是在有些特定的应用领域,例如面对大功率电子对抗设备会在前端加载一个限幅器降低输入功率的幅度。随后经过带通滤波、放大、低通滤波、下变频、低通滤波、放大,在进入ADC之前需要做一个抗混叠滤波,滤除掉一些干扰、杂散以及谐波信号。信号进入ADC进行数据变换,后续的电路都是围绕着ADC进行设计的。

有没有必要在每一种接收机或者设备中都采用高速、高精度的ADC?这是需要结合具体的应用场景来讨论的。当面对的是宽带、高速的信号,典型的就是电子电子对抗、大数据量通信、频谱测试测量等,高速的ADC就显得必不可少。从系统架构方面来看,能够有效降低系统复杂程度;从性能方面来说,能够提高高吞吐量的数据采集变换。同时结合不同的接收机架构,在面对射频直采和零中频的应用,高性能的ADC的需求更加迫切,大带宽、高采样率等特点有助于研发人员采用紧凑的系统架构;超外差结构中,高性能的ADC也能够在一定程度上降低系统的复杂程度,但是如果需要考虑到性价比、成本方面的问题,如果能够采用成本较低的多级变频的方案+性能适合的ADC来实现也是一种方案。

综上,考虑到架构性价比、成本、性能优势以及复杂程度,虽然不是每一种接收机架构都需要用到高速、高分辨率的ADC,但是高速的ADC能够极大的降低接收机的架构复杂度、提高性能,这也正式复合了系统朝着低SWaP方向发展的技术和应用趋势。

四、ADC中的NCO和DDC如何工作的

首先我们先来回答几个问题。

- 为什么要做降采样?

降采样,顾名思义,降低采样率。为什么要做降采样,那是因为之前用了采样率过高的ADC。那为啥不直接用低采样率的ADC就可以了吗?

用高速的ADC,个人觉得主要原因如下:

第一、因为接收和采集的信号是宽带、高速的信号,需要采集的信号往往是一些宽带的信号,必要时候还需要在一个很宽的频段内进行扫频。所以为了实现匹配,采用高速的ADC是必备的。

第二、可以降低对射频前端模拟滤波器的要求。滤波器的设计难点在于尽量需要一个很好的矩形系数,又希望只采用几阶就能够实现,这之间就存在trade-off的设计。模拟滤波器通带越窄、带外衰减越陡峭、衰减越大,需要的滤波器阶数就越多,滤波器的设计成本就越高,有时甚至无法研制出来。所以采用宽带的滤波器结合逐级滤波,进来的信号量也就很大,就需要用到高速的ADC了。

为什么又需要再后面降低采样率呢?主要是因为ADC过后,需要将数据传输到后续的DSP、FPGA等基带数字信号处理电路进行分析处理,这中间存在一个速率匹配的问题。高速的ADC不经过降采样出来的信号速率通常很高,DSP的时钟速率是无法跟上的,所以需要经过降采样处理。第二,ADC的数据输出接口如果一直保持在很高的数据传输速率下,其需要驱动的功率就很高,功耗也提高,芯片的功耗、散热是一个非常大的问题。

- 为什么是先滤波、再降采样而不是先降采样再滤波?

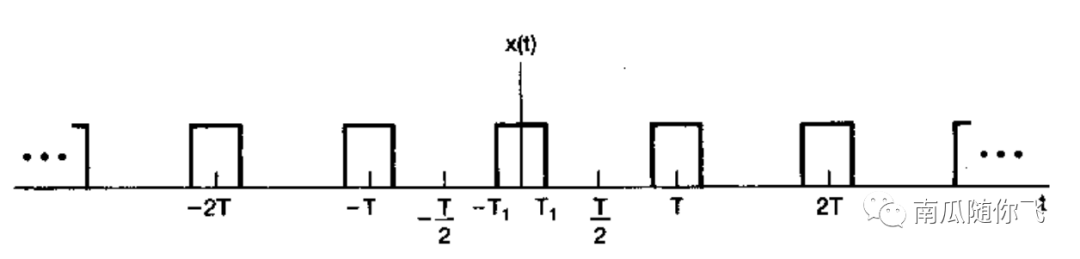

在信号与系统中表述过,时域离散对应频域周期、时域连续对应频域离散。(信号与系统第三章和第四章)。直观的就是时域上的周期方波通过傅里叶变换成为了频域上的Sinc函数,如下图。

图片来源:《信号与系统》

假设,输入信号如下左边是时域,右边是频域:

图片来源:《信号与系统》

经过ADC采样之后,时域和频域分别变成如下,时域离散对应频域周期。

图片来源:《信号与系统》

降采样过程实际上是在对AD采样之后的数据进行抽取滤波,即是间隔一定的数量进行抽过去采样,如下图所示左所示。这个过程可以看作是对已经在频域上周期了的信号又做了一次周期,结果如下图右边所示。此时的信号在频域上面已经发生了混叠。

所以,需要在采样之后滤波,然后再进行降采样,就可以得到没有混叠的信号。

回到NCO和DDC。NCO:Numerical ControlOscillator,数控振荡器,集成在DDC中,用于为输入信号分成I/Q信号提供本振混频。

DDC:Digital Downconverters,数字下变频器,进行降采样工作。

图片来源:ADI官网

信号经过采样之后进入DDC,首先通过NCO,与NCO提供的两路相位相差90°的信号进行混频,从一个较高频率变换到较低频率;然后通过滤波器进行抽过去滤波;接着选择性的是否进行一个放大;最后输出两路I/Q信号。

图片来源:ADI官网

DDC中的滤波器一般来说采用级联方式首先的,分为三级,按照顺序分别是梳状滤波器(CIC),第二级半带滤波器(HBF),第三级有限冲激响应滤波器(FIR)。

CIC是一种不需要进行乘除法运算的滤波器,只需要加减法和移位运算就可以。乘法运算是一种非常耗费资源的运算,因为实际上在数字计算中本质上是没有乘法运算的,还是通过加减法结合移位运算进行的。乘法运算实质上是一堆加减法+移位运算的集合。在提出CIC之前都是直接用乘法运算进行一级滤波的,成本很高,同时运算速率有限。采用了CIC能够很好的将高频速率降低,同时修复带内平坦度,为后面两级滤波设计降低了难度。

HBF作为第二级滤波器,运算量是FIR的一半。

FIR低通滤波器,它的作用是对经过抽取滤波后的波形进行整形,因为经过抽取滤波之后,仍然会有一部分波形处于有效频带之外,故需要低通滤波器将这部分带外波形除去,剩下带内的信号提供给后端的 DSP 处理。

-

高性能ADC/DAC芯片供应商奇历士与世强先进达成合作2023-11-28 2517

-

ADC模拟电路皇冠上的明珠(1)2023-07-03 5903

-

余承东:操作系统是软件行业皇冠上的明珠 当前的创新研究还非常有挑战2023-02-25 1222

-

终于搞懂模拟电路中的ADC!12023-02-20 21048

-

半导体材料皇冠上的明珠,迎来国产化机遇.zip2023-01-13 551

-

详解类比半导体16~32bits Σ-Δ ADC全系产品2022-12-09 5163

-

公布!中国制造业皇冠上的明珠:28家传感器单项冠军企业!2022-10-30 1750

-

高性能与低功耗兼具的ADC产品汇聚2021-12-20 3825

-

高精度,快速度!盘点国产化浪潮下的国内ADC厂商们2021-08-19 89512

-

摘取装备制造业“皇冠上的明珠”2019-06-12 3701

全部0条评论

快来发表一下你的评论吧 !