时序分析的基本概念

描述

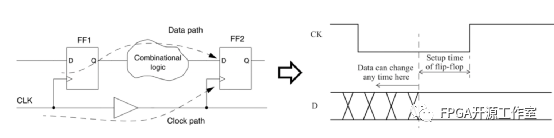

1 setup time

Setup time (建立时间)是数据信号(D)在时钟事件(这里以时钟上升沿为例)发生之前保持稳定的最小时间。以便时钟可靠地对数据进行采样。适用于同步电路,如触发器(flip-flop)。

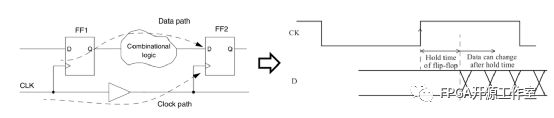

2 hold time

Hold time (保持时间) 是数据信号(D) 在时钟事件(这里以时钟上升沿为例)发生之后保持稳定的最小时间。

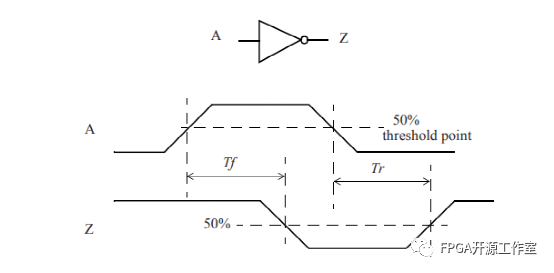

3 Propagation Delay

信号传播延时(Propagation Delay),以反相器(Inverter)为例,A输入信号变化(0-1的50%)为开始,到Z输出信号变化(1-0的50%)所需的时间称为Tf, A输入信号变化(1-0的50%)为开始,到Z输出信号变化(0-1的50%)所需的时间称为Tr。

Output fall delay (Tf)

Output rise delay (Tr)

# Threshold point of an input falling edge: input_threshold_pct_fall : 50.0; # Threshold point of an input rising edge: input_threshold_pct_rise : 50.0; # Threshold point of an output falling edge: output_threshold_pct_fall : 50.0; # Threshold point of an output rising edge: output_threshold_pct_rise : 50.0;

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

时序分析基本概念解析2023-08-08 2220

-

时序分析基本概念介绍<wire load model>2023-07-07 2271

-

时序分析基本概念介绍—Timing Arc2023-07-06 5969

-

时序分析基本概念介绍<Skew>2023-07-05 5631

-

时序分析基本概念介绍<Latency>2023-07-04 4891

-

介绍时序分析的基本概念lookup table2023-07-03 2918

-

静态时序分析的基本概念和方法2023-06-28 2661

-

FPGA设计中时序分析的基本概念2022-03-18 4545

-

时序分析基本概念2021-05-06 2040

-

时序分析基本概念介绍2019-05-14 6528

-

时序分析基本概念介绍——时序库Lib,除了这些你还想知道什么?2017-12-15 14059

-

时序分析基本概念——STA概述简析2017-12-14 31542

全部0条评论

快来发表一下你的评论吧 !