fpga设计流程包含哪几个部分

描述

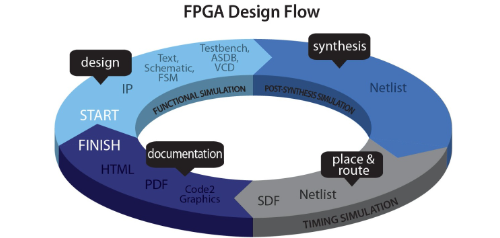

FPGA是一种可编程芯片,因此FPGA的设计方法包括硬件设计和软件设计两部分。硬件包括FPGA芯片电路、存储器、输入输出接口电路等器件。软件是对应的VHDL程序和VerilogHDL程序。FPGA采用自上而下的设计方法,从系统级设计开始,然后逐渐分为二级单元和三级单元,直到知道基本逻辑单元或IP核可以直接操作。通常,设计过程包含以下步骤:

1.功能定义/设备选择

在FPGA设计项目开始之前,必须有系统功能的定义和模块的划分。此外,根据任务要求,如系统功能和复杂性,工作速度与电线的资源、成本和分配性应保持平衡。然后选择正确的设计方案和适当的设备类型。

2.Design输入

设计输入包括原理图输入和硬件描述语言输入。原理图输入直观,但不容易仿真。此外,它效率低下且难以维护。它不利于模块构建和重用。主要缺点是其便携性差。当芯片升级时,所有原理图都需要更改。硬件语言包括VHDL,VerilogHDL,SystemC等。硬件描述语言输入的共同特点是语言与芯片技术无关,有利于自上而下设计,便于分区和移植模块。它们具有良好的便携性,强大的逻辑描述和模拟功能。

3.功能仿真

功能仿真,也称为预仿真,用于在编译之前验证用户设计的电路的逻辑功能。此时,没有延迟信息,只有函数的初始检测。

4.合成

所谓综合,就是把上层抽象层次的描述转化为下层的描述。集成优化可以根据逻辑连接产生的分层设计平面,优化目标和要求,实现FPGA布局和布线软件。在当前级别,综合是将设计输入编译成一个逻辑连接网络表,该网络表由基本逻辑单元(如AND门、析取门、逆变器、RAM、触发器等)组合在一起。它不是一个真正的栅极电路。

5.Post合成模拟

仿真是为了检查合成结果是否与原始设计一致。在仿真中,当将合成生成的标准延迟文件去标记到合成仿真模型中时,可以估计栅极延迟的影响。但是,这一步无法估计线路的延迟,因此与布线后的实际情况仍有一定的差距,这不是很准确。

6.实现和布局路由

布局路由可以理解为使用实现工具将逻辑映射到目标设备结构的资源,以确定逻辑的最佳布局,并选择该逻辑以连接到连接到输入/输出功能的布线通道并生成适当的文件(诸如配置文件和相关报告)。实现方式是在特定FPGA芯片上配置合成生成的逻辑网络表。

7.时序模拟

时序仿真又称后仿真,是指将布局布线的时延信息标注回设计网络表,以检测是否存在任何时序不规则(即不满足时序约束或器件固有的时序规则,如建立时间、维护时间等)。时序仿真中包含的延迟信息是最完整和准确的,可以更好地反映芯片的实际运行情况。

8.板级仿真和验证

板级仿真主要用于高速电路设计。分析了高速系统的信号完整性、电磁干扰等特性,一般由第三方工具进行仿真和验证。

9.芯片编程与调试

设计的最后一步是芯片编程和调试。芯片编程是数据文件的生成(比特流文件/比特流生成)。然后将程序数据下载到FPGA芯片。逻辑分析仪是FPGA设计的主要调试工具。但是需要很多测试引脚,而且LA很昂贵。目前,主流FPGA芯片制造商都提供嵌入式在线逻辑分析仪。

-

一个成熟的PCBA设计通常包含哪几个方面?2024-05-07 1340

-

Linux中的进程包含哪几个段呢2021-12-23 1610

-

串口通信的硬件设计可以分为哪几个部分呢2021-12-14 2009

-

stm32的启动文件startup_stm32f10x_hd.s主要包含哪几个部分2021-11-29 1620

-

Switch的配置主要包含哪几个方面? Switch的配置流程是怎样的?2021-10-22 7850

-

IC的设计过程可分为哪几个部分2021-10-20 2273

-

STM32的闪存模块是由哪几个部分组成的2021-10-15 1923

-

工业控制机由哪几个部分组成2021-09-01 1837

-

射频电路设计与仿真包含哪几个步骤?2021-05-20 2424

-

DSP设计流程有哪几个步骤?2021-04-30 2529

-

学习FPGA要经历哪几个阶段?2021-04-08 2202

-

综合布线系统由哪几个部分组成2020-01-03 5023

-

学习FPGA主要用到altera的哪几个软件2013-08-27 2490

-

示波器的组成--示波器由哪几个部分组成的?2009-02-10 5623

全部0条评论

快来发表一下你的评论吧 !