总结一下在时序分析中的基本概念及基本术语

电子说

描述

01 发起沿和捕获沿

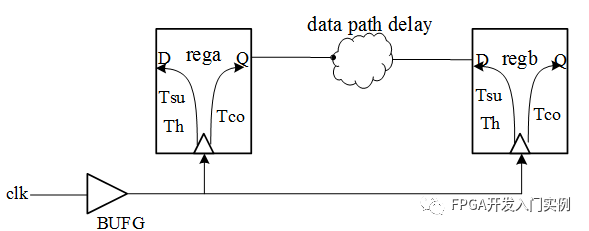

下图是一个经典时序分析模型,无论寄存器A与寄存器B是否在同一个芯片中,下列概念均适用。

02 时序路径

1、由器件A末端寄存器时钟到FPGA内部第一级数据端口

2、FPGA内部REGA时钟端口到REGB的数据端口

3、FPGA末级寄存器的时钟端口到器件B的输入数据端口

4、组合逻辑路径,FPGA输入端口到输出端口

1 源端时钟路径(红色)

2 数据路径(蓝色)

3 目的端时钟路径(黄色)

03 数据到达时间与数据需求时间

在clk时刻参考时间为0的条件下,进行数据到达时间、时钟到达时间、数据要求时间(建立时间)、数据要求时间(保持时间)的时序分析。

1.数据到达时间

数据到达时间=0+Tclka+Tco+Tdata

2.时钟到达时间

时钟到达时间=捕获沿+Tclkb

捕获沿=0+T(一个时钟周期)

时钟到达时间=T+Tclkb

3.数据要求时间-建立时间

数据要求到达时间=时钟到达时间-Tsu-setupuncertainty

=T+Tclkb-Tsu-setup uncertainty

setup uncertainty:时钟抖动造成的不确定时间。

4.数据要求时间-保持时间

数据要求保持时间=时钟到达时间+Th+hold uncertainty

=T+Tclkb+Th+hold uncertainty

hold uncertainty: 时钟抖动造成的不确定时间。

04 建立时间裕量与保持时间裕量

1.建立时间裕量

建立时间裕量=数据要求到达时间-数据到达时间

=T+Tclkb-Tsu-setupuncertainty -(Tclka+Tco+Tdata)

2.保持时间裕量

保持时间裕量=数据到达时间(新的)-数据要求保持时间

=Tclka+Tco+Tdata-Tclkb-Th-hold uncertainty

3.建立与保持时间裕量整合

建立时间裕量与保持时间裕量为正,则满足时序要求,如果时间裕量为负,则不满足时序要求。

建立时间裕量与保持时间裕量为正,则满足时序要求,如果时间裕量为负,则不满足时序要求。

系统时钟频率

Tlogic为代码导致的延时,Tnet为布线延时。

05 总结

1、发送沿通常为时序分析的参考时间点

2、通常,捕获沿=发送沿+1个时钟周期

3、建立时间与保持时间是由芯片工艺本身决定。提高系统时钟频率由决Tdata定。

-

时序分析基本概念介绍—花一样的“模式”2023-07-10 6381

-

时序分析基本概念介绍—Timing Arc2023-07-06 5951

-

时序分析Slew/Transition基本概念介绍2023-07-05 5775

-

介绍时序分析基本概念MMMC2023-07-04 4407

-

介绍时序分析的基本概念lookup table2023-07-03 2895

-

静态时序分析的基本概念和方法2023-06-28 2642

-

放大电路中反馈的基本概念及判断方法2023-03-10 8812

-

FPGA设计中时序分析的基本概念2022-03-18 4497

-

USB基本概念及从机编程方法介绍2021-11-08 1940

-

时序分析和时序约束的基本概念详细说明2021-01-08 1809

-

时间抖动的概念及其分析方法介绍2019-06-04 2736

-

详细介绍时序基本概念Timing arc2018-01-02 26093

-

时序分析中的一些基本概念2017-02-11 5171

-

天线的基本概念及制作2010-01-04 1662

全部0条评论

快来发表一下你的评论吧 !