EMI问题之串扰描述

EMC/EMI设计

1295人已加入

描述

串扰描述:

串扰特指印制线间,导线间,印制线到导线间、电缆组件、元件和其他遭受电磁场干扰的电子元件间不经意地发生电磁耦合,通常这些耦合回路包括PCB上的印制线。

这些不良的影响不仅与时钟和周期信号有关,而且还和其他重要的系统电路有关,如数据线、地址线、控制线、和I/O线都可能受串扰和耦合效应影响。时钟和周期信号是产生问题的主要原因,并且能导致其他区域的组件出现严重的功能性问题,如有客户遇到板子上的高频谐波,影响到2.4G通信问题。

串扰的表征是RF能量从干扰线耦合到被干扰线,而EMI 敏感电流也会将RF能量耦合到包括互连线的其他电路。

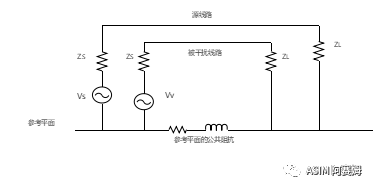

通常串扰需要有三条以上线路,如下图,其中两条线路承载有用的信号,第三条线路为参考导线,这条导线通过容性和感性耦合使得电路之间有交换(传递):

容性耦合通常是在一条印制线位于另一条上方时产生的,这种耦合是印制线和交叠区域之间距离的函数,通常主要有很短的交叠线条,就能发容性耦合。印制线物理上相互接近会产生感性耦合,这种耦合源于印制线上信号的切换电流产生的电磁场的扩张和收缩。

在平行布置的印制线上可以观察到两种形式的串扰:前向和后向。出现在被干扰线上的干扰信号位于干扰源的激励源处就称之为后向干扰,反之在被干扰线的接收端上观察到的干扰信号称之前向串扰:

为了避免串扰发生,在PCB 布局时需要注意以下几点:

1、将器件的逻辑系列按照功能分类,严格控制总线结构。

2、减小平行布线的线长。

3、对控制阻抗的印制线或富含谐波能量的印制线进行滤波处理。

4、避免相互平行的布线,在印制线间保持足够的间距减小感性耦合。

5、减小信号层到参考地的距离。

6、降低线条阻抗和驱动信号的电平

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

串扰如何影响信号完整性和EMI2025-08-25 10141

-

基于S参数的PCB串扰描述2019-07-08 1768

-

如何使用S参数描述PCB串扰2020-10-10 1011

-

EMI问题之串扰2023-06-26 1359

全部0条评论

快来发表一下你的评论吧 !