PCIe—Bar空间是怎么生效的?

电子说

描述

最近在研究cocotbext-pcie的实现,对于学习PCIe还是挺有帮助的,陆陆续续做个总结,有时间也会在SpinalHDL下实现类似的方针功能。

》抛砖

PCIe接口相对来讲还是打交道比较多的接口。无论是Intel还是Xilinx的IP也都接触到过。谈及PCIe,就不可避免地涉及Bar空间。当然厂商的IP还是包装的可以的,我们直接配置就行。但在使用时关于Bar空间的配置,往往牵涉到这么几个概念:

- IO/Mem

- Prefetchable

- 32位/64位

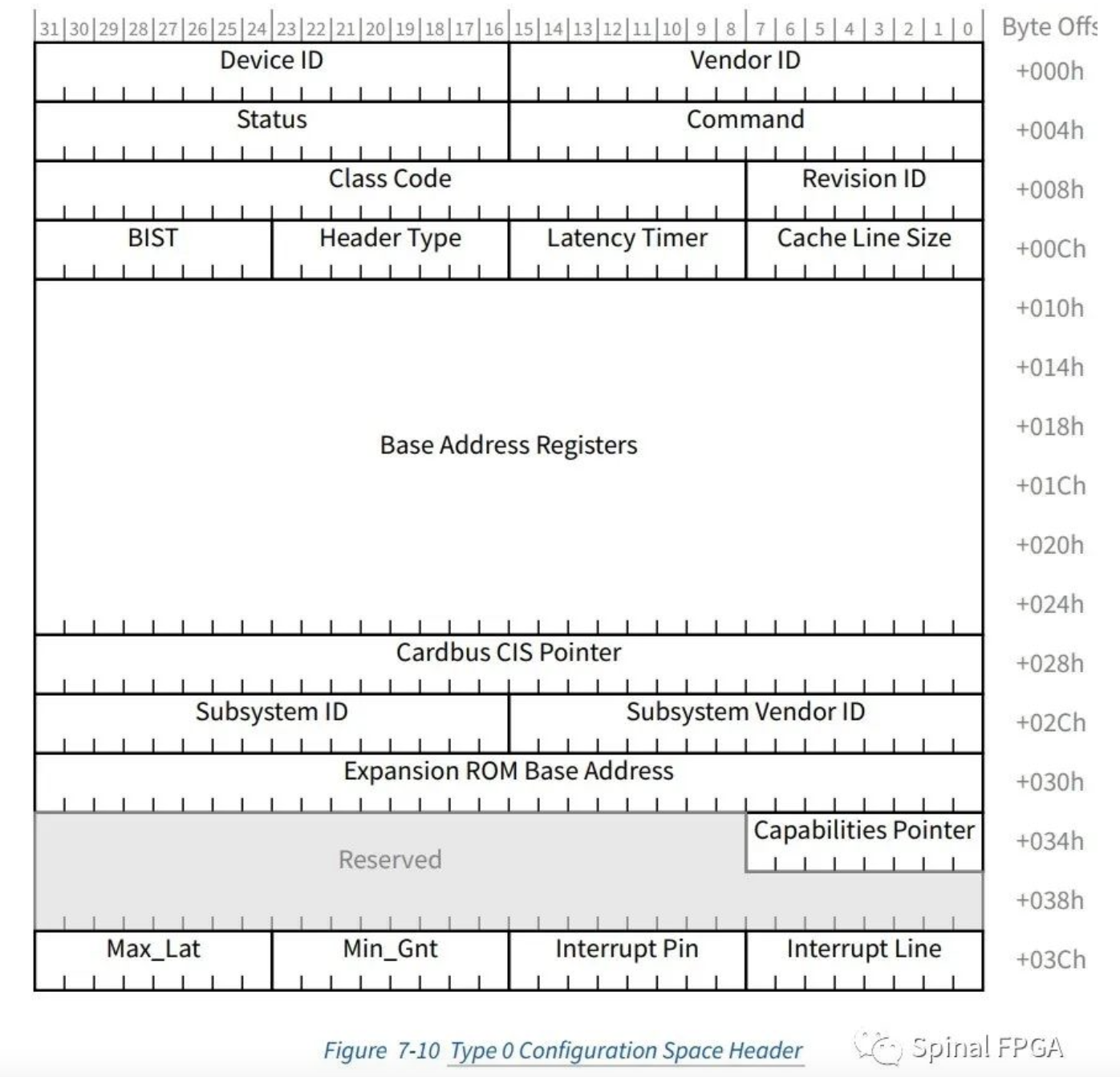

早前这东西不假思索,抄抄之前的设计照着配置就好了。乍看pcieext-cocotb中的实现,不禁思索,这些参数软件是如何识别的呢?像下面EP常涉及的配置空间:

配置空间中所涉及到的只有6个Base Address Registers,似乎并无很明显的指示~

》协议解读

先来看看Spec中关于Base Address Registers的定义:

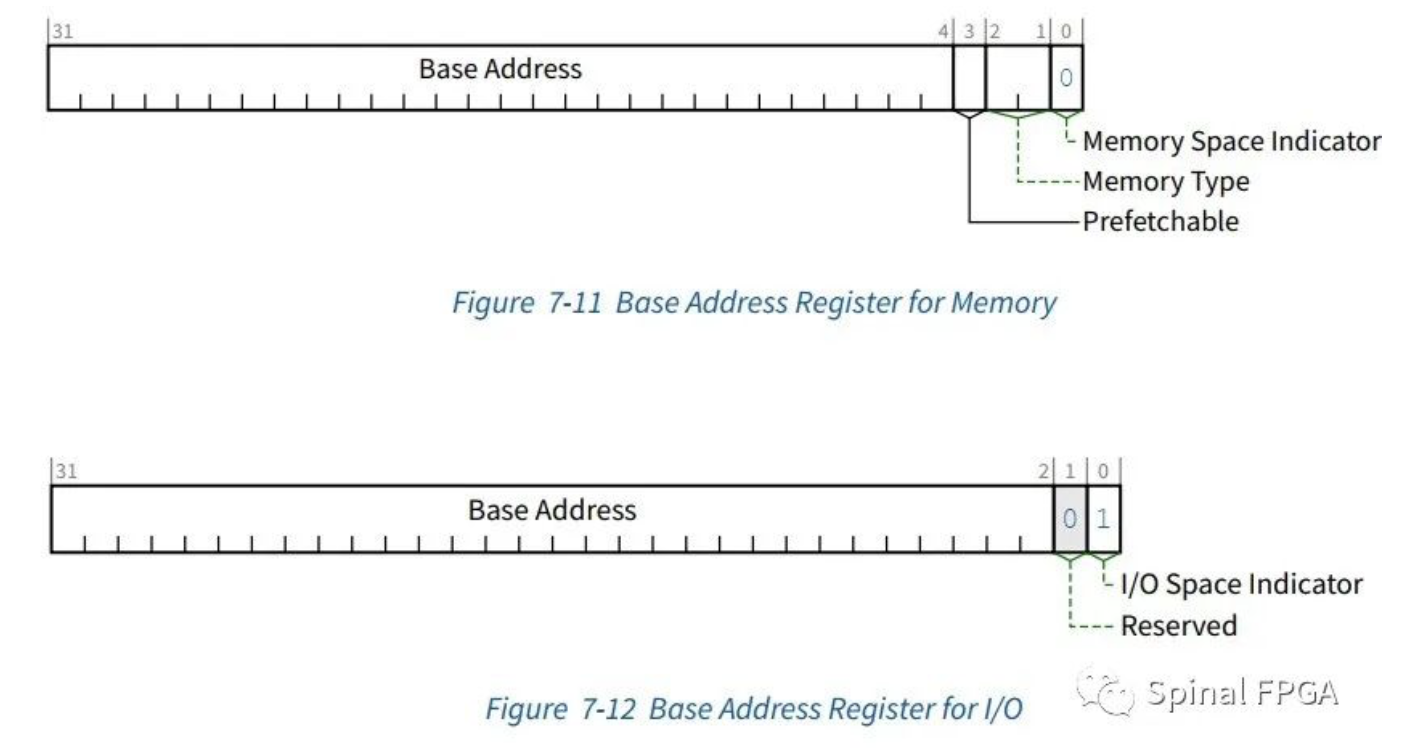

关于如何区分是Mem空间还是IO空间,Spec中定义了:

bit0:为1表示Memory Space,为0则表示I/O Space。

(I/O空间仅支持32位,且现在PCIe设备里也较少使用,这里不再展开,感兴趣小伙伴可自行翻看Spec)

对于Memory类型空间,bit[3:0]均为只读。在bit[2:1]中定义了Memory类型空间

可见,当bit[2]为1时表示64位地址空间,否则为32位地址空间。

而当bit[3]为1时,表示该Bar空间为Prefetchable,为0则不是非prefetchable。

看到这里,上面的疑问也基本可以解答了。在cocotbext-pcie中的配置方式也有所验证:

》Prefetchable

关于Prefetchable这个属性,一直也没有非常清晰的认识。按照Spec中的定义:

A Function is permitted to mark a range as prefetchable if there are no side effects on reads, the Function returns all bytes on reads regardless of the byte enables, and host bridges can merge processor writes into this range without causing errors.

Any device that has a range that behaves like normal memory should mark the range as prefetchable. A linear frame buffer in a graphics device is an example of a range that should be marked prefetchable.

一般而言,在PCIe设备里,Bar空间基本用于实现寄存器读写,是基本符合上面所描述的情况的,所以配置成prefetchable还是有必要的。而且在spec中,也提到了:

PCI Express adapters with Memory Space BARs that request a large amount of non-prefetchable Memory Space(e.g., over 64 MB) may cause shortages of that Space on certain scalable platforms, since many platforms support a total of only 1 GB or less of non-prefetchable Memory Space.This may limit the number of such adapters that

can be supported on those platforms. For this reason, it is especially encouraged for BARs requesting large amounts of Memory Space to have their Prefetchable bit Set, since prefetchable Memory Space is more bountiful on most scalable platforms.

On PCI Express systems that meet the criteria enumerated below, setting the Prefetchable bit in a candidate BAR will still permit correct operation even if the BAR’s range includes some locations that have read side-effects or cannot tolerate write merging. This is primarily due to the fact that PCI Express Memory Reads always contain an

explicit length, and PCI Express Switches never prefetch or do byte merging. Generally only 64-bit BARs are good candidates, since only Legacy Endpoints are permitted to set the Prefetchable bit in 32-bit BARs, and most scalable platforms map all 32-bit Memory BARs into non-prefetchable Memory Space regardless of the Prefetchable bit value.

这里贴上Spec中的原话,总结起来:尽可能配置成64 bit prefetchable.

》Bar空间的初始化

对于Bar空间,其核心除了上述的属性检测外另一重点便是为Bar空间分配指定大小的地址空间。

对于Base Address Registers,Bar空间的大小只能配置成2的n次方。以32位Memory 空间为例,其可配置的范围是16Byte~2GB(低四bit用于设置Bar空间属性)。对于指定大小所占用的位,其只读并且始终为0,若没有被使用,则其会返回全0。在初始化时软件可以向Bar空间写全1然后回读。对于读会的数据,将低4bit清零,然后所有bit取反后加1即为对应的Bar空间大小。分配好地址空间好将Base地址写回到Base Address Registers中~

-

NVMe高速传输之摆脱XDMA设计之八:PCIe初始化状态机设计2025-07-05 1012

-

PCIE的BAR空间介绍2024-04-22 7319

-

6678通过pcie进行boot时,PC无法写bar空间2024-03-28 17911

-

体验紫光PCIE之使用WinDriver驱动紫光PCIE2023-11-17 1847

-

PCIe相关问题解答2023-09-15 3278

-

PCIe—Bar空间是怎么生效的2023-06-05 8301

-

IMX8 PCIE BAR 15没有空间是怎么回事?2023-04-11 737

-

如何解决PCIe采集卡在3588J开发板无法进行大容量高端BAR Memory空间分配的问题2022-10-20 2609

-

关于PCI9054在BAR3空间读取SDRAM数据地址需要*4的问题2021-05-14 3799

-

如何使用AXI-PCIe桥接IP与我的逻辑进行通信2020-06-19 3884

-

C6678,PCIe,BAR的地址范围2018-06-21 4253

-

关于PCIE中BAR配置的问题。2018-06-19 5864

-

求教:关于DM8168的PCIe寄存器2018-05-28 2292

全部0条评论

快来发表一下你的评论吧 !