晶振DLD2值过高的原因

描述

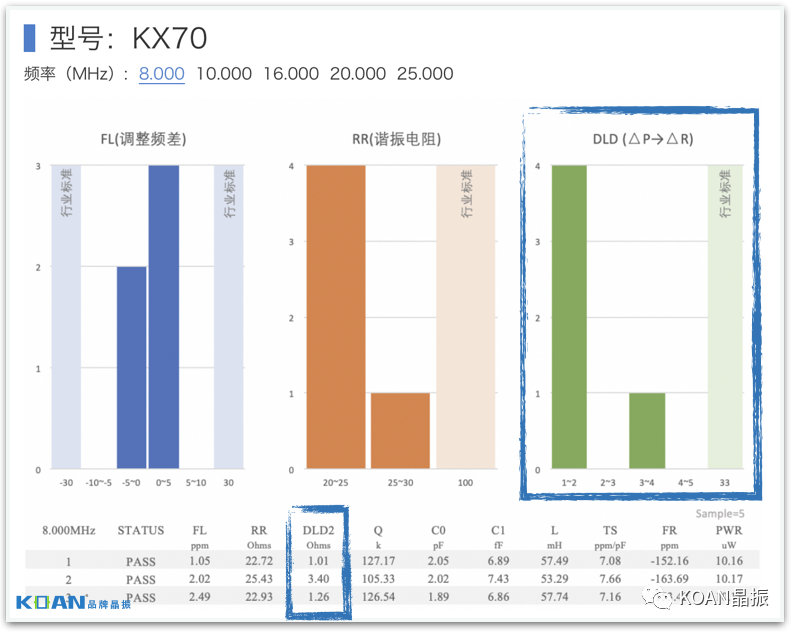

激励功率的变化会引起晶体频率和谐振阻抗的变化,S&A250B测试数据中的DLD2指的是:不同激励电平下的负载谐振电阻的最大值与最小值的差值,值越小越好。

激励电平相关性

DLD: Drive Level Dependency

晶振DLD2值过大,会怎么样?

如果激励功率过大可能破坏晶体的内部机理,引起振荡频率异常、稳定度下降、频率失真、晶片破损等现象,更为严重的导致电极受损。

在电路设计时,KOAN小妹建议您确认所使用的激励等级绝对不超过最大激励等级。如果激励功率过低,也会带来DLD问题或者不起振。

DLD2值过高的原因

除电路设计的因素,晶振制作过程中残留应力和制造污染也会造成DLD2值高。《晶振的制作过程》中,第七步“晶振焊封”中:无源谐振器真空密封/充氮气;有源晶振还需要加入芯片,用金线与底座各引脚连接,最后用真空密封/充氮气。

在没有真空的情况下,晶振内部存有少量水蒸气,在低温环境下会凝结成水滴附着于晶片表面。晶振内部充氮气优于仅抽真空。氮气是防止内部金属氧化,例如电极等,以进一步提升晶振的稳定性。

晶振的设计关键:频率稳定

晶振频率稳定是振荡电路设计的关键点。振荡电路设计中需要考虑的6大因素:

01 选用公差和谐振阻抗较小的晶体

02 选择合适的激励功率

03 合适的匹配电容(满足相位条件)

04 振荡宽限(满足振幅条件)

05 选用合适的振荡IC

06 其它因素:电路,环境……

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

晶振起振_单片机晶振不起振原因及解决方法2018-01-12 10892

-

单片机晶振不起振的40个原因分析2018-10-12 44402

-

32.768KHZ晶振不起振原因有哪些?2022-04-22 5506

-

晶振不起振的原因是什么?这些解决办法要知道!2023-09-13 3494

-

晶振停振的原因及解决方法2023-10-31 3537

-

晶振频偏过大的原因及解决方案2023-11-17 4324

-

晶振引脚氧化的原因及解决办法2023-12-18 1649

-

10个晶振不起振的原因分析2024-06-13 2536

-

晶振DLD参数是什么?2024-07-26 3581

-

晶振不起振的常见原因2025-03-31 1642

全部0条评论

快来发表一下你的评论吧 !