采样技术对信噪比的提升方法

电子说

描述

基本原理

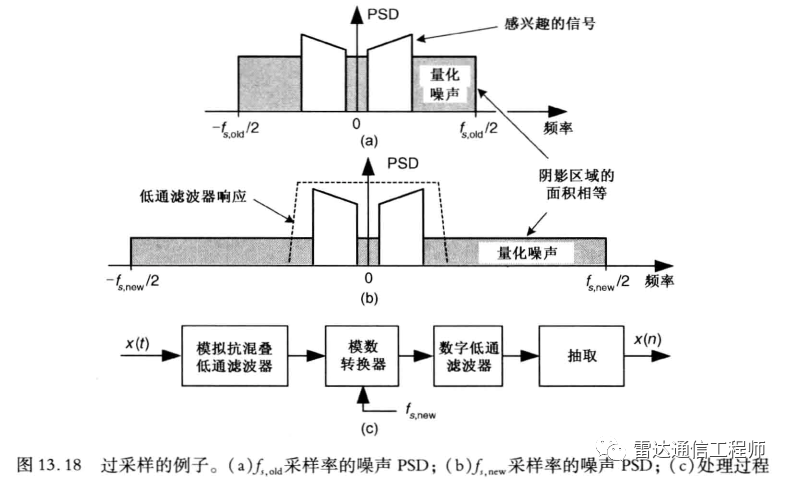

如上图所示,过采样提升信噪比的基本原理:对于确定的ADC芯片,其采样的量化噪声为固定常数,其均匀的分布在Fs/2带宽的奈奎斯特区间内,当采样率Fs增加时,等量的量化噪声将分布在更换的内奎斯特区间内,噪声谱密度降低(上图中阴影区域被压扁,但面积不变),即同样信号带宽内包含的噪声降低,理论上采样率每提高一倍,噪声功率谱密度就降低3dB。

利用该原理而得到的信噪比提升值称为“处理增益”,因此提高采样率可以在特定信号带宽内提高ADC的有效位ENOB,Fs每增加4倍,有效位增加1bit。有专门利用这个原理制造的ADC芯片,即sigma-delta型ADC,其通过很低的实际ADC分辨率(比如2bit)进行超高过采样(比如1024倍)后再滤波抽取,就能在得到10bit的分辨率,因此很多测量精密直流信号的ADC就适合用这种类型,要求的数据刷新速率较低,如用于测量温度、压力这种缓变的24bit、32bit ADC几乎(应该说全部)都是这种。

sigma-delta型ADC除了利用过采样外,还利用特殊的噪声整形技术,将关注的带内噪声大部分转移到带外,然后再用数字滤波器滤除,如此即可在前面常规过采样的基础上进一步降低目标带宽的噪声量;噪声整形的形状大概有两种,一种是针对中频数字接收(如ADI的某些中频数字接收芯片),有的称作“浴盆状”,一种是针对以直流为起点的低通应用,如上面提到的用于近直流测量的24、32bit ADC,重点、重点、重点来了,ADI的射频收发器如AD9361、71,ADRV9009等的接收通道ADC都属于sigma-delta型ADC;

注:以上3图来源自ADI文献

案列描述

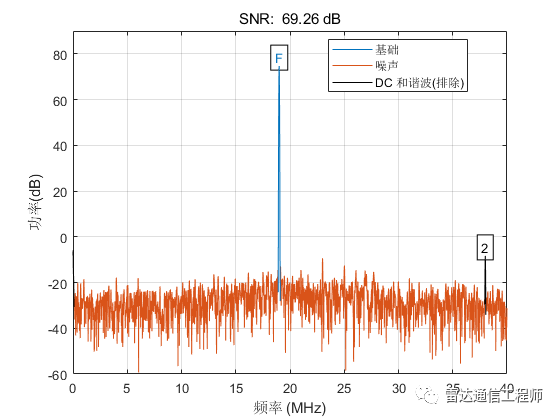

案列描述:使用信号源给ADC输入一个-1dBFS的61MHz正弦信号,其中ADC采样率80MHz,信号经过DDC数字下变频、CIC滤波4抽取、两级FIR滤波2抽取最终得到5Mbps速率的基带IQ信号(带宽4MHz),通过Vivado的ILA核从FPGA同时抓取ADC原始数据、DDC结果、CIC结果、HB滤波结果、FIR滤波结果;然后将数据导入matlab绘制频谱和计算SNR;文中所有频谱不是matlab仿真而来,而是在FPGA中采集的实际信号频谱。

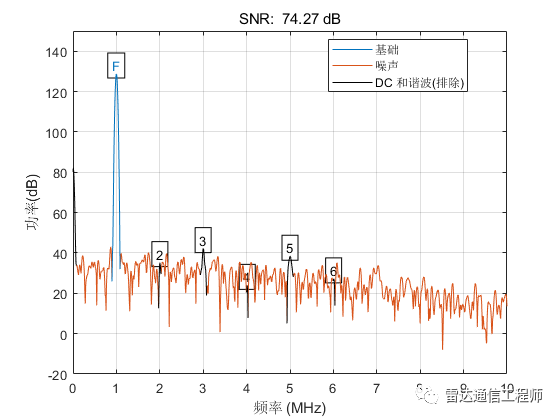

处理增益PG=Fs/(2BW)=80/(25)=8,即理想情况下SNR能够提升9dB(过采样处理增益),从图看出经过系列处理后SNR提高了8.3dB,后文中除了第一个图是原始实信号外,其余均为基带I路信号,最后输出信号的信噪比与理想条件下相差0.7dB,这0.7dB的差异主要就是滤波器不理想(过渡带)等因素所导致。

基本流程

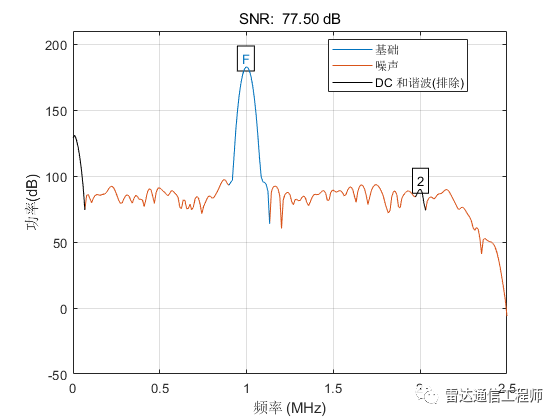

图1-ADC采样的原始数据频谱

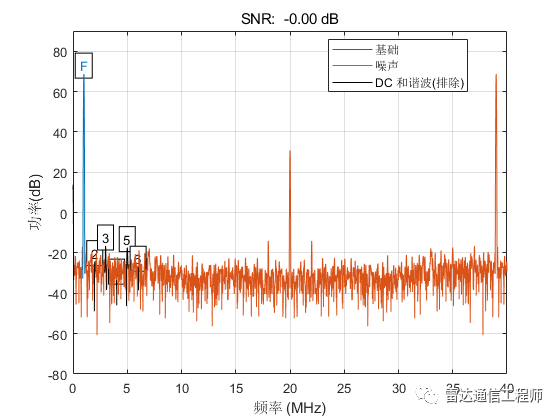

图2-DDC后的I路数据频谱

信号中有直流成分,导致DDC过程中NCO本振频率(20MHz)泄露

图3-CIC后的I路数据频谱

实际此处采用4倍CIC抽取其实有些问题,

图4-HB后的I路数据频谱

图5-末级FIR后的I路数据频谱

滤波器带宽设置为2MHz,故上图中可清晰见到2~2.5MHz处的滤波器过渡带滚降特性。

-

基于DSP和FPGA技术的低信噪比雷达信号检测2018-08-15 3048

-

利用DSP和FPGA技术的低信噪比雷达信号检测设计介绍2019-07-04 2018

-

如何利用DSP和FPGA技术检测低信噪比雷达信号?2019-08-05 2376

-

提升JavaEE技术的方法2020-12-17 1291

-

多带通信号采样的信噪比分析2009-02-27 1718

-

低信噪比下RFID调制识别方法的研究2010-10-15 702

-

什么是声卡采样/信噪比2010-02-05 772

-

过采样法提高A_D分辨率和信噪比2012-03-19 1038

-

信噪比估计方法研究2013-04-27 754

-

基于fpga的过采样技术设计2018-12-19 3362

-

浅谈ADC过采样提高信噪比2022-03-07 8623

-

过采样:提高ADC信噪比巧妙方法2023-06-02 5383

-

CDMA系统中的信噪比优化与增强技术2023-06-20 2194

-

如何提高信噪比的有效方法2024-12-10 9499

-

如何提升科研级CCD相机成像信噪比?2025-06-09 1385

全部0条评论

快来发表一下你的评论吧 !