浅谈FPGA芯片架构

描述

引言

FPGA 芯片架构是非常重要的,如果你不了解 FPGA 芯片内部的详细架构,那么:

- 你便对于你自己的设计一无所知,

- 你将不懂如何去实现资源的优化,

- 你也不懂如何合理调用内部模块,

- 你更不懂如何去权衡速度与面积,

- 那么你的 HDL 语言就跟 C 一样...

- 所以,我们必须了解一下其架构:

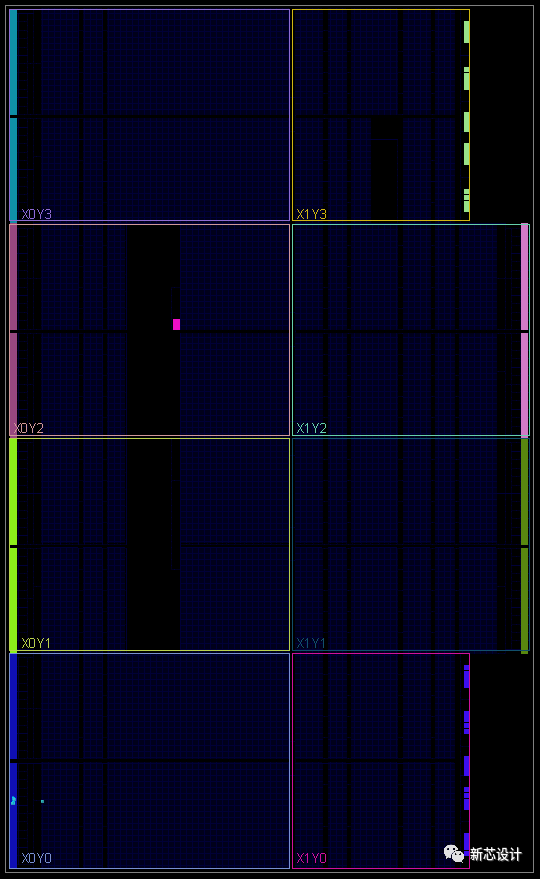

如下所示,这是部件号 Part 为 XC7A100TFGG484-2 的 FPGA 芯片内部的整体架构(基于 Xilinx Vivado 的观测角度),在这里,按照不同的时钟域划分的话(时钟域,顾名思义就是不同频率不同相位的时钟所划分的不同区域模块),通常根据不同的工艺、器件速度及其对应的时钟进行划分,如划分为 8 个区域;按照不同的资源类型划分的话,就是按照不同的资源部件的不同功能进行划分,如划分成 10 种资源;按照不同的模块划分的话,FPGA 芯片架构可以划分为 6 大模块。

Xilinx FPGA 芯片架构

一、输入输出块(IOB)(Input Output Block)

为了便于管理和适应多种电气标准,FPGA 的 IOB 被划分为若干个组(Bank),每个 Bank 的接口标准由其接口电压 VCCO 决定;一个 Bank 只能有一种 VCCO,而不同 Bank 的 VCCO 可以不同;只有相同电气标准和物理特性的端口才能连接在一起,VCCO 电压相同是接口标准的基本条件。

IOB 为芯片内部逻辑和芯片外部输入和输出信号提供接口,可编程为输入、输出和双向 IO 三种方式。(通过 RTL 代码中信号的定义和引脚的约束即可实现)

二、可配置逻辑块(CLB)(Configurable Logic Block)

在 Xilinx 公司的 FPGA 器件中,一个 CLB 由 2 个或 4 个相同的 Slice 和附加逻辑组成。Slice 是 FPGA 的基本逻辑单元,Slice 又分为 SLICEL(Logic)和 SLICEM(Memory)。

SLICEL 和 SLICEM 内部都各自包含了 4 个 6 输入查找表(LUT6)、3 个数据选择器(Mux)、1 个进位链(Carry Chain)和 8 个寄存器(Register)。查找表和数据选择器完成组合逻辑功能,寄存器(可配置成触发器或锁存器)完成时序逻辑功能。

- 查找表:6 输入查找表类似于一个容量(深度)为 64 的 ROM(2^6 = 64)(工艺上是珍贵的 SRAM 资源,哎,这就是 FPGA 通常不会出现在量产的手机行业里的原因,就是太昂贵了)。6 输入表示输入地址位宽为 6 bits,更通俗地讲就是地址线有 6 根;对于查找表,目前主流 FPGA 都采用了基于 SRAM 工艺的查找表(LUT)(Look Up Table)结构,所以 LUT 本质上就是一个 RAM。当用户通过原理图或 HDL 语言描述了一个逻辑电路以后,FPGA 开发软件会自动计算逻辑电路的所有可能结果,列成一个真值表的形式,并把真值表(即输入对应的输出逻辑)事先写入 RAM(写入 RAM 的过程即为 Bitstream 配置的过程,数据的载入),这样,每输入一个信号进行逻辑运算就等价于输入一个地址进行查表(软件中称为索引),找出地址对应的内容,然后输出即可(思考一下,单片机的程序计数器 PC 的取值不也是这样的吗,CPU 的程序数据指令的载入不也是这样的吗)。

- 数据选择器:数据选择器一般在 FPGA 配置后就固定下来了。

- 进位链:超前进位加法器,更快的加法器的实现。

- 寄存器:可以配置成多种工作方式,比如 FF 或 Latch、同步复位或异步复位、复位高电平有效或低电平有效等等。SLICEM 的结构与 SLICEL 的结构类似,最大的区别是使用了一个新的单元代替 SLICE 中的查找表,这个新的单元可以配置为 LUT、RAM、ROM 或移位寄存器(SRL16 或 SRL32),从而可以实现 LUT 的逻辑功能,也能做存储单元(多个单元组合起来可以提供更大的容量)和移位寄存器(提供延迟等功能)。

其中,SLICEM 中 LUT 的输入端读地址和写地址为 8 位,高两位可能是将 4 个 LUT 并联一起作为一个大的 RAM 或 ROM 时用,同时 SLICEL 和 SLICEM 的 LUT 均可设为 5 位或 6 位查找表。

三、嵌入式块 RAM(BRAM)(Block RAM)

BRAM 可被配置为 ROM、RAM、FIFO 等常用的存储模块。区别于分布式 RAM(Distributed RAM),DRAM 主要由 LUT 组成的,而不占用 BRAM 的资源,分布式 RAM 也可以被配置为 ROM、RAM、FIFO 等常用的存储模块,但是性能不如 BRAM,毕竟 BRAM 才是专用的(在 IC 设计中,专用的才是性能较好的,例如 ASIC 就比 FPGA 性能好,GPU 就比 CPU 跑得快,但是,太专一的缺点就是不够灵活哈哈)。所以,在 BRAM 资源不够用的情况下,才使用分布式 RAM,或者是不追求性能的情况下。

BRAM 由一定数量固定大小的存储块构成的,使用 BRAM 资源不占用额外的逻辑资源,并且速度快性能高。然而,使用的时候消耗的 BRAM 资源只能是其块大小的整数倍,当你调用了 BRAM,就算你只存了一个比特也要占用一个 BRAM。 一个 BRAM 的大小为 36K Bits,可以分成两个小的 RAMB18 各自为 18K Bits,以及一个大的 RAMBFIFO36 为 36K Bits,例如,总共有 135 个 BRAM,又可以分为 135 个 RAMB36 或 270 个 RAMB18。

在 FIFO 例化的时候可以将 BRAM 设置为 FIFO 时,不会使用额外的 CLB 资源,并且这部分 RAM 是真双口 RAM。

FPGA 所采用的逻辑单元阵列 LCA(Logic Cell Array)的内部主要包括可配置逻辑块 CLB(Configurable Logic Block)、 输入输出块 IOB(Input Output Block)和内部互连线(Interconnect)三个部分;前面两种已经介绍完毕,接下来介绍第三种。

四、互连线资源(Interconnect)

布线资源连通着 FPGA 内部的所有单元,而连线的长度和工艺决定着信号在连线上的驱动能力和传输速度。FPGA 芯片内部有着丰富的布线资源,根据工艺、长度、宽度和分布位置的不同而划分为 4 类不同的类别:

- 第一类是全局布线资源,用于芯片内部全局时钟和全局复位的布线;

- 第二类是长线资源,用于完成芯片 Bank 间的高速信号和第二全局时钟(局部时钟)信号的布线;

- 第三类是短线资源,用于完成基本逻辑单元之间逻辑互连的布线;

- 第四类是分布式布线资源,用于专有时钟、专有复位、控制信号的布线。

想要详细了解布局布线 Place & Route 的话,可以参考文章《数字 IC 笔试面试必考点(3)数字 IC 前端设计 + 后端实现》

五、内嵌功能单元

内嵌功能单元主要指 DLL(Delay Locked Loop)、PLL(Phase Locked Loop)、DSP(Digital System Processing)(数字信号处理)、DCM(Digital Clock Manager)(提供数字时钟管理和相位环路锁定)、和 CPU(Central Processing Unit)软处理核(比如 MicroBlaze 的软核)。

DLL 和 PLL 具有类似的功能,可以完成时钟高精度、低抖动的倍频和分频,以及占空比调整和相移功能。Xilinx 公司生产的芯片上集成了 DCM 和 DLL,Altera 公司生产的芯片上集成了 PLL。PLL 和 DLL 可以通过 IP 核生成的方式进行管理和配置。

DCM 是 FPGA 内部处理时钟的重要器件,他的作用主要有三个:消除时钟偏差(Clock De-Skew)、频率合成(Frequency Synthesis)和相位调整(Phase Shifting);DCM 的核心器件是延时锁相环 DLL 和锁相环 PLL,它是由一串固定时延的延时器组成,每一个延时器的时延约为 30 皮秒,也就是说,DCM 所进行的倍频、分频、调相的精度为 30 皮秒(DLL 由数字电路实现,PLL 由数模混合电路实现)。

对于时钟,我们最好不要将两个时钟通过一个与门或者或门操作(等等的一些逻辑操作),这样的话就很可能会产生毛刺,影响系统稳定性,如果要对时钟进行操作,例如切换时钟等,可以使用 FPGA 内部的专用器件 BUFGMUX(原语 Primitives)。

现在越来越丰富的底层内嵌功能单元,使得单片 FPGA 成为了系统级的设计工具,具备了软硬件联合设计的能力,逐步向 SoC 平台过渡。

六、内嵌专用硬核

内嵌专用硬核是相对底层嵌入的软核而言的,指的是 FPGA 处理能力强大的硬核(比如 ARM Cortex-A9 的硬核),等效于 ASIC 电路。为了提高 FPGA 性能,芯片生产商在芯片内部集成了一些专用的硬核。例如,主流的 FPGA 中都集成了专用的 DSP 乘法器,用于提高 FPGA 乘法器的速度;而为了适用通信总线与接口标准,很多高端的 FPGA 内部都集成了串并收发器(Serdes),例如 FMC,可以达到数十 Gbps 的收发速度呢。

-

FPGA内部详细架构解析2022-10-20 2860

-

FPGA架构演进之路 FPGA架构设计原则和实现挑战2023-08-11 3375

-

FPGA架构和应用基础知识2018-12-14 2927

-

浅谈FPGA在安全产品中有哪些应用?2021-05-08 2229

-

FPGA各芯片架构特点2021-07-26 1246

-

FPGA芯片整体架构2021-07-29 1721

-

FPGA 内部详细架构 精选资料分享2021-07-30 1691

-

XILINX FPGA 芯片整体架构是如何构成的2021-10-29 3490

-

FPGA芯片的整体架构是由哪些部分组成的2021-11-05 2015

-

浅谈三层架构原理2022-01-16 7995

-

FPGA设计工具浅谈2009-10-10 681

-

浅谈数字总线的时钟架构2017-01-17 800

-

浅谈区域车辆架构中音频和无线电处理2022-09-20 1451

-

芯片行业之浅谈FPGA芯片2023-02-08 5564

-

fpga芯片架构介绍2024-03-15 1809

全部0条评论

快来发表一下你的评论吧 !